Fターム[5B042HH03]の内容

デバッグ、監視 (27,428) | プログラムデバッグ、プログラムテスト (3,778) | デバッグ用装置、デバッグプログラム (789) | 着脱自在なデバッグ装置 (110)

Fターム[5B042HH03]に分類される特許

1 - 20 / 110

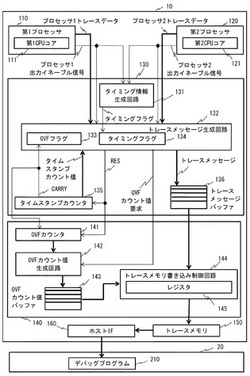

インサーキットエミュレータ、トレースメモリ制御装置、トレースメッセージ生成装置及びトレースメッセージ処理方法

【課題】トレース対象の命令の実行が同時に生じた場合に、正確な命令発生タイミングを把握すること

【解決手段】タイミング情報生成回路131は、第1CPUコア111、第2CPUコア121の各々からのトレースデータの出力と同期して出力されるプロセッサ1(2)出力イネーブル信号に基づき、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報を出力する。トレースメッセージ生成回路132は、各トレースデータと、各トレースデータ取得時のタイムスタンプと、タイミング情報と、を対応付けたトレースメッセージを生成する。トレースメモリ書き込み制御回路144は、トレースメッセージ生成回路132が生成したトレースメッセージをトレースメモリ150に書き込む。

(もっと読む)

バリアトランザクションのデバッグ

【課題】集積回路をデバッグするための技術を提供する。

【解決手段】集積回路2は、相互接続回路20を介してデータトランザクションを発行するための、1つ以上のトランザクションマスター8、10、12、4を含む。デバッグアクセスポート回路は、デバッグコントローラ6から受信されるデバッグコマンドに応答して、相互接続回路に発行されるバリアトランザクションを発生させるように構成される。相互接続回路は、データトランザクションの少なくともいくつかの相対的順序付けを、それらが相互接続回路を通過する時に抑制することによって、受信したバリアトランザクションに応答する。

(もっと読む)

デバッグ装置およびデバッグ方法

【課題】デバッグのための事前準備を簡略化してデバッグ作業の効率を向上させること。

【解決手段】デバッグ装置は、デバッグコマンドを埋め込んだプログラムを実行し、デバッグコマンドによりプログラムの実行を中断する場合には、デバッグコマンドを示す第1の情報およびプログラムの中断を示す第2の情報を出力するエミュレータと、第2の情報を受けると、第1の情報が示すデバッグコマンドをエミュレータから読み出して、読み出したデバッグコマンドを実行し、実行結果を戻り値としてエミュレータに出力するとともに、プログラムの実行を再開するようにエミュレータに指示するデバッガと、を備える。

(もっと読む)

エミュレータ及びデバッグ方法

【課題】JTAG-ICEにおいて、LSIの入出力状態をトリガとするエミュレーションのブレークを実現する「エミュレータ及びデバッグ方法」を提供する。

【解決手段】エミュレーション処理部23は、LSI31のICE制御ブロック314に命令を発行し、所定のプログラムをコアロジック311に実行させ、スキャン処理部24は、LSI31のコアロジック311のプログラムの1ステップ実行毎のスキャン動作を、LSI31のバウンダリスキャン制御ブロック315に行わせ、LSI31の各入出力端子312の状態をスキャンデータメモリ25に格納する。エミュレーション処理部23は、スキャンデータメモリ25からLSI31の各入出力端子312の状態を読み出し、読み出した各入出力端子312の状態が、予めブレーク条件メモリ26に設定されているブレーク条件にマッチするかどうかを調べ、マッチしていればプログラムの実行をブレークする。

(もっと読む)

半導体集積回路

【課題】半導体集積回路に接続されたCPUのユーザーランド上のアプリケーションから半導体集積回路に特化したデバイスドライバを書くことなく容易に制御し得る半導体集積回路を提供する。

【解決手段】半導体集積回路としてのASIC20は、CPU11と接続し得る高速シリアルインタフェース30Bを備えていると共に、通常のUARTモジュール23と同等のレジスタ仕様を有し、CPU側からデータ送受信のためのレジスタアクセスを行うと、そのレジスタアクセスをデバッグコマンドとみなして、ローカルバス21へのレジスタアクセスを行うダミーデバッグシリアルモジュール22を備えた。

(もっと読む)

半導体集積回路及び半導体集積回路のバス制御方法

【課題】ROMエミュレータによるプログラムのデバッグでは、専用のコネクタをCPUが実装された基板に設ける必要ある。このコネクタを追加することにより、配線抵抗が上昇し、メモリのアクセスタイミングを悪化させる。そこで、メモリ間のアクセスタイミングに影響を与えずに、プログラムのデバッグを実現する半導体集積回路を提供する。

【解決手段】半導体集積回路は、メモリに対するアクセスを制御するメモリコントローラと、メモリコントローラの端子と外部端子の間に配置されるバウンダリスキャン回路と、バウンダリスキャン回路の動作モードを決定するモード信号の出力が可能なJTAGインターフェイスと、プログラムのデバッグ時に、モード信号に基づいて、メモリコントローラのリードアクセスを許可する制御信号を、バウンダリスキャン回路を介して、メモリコントローラに発行するタイミング制御回路と、を備える。

(もっと読む)

デバッグ対象装置、デバッグ情報出力システム、デバッグ情報出力方法およびデバッグ情報出力プログラム

【課題】テキストデータに限定されない表現形態でデバッグ情報を取り扱うことのできるデバッグ対象装置、デバッグ情報出力システム、デバッグ情報出力方法およびデバッグ情報出力プログラムを得ること。

【解決手段】デバッグ出力データ作成手段11の作成したデバッグ出力データは、送信情報形式判別手段12によってデータの形式(テキスト、画像、音等)が判別され、データ量判別手段13で送信するデータ量が判別される。通信方式判別手段14はこれらの判別結果を用いて通信方式を判別しデバッグ出力データ送信手段15でモニタ側に送信する。

(もっと読む)

インサーキットエミュレータ

【課題】エミュレーション時に、プログラム実行を停止させることなくレジスタ情報を外部に読み出し、且つ、エミュレーション対象と同じプログラム動作を実現すること。

【解決手段】インサーキットエミュレータは、プログラムを実行するプロセッサをエミュレートするメインプロセッサと、周辺機能をエミュレートする第1、第2周辺プロセッサと、外部と通信可能なエミュレーション制御回路と、アクセス制御回路と、を備える。第1周辺プロセッサは、メインプロセッサによってアクセスされる第1周辺レジスタを備え、第2周辺プロセッサは、第1周辺レジスタと内容が同期した第2周辺レジスタを備える。アクセス制御回路は、エミュレーション制御回路によって発行される読み出し要求に応答して、バイパス処理を実行する。そのバイパス処理において、アクセス制御回路は、第2周辺レジスタからデータを読み出し、当該読み出しデータをメインプロセッサを介することなくエミュレーション制御回路に出力する。

(もっと読む)

デバッグを実行可能にするデバイス及び方法

【課題】デバイスが低電力モードから通常モードに復帰するときに、重要なデバッグ情報が失われてしまうことを防止する。

【解決手段】デバイス100が低電力モードから出る場合、電力管理モジュール(PMM)155は、コア論理部135が処理を再開することを、デバッグ素子140が各自の前の状態に再構築されるまで禁止する。PMM155はコア論理部135をリセット状態に保持する或いはコア論理部135に電力供給をしないようにする。デバッグ素子140の再構築は接続されたデバッガにより開始され、デバイス100の中で1つ以上の制御及びステータス(CS)レジスタ150の値を設定することができる。CSレジスタ150の値は、PMM155がコア論理部135の処理再開を何時禁止するか、及びデバイス100が低電力モードから復帰した後にPMM155が処理を何時再開できるようにするか等を決定する。

(もっと読む)

半導体装置

【課題】デバッグ端子部を介してのリバースエンジニアリングを防止できるようにする。

【解決手段】デバッグ端子部制御回路3は、CPU4で実行されたデバッグ用プログラムP1の中から有効化ルーチンR1を抽出し、該抽出した有効化ルーチンR1に基づいて、デバッグ端子部2で受信されるデバッグ入力信号S4をCPU4に入力するようにデバッグ端子部2を制御する。これにより、外部メモリ7aにデバッグ用プログラムP1が記憶されているときには、デバッグ端子部2が有効になってデバッグ入力信号S4がCPU4

に入力されるが、外部メモリ7aにデバッグ用プログラムP1が記憶されていないときには、デバッグ端子部2が無効になってデバッグ入力信号S4がCPU4に入力されない。この結果、出荷時にデバッグ端子部2を無効化することにより、デバッグ端子部2を介してのリバースエンジニアリングを防止できる。

(もっと読む)

電子機器およびテレビジョン

【課題】機器に必要な機能の維持と小型化、低コスト化とを両立させる。

【解決手段】制御部は、外部から音声信号を入力するための音声入力ポートと、デバッグのための通信処理に用いられるデバッグ通信用ポートとを有し、機器側接続端子は、信号線を介して音声入力ポートとデバッグ通信用ポートとのそれぞれと接続しており、制御部は、機器側接続端子に外部側接続端子が接続されたと判定した場合に、信号線における信号を検出することにより音声入力のための外部側接続端子が接続されたか上記通信処理のための外部側接続端子が接続されたかを判定し、音声入力のための外部側接続端子が接続されたと判定した場合には機器側接続端子および音声入力ポートを介して音声入力を受け、上記通信処理のための外部側接続端子が接続されたと判定した場合には機器側接続端子およびデバッグ通信用ポートを介して上記通信処理を実行する構成とした。

(もっと読む)

プログラム評価装置

【課題】 組み込みシステムの開発において既存機能の流用をより容易に行うための技術を提供する。

【解決手段】 プログラム評価装置は、演算部と、複数の記憶媒体インタフェースとを備える。演算部は、RTOSにより複数種類のタスクの実行を管理するとともに、各々がタスク単位でモジュール化されたコンパイル処理後のバイナリデータである複数種類のオブジェクトモジュールを取得する。複数の記憶媒体インタフェースは、オブジェクトモジュールを格納した記憶媒体をそれぞれ物理的に着脱可能である。また、演算部は、複数種類のオブジェクトモジュールを、別々の記憶媒体からそれぞれ独立して取得する。

(もっと読む)

半導体集積回路、半導体集積回路の動作方法およびデバッグシステム

【課題】 デバッグに必要な半導体集積回路の外部端子数を少なくし、デバッグ機能を含む半導体集積回路のチップサイズを小さくする。

【解決手段】 電流計測部は、プロセッサを有する回路ブロックを含む複数の回路ブロックでそれぞれ消費される電源電流を計測し、電源電流値として出力する。選択部は、電源電流値の少なくともいずれかを選択情報に応じて選択する。トレースバッファは、選択部で選択される電源電流値をプロセッサの実行情報とともに順に保持し、保持している情報を順に出力する。デバッグに必要な回路ブロックの電源電流値を選択情報に応じて選択することで、プロセッサの実行履歴情報とともに保持される情報量を最小限にできる。これにより、トレースバッファから出力される情報のビット数を最小限にでき、電源電流値のトレースを含むデバッグに必要な半導体集積回路の外部端子数を少なくできる。

(もっと読む)

試験方法、試験装置、およびプログラム

【課題】予め準備した試験項目から何通りもの試験を可能とする技術を提供する。

【解決手段】試験装置1は、コマンド要素21およびデータ要素22からなる、被試験機の操作に係るコマンドブロック20が複数記述されたサンプルシナリオ2の入力を受け付け、このサンプルシナリオ2に対して、記述順入替え処理、コマンドブロック挿入処理、コマンドブロック置換処理、コマンド要素入替え処理、およびスルー処理のうちの少なくとも一つを実施して、複数のコマンドブロック20が試験順に記述された試験シナリオ5を生成する。また、試験シナリオ5に記述されているコマンドブロック20各々を、この試験シナリオ5での記述順に従って、デフォルト速度送信モード、ランダム速度送信モード、ポーズ挿入送信モード、および速度可変送信モードのいずれかにより、被試験機に送信する。

(もっと読む)

情報処理装置、デバッグ装置、デバッグ方法

【課題】デバッグ機能のパフォーマンスを最適に保つように、通信内容に適合する通信速度で通信不整合を起こすことなくデータを送受することができる。

【解決手段】CPU部(201、202)は、第1クロック(SCLK)に基づいてデバッグ対象となるプログラムを実行する。その第1クロック(SCLK)は、CPU部(201、202)の指示に基づいてクロック速度を変更される。外部ツール装置(501、502)は、デバッグを行うユーザーに対するマンマシンインタフェースを有する。第1送信部(401、402)は、第1クロック(SCLK)に基づいてデバッグデータを外部ツール装置(501、502)へ送信する。第2送信部(405)は、第1クロック(SCLK)と異なる第2クロック(DCLK)に基づいてデバッグデータを外部ツール装置(501、502)へ送信する。受信部(301、302)は、外部ツール装置(501、502)から送信されるデータを受信する。

(もっと読む)

集積回路装置及びその制御方法、並びにデバッグシステム及びその制御方法

【課題】全端子をエミュレーションすることができる集積回路装置及びその制御方法、並びにデバッグシステム及びその制御方法を提供する。

【解決手段】デバッグシステムは、オンチップデバックが可能なマイコン400を搭載したターゲットシステム300とオンチップデバッグエミュレータ200とを有する。マイコン400は、CPU411と、デバッグモード時にデバッグ端子として機能すると共に、ユーザモード時にはユーザ端子として機能するDEBUG/USER端子407と、デバッグモードの際にデバック機能を制御するデバッグ機能制御部402と、ユーザモードの際にポート機能を制御する汎用出力ポート401と、モードに応じて端子407をデバッグ機能制御部402又は汎用出力ポート401のいずれかに接続するセレクタ403とを有する。CPU411は、現在のモードの検知結果に応じてセレクタを制御する。

(もっと読む)

半導体集積回路装置およびプログラムのデバッグ方法

【課題】プログラムデバッグの容易化又はプログラムデバッグの低コスト化を実現する。

【解決手段】同一構成となる複数のCPUブロック(CPUBK[0],CPUBK[1],…,CPUBK[n−1],CPUBK[n])500aを設け、モード設定レジスタ(MREG)210によってCPUBK[0],CPUBK[n−1]をプログラム実行用モードで動作させ、CPUBK[1],CPUBK[n]をデバッグ実行用モードで動作させる。CPUBK[0],CPUBK[n−1]からのデバッグ情報は、それぞれ、デバッグ情報記憶装置アクセスコントローラ(DIMAC)220を介して出力され、CPUBK[1],CPUBK[n]のDIMACを介して収集される。CPUBK[1],CPUBK[n]のDIMACは、リング接続に伴う通信径路を持ち、互いにデバッグ情報等の送受信が可能となっている。

(もっと読む)

インサーキットエミュレータ用アダプタおよびインサーキットエミュレータ

【課題】CPUコア用インサーキットエミュレータ(ICE)と、遊技機向け付加回路の機能をエミュレートするICE用アダプタとで構成されるICEにおいて、ブレーク中に、ICE用アダプタに搭載されている遊技機向け付加回路の内部状態を保存したまま、その付加回路内のメモリやレジスタからデータを読み出す

【解決手段】乱数回路11やウォッチドッグタイマ12のように状態遷移回路を含む回路では、CPUコア用ICE20がブレークされているとき、状態遷移回路の状態遷移を停止させる。受信用FIFO回路13のリードポインタのように、CPUコア用ICE20がレジスタやメモリの内容を読み出すと内部状態が変化する回路では、内部状態を保存したままレジスタやメモリの内容を読み出すことができる回路を付加する。

(もっと読む)

コンフィグレーション装置、コンフィグレーション方法及びコンフィグレーションプログラム

【課題】論理回路のコンフィグレーションを効率よく行うことが出来るコンフィグレーション装置を提供する。

【解決手段】FPGA部200に含まれる複数のFPGAの各々にテスト用の論理回路を構築するためのテスト用コンフィグレーションデータ111と、複数の正式用デバイスデータ112aとからなる正式用コンフィグレーションデータ112を保持するデータ保持部110と、複数のFPGAに論理回路を構築するコンフィグレーション制御部120と、テスト用デバイスデータにより電子回路が構築された複数のFPGA間の入出力特性を測定し、複数のテスト用デバイスデータから特定のデバイスデータを抽出するコンフィグレーション選択部130とを備え、コンフィグレーション制御部120が、抽出されたテスト用デバイスデータ111aに対応づけられた正式用デバイスデータ112aにより、複数のFPGAに論理回路を構築する。

(もっと読む)

デバッグ方法、デバッグ装置、及びトランスレータプログラム

【課題】暗号化されていないCPU用のデバッガを用いて、ターゲットCPU上で動作する暗号化された命令列を含むプログラムのデバッグを容易に行う。

【解決手段】暗号化された命令列を復号化して実行するターゲットCPU(208)と、デバッガ(202)とを含むデバッグ装置を用いてデバッグを行う。上記ターゲットCPUと上記デバッガとの間にトランスレータ(204)を介在する。上記トランスレータは、上記デバッガから伝達された通信内容を上記トランスレータで上記ターゲットCPUに対応する内容に変換し、上記ターゲットCPUから伝達された通信内容を上記トランスレータで上記デバッガに対応する内容に変換する。このような変換を行うことで、ターゲットCPU上で動作する暗号化された命令列を含むプログラムのデバッグの容易化を図る。

(もっと読む)

1 - 20 / 110

[ Back to top ]