Fターム[5B042JJ21]の内容

デバッグ、監視 (27,428) | 動作監視、異常又は誤りの検出 (3,508) | 異常又は誤りの検出方法 (1,125) | 時間を監視するもの (556) | ウォッチドッグタイマ (181)

Fターム[5B042JJ21]に分類される特許

1 - 20 / 181

生存監視システム

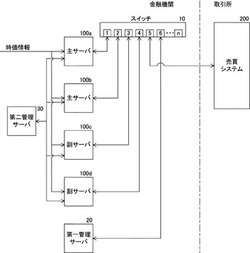

【課題】稼働中の主サーバが行う処理の遅延を引き起こすことなく、主サーバの生存監視を行うことができる生存監視システムを提供する。

【解決手段】スイッチ10は、各主サーバ100a,100bから信号が送られたときに、その信号をコピーして所定のポートから第一管理サーバ20に送出する。第一管理サーバ20は、スイッチ10からそのコピーされた信号を受信したときに、その送信元である主サーバが生存していると判定し、その判定結果及びその信号を受信した日時を示す日時情報に基づいて作成される当該主サーバの生存状況を示す情報を記憶部に記憶して管理する。第一管理サーバ20は、その管理する主サーバの生存状況を示す情報に基づいて当該主サーバからの信号が前回受信したときから所定時間送られてきていないと判断したときに、当該主サーバが生存していないと判定する。

(もっと読む)

電子制御装置

【課題】自動車に搭載される電子制御装置において、待機状態における消費電力の低減と、装置の小型化及び低コスト化とを実現すること。

【解決手段】電子制御装置1において、1つのウォッチドッグタイマ回路20が、稼働状態のCPU10の異常監視と、待機状態のCPU10の異常監視との両方を行う。待機状態のCPU10は、所定のウェイクアップ周期で動作モードを省電力モードから通常モードへ一時的に切り替える定期ウェイクアップ処理を行う。ウェイクアップ周期は、ウォッチドッグタイマ回路20のリセット監視時間(タイムアップ時間)よりも短い。さらに、待機状態のCPU10は、動作モードが通常モードに切り替わるごとに、センサの状態変化をチェックする処理及びウォッチドッグタイマ回路20のカウンタをクリアする処理を併せて実行する。

(もっと読む)

情報処理装置及び遠隔管理システム

【課題】遠隔監視される装置に異常が発生した場合に、容易に障害発生前後の装置の動作ログを取得する。

【解決手段】画像処理装置と連動することにより画像処理機能を提供する情報処理装置であって、画像処理機能を提供するメインコントローラと、LPCバス120を介してメインコントローラと接続されたEC130とを含み、EC130は、情報処理装置へ情報を入力する複数種類の入力ポートと、入力ポートを制御すると共にメインコントローラの異常を検知するメイン処理制御部131と、情報処理装置の異常動作時においてネットワーク通信を行うネットワーク通信制御部132とを含む。

(もっと読む)

多重系制御装置

【課題】雷などの影響を受け、2重系の片系が、誤動作により動作停止した場合には、他系に切り替わり、1重系動作状態となるため、早急に復旧させなければ、当該系まで停止した場合システムダウンし、列車の運行を停止させることになる。こうなると、従来にあっては、片系装置の停止原因が、一過性の事象による影響によるものであっても、保安装置(例えば信号機など)の保安者が現場に出向いて異常原因の確認と復旧を行っており、その時間や労力の負担が大きかった。

【解決手段】本発明は、上記課題を解決するために、多重系構成において、制御装置の状態を相互に監視し、停止した系に対し再起動の要求がなされ、停止した系を再起動させる手段を設けたものである。

(もっと読む)

モバイル端末のプログラム起動保全システム

【課題】モバイル端末内のエージェントプログラムが停止した場合に、極短時間でこれを回復させる保全技術を提供する。

【解決手段】エージェントプログラム14は、一定間隔でハートビートを発信するハートビート発信部24を備える。OSフレームワーク18は、ハートビートをヘルパープログラム16に伝達するハートビート伝達部28と、ヘルパープログラム16からの要請に基づいてエージェントプログラム14を再起動させると共に、ハートビートを伝達する時点でヘルパープログラム16が起動状態にない場合にこれを再起動させるプログラム起動部30を備える。ヘルパープログラム16は、ハートビートを受領する度にタイマーをリセットして時間を計測し、一定の時間を経過しても次のハートビートが伝達されない場合に、OSフレームワーク18にエージェントプログラム14の再起動を要請するエージェント監視部26を備える。

(もっと読む)

アプリケーション監視最適化装置

【課題】適切なオーバヘッドで動作し、アプリケーションの異常発生を容易に判断することのできるアプリケーション監視最適化装置を得る。

【解決手段】複数のアプリケーションプログラム103のそれぞれに、心音を発生する心音発生部202と、心音を監視する監視部201と、心音の発生タイミングを変更する心音変更部203と、監視タイミングを変更する監視変更部204とを備える。心音発生部202は、自アプリケーションプログラム103が正常に動作している場合は、これを示す心音を発生する。監視部201は、他のアプリケーション103の心音を監視する。

(もっと読む)

スタータ制御装置

【課題】メモリ機能付きの駆動回路を備えるスタータ制御装置にて、マイコンが制御処理の実行期間中に暴走してしまうことで不要なスタータ駆動がされてしまうのを防止する。

【解決手段】スタータ制御装置は、マイコンからの駆動指令を受けるとマイコンからの停止指令を受けるまでの間、スタータに駆動電流を流す方の出力オン状態を維持する駆動回路と、マイコンの暴走を検知するとマイコンをリセットして再起動させるリセット回路とを備えている。そして、マイコンは、起動直後に初期処理を一回実行した後、スタータを制御するための通常処理(上記指令を出す制御処理)を繰り返し実行するようになっている。更にマイコンは、初期処理の中で、駆動回路が出力オン状態であると判定するとバックアップRAM内のカウンタCをインクリメントし、カウンタ値が所定値(例えば3)に達したと判定すると駆動回路に停止指令を出力して該駆動回路を出力オフ状態にする。

(もっと読む)

電子制御装置

【課題】監視対象であるCPU等の処理部の処理負荷を増大させることなく、WDTの故障診断を行うことの可能な電子制御装置を提供する。

【解決手段】プログラムに従って所定の処理を実行する処理部と、前記処理部から一定周期で出力されるパルス信号によってリセットされるタイムカウンタを有すると共にオーバーフロー発生の有無によってレベルが反転する信号を出力するウォッチドッグタイマと、を備えた電子制御装置において、前記ウォッチドッグタイマの出力信号をラッチし、当該ラッチによって得られた信号を第1の出力イネーブル信号として出力するラッチ回路を備え、前記処理部は、前記ウォッチドッグタイマの故障診断時に前記パルス信号の出力を停止し、前記パルス信号の出力停止後に前記ラッチ回路から出力される前記第1の出力イネーブル信号を基に前記ウォッチドッグタイマの故障診断を行う。

(もっと読む)

コンピュータシステムの異常推定方法およびコンピュータシステムの異常推定プログラム

【課題】異常原因の把握を可能とするコンピュータシステムの異常推定方法およびコンピュータシステムの異常推定プログラムを提供する。

【解決手段】マイクロコンピュータ44は、診断対象のコンピュータシステムにおける、ウオッチドッグタイマ回路のカウンタ値のオーバーフロー回数である第1の値を記憶する第1の記憶部から第1の値を読出し、LVD回路の電圧降下回数である第2の値を記憶する第2の記憶部から第2の値を読出し、クロック供給回路の発振停止回数である第3の値を記憶する第3の記憶部から第3の値を読出す。マイクロコンピュータ44は、第1の値、第2の値、および第3の値と異常原因との関係を定めた異常原因推定テーブルを参照して、読み出した第1の値、第2の値、第3の値に対応する異常原因を推定する。

(もっと読む)

ウォッチドッグタイマ回路

【課題】ウォッチドッグタイマ回路におけるエラー信号の出力動作の故障を検出できるようにすること。

【解決手段】初期化信号に応じてトグルする選択信号を出力する選択信号出力回路と、初期化信号に応じて初期化されるとともにオーバーフローするとそれぞれ第1および第2のオーバーフロー信号を出力する第1および第2のカウンタと、選択信号に応じて第2のオーバーフロー信号および所定のクロック信号の一方を選択し、カウント用のクロック信号として第1のカウンタに出力する第1のセレクタと、選択信号に応じて第1のオーバーフロー信号および所定のクロック信号の一方を選択し、カウント用のクロック信号として第2のカウンタに出力する第2のセレクタと、選択信号に応じて第1のオーバーフロー信号および第2のオーバーフロー信号の一方を選択して出力する第3のセレクタと、を備える。

(もっと読む)

制御装置

【課題】CPUの暴走を検知して正常な状態に復帰させるためにWDT回路は有効であるが、複数のCPUを備えた制御装置では、全てのCPUに各々WDT回路を設けたのではコストが高くなると共に制御装置が大型化するという問題が生じる。

【解決手段】メインCPUが暴走した場合にメインCPUをリセットして正常化するウォッチドッグタイマ装置をメインCPUに対して設けると共に、メインCPUがサブCPUの作動状態を監視し、サブCPUが暴走した場合にはメインCPUがサブCPUをリセットする。

(もっと読む)

制御装置

【課題】プログラムが暴走した場合であっても暴走を自動的に検知して当該プログラムを容易に書き換える。

【解決手段】第1記憶部と、クリア信号の入力の都度時間計測を開始し直し、所定の検出時間が経過すると異常の発生を示す情報を第1記憶部に記憶し且つリセット信号を出力するウォッチドッグタイマと、所定タイミングでクリア信号を入力するメインプログラムとメインプログラムを書き換える書き換えプログラムとプログラムの実行を制御するブートプログラムとを記憶する第2記憶部と、制御部とを備え、ブートプログラムは、制御装置の起動時及びリセット信号が出力されたときに制御部によって実行され、第1記憶部に異常の発生を示す情報が記憶されていない場合、ウォッチドッグタイマにクリア信号を入力後、メインプログラムを実行し、異常の発生を示す情報が記憶されている場合、書き換えプログラムを実行する。

(もっと読む)

車載電子制御装置

【課題】マイクロコンピュータの異常の詳細を適切に診断することができる車載電子制御装置を提供する。

【解決手段】マイクロコンピュータ(MCU2)の内部に、ハードウェア部21の主機能22の入出力を監視することで故障を検出する監視機能23と、ソフトウェア部24の主機能25の演算結果を監視することで異常を検出する監視機能26とを設ける。さらに、MCU2の外部に、MCU2の異常を監視する故障処理回路5を設ける。故障処理回路5はMCU2のクロック27を監視するクロック監視処理52と、監視機能23及び監視機能26のウォッチドッグタイマ(WD)の出力パルスをそれぞれ監視するパルス監視処理53とを備える。

(もっと読む)

情報処理装置、情報処理方法及びプログラム

【課題】外部装置が接続されたときに、動作ログを必要な場合にのみ外部装置に保存する情報処理装置を提供する。

【解決手段】情報処理装置の一例である画像処理装置は、動作ログをログ領域250に保持し、システム監視・デバッグログプロセス221がUIを制御するUI制御プロセス220がエラー状態にあるか否かを監視する。USBドライバ230がUSBメモリメディア140の装着を検知すると、システム監視・デバッグログプロセス221は、UI制御プロセス220が正常に動作しているかの生存確認を行い、エラー状態にあると判定した場合に、ログ領域250に保持されている動作ログをUSBメモリメディア140に保存する。

(もっと読む)

リセット回路

【課題】ウォッチドッグのための特殊な構成を追加することなく、マイコンラッチ時に自動的かつ確実にマイコンにリセットをかける

【解決手段】水晶振動子Xtalを用いた水晶発振回路からクロック信号を入力されるマイコン200のリセット回路100であって、マイコン200は、出力がHighとLowとで周期的に変動するGPIO端子201を備え、クロック信号の入力が停止されたときに自動的にリセット状態となる構成とされ、リセット回路100は、GPIO端子201の出力をコンデンサを用いて平滑し、平滑電圧がHighとLowの中間電位のときは水晶振動子Xtalの負性抵抗より小さい抵抗を発生して水晶振動子Xtalに印加し、平滑電圧がHighとLowのいずれかになると水晶振動子Xtalの負性抵抗以上の抵抗を発生して水晶振動子Xtalに印加する。

(もっと読む)

プログラム群

【課題】ブートプログラムから基本プログラムに切り替わる時に、規定されたウォッチドッグ信号を確実に供給できるようにする。

【解決手段】ブート処理が実行されている間は、WDカウント値がWD閾値THw1に達する(即ち、WD周期が経過する)毎にWD信号の信号レベルを反転させ、通常処理が実行されている間は、WDカウント値がWD閾値THw2に達する(即ち、WD周期が経過する)毎にWD信号の信号レベルを反転させている。ブート処理から通常処理に切り替わるタイミングでは、引継情報に基づいて、WDカウント値の初期値を、初期オフセット時間が経過するとWD閾値THw2に達するような値に設定する。

(もっと読む)

RAS機能を備える組み込み機器

【課題】RAS機能を一箇所にまとめて実装することにより、RAS機能の信頼性、確実性の向上を図り、ブートローダ、OS、およびアプリケーションソフトウェアがRAS機能にできる限り依存しない構成とした組み込み機器を実現する。

【解決手段】複数のアプリケーションが、システムソフトウェアのデバイスドライバを介してハードウェアを構成する複数の物理デバイスを利用すると共に、前記アプリケーションおよびハードウェアに対するRAS機能を実装する、RAS機能を備える組み込み機器において、

前記システムソフトウェアと前記ハードウェア間に介在させたハイパーバイザ層内に、前記複数のアプリケーションおよびハードウェアのRAS機能を統合して一元管理する、論理RAS機能部を実装する。

(もっと読む)

フォールトトレラント計算機システム、フォールトトレラント計算機システムの制御方法、及びフォールトトレラント計算機システムの制御プログラム

【課題】特別なハードウェアを使用せずに、簡便、高速に系の切り換え可能な低消費電力のフォールトトレラント計算機システム、フォールトトレラント計算機システムの制御方法、及びフォールトトレラント計算機システムの制御プログラムを提供する。

【解決手段】ゲストOS3aが稼働中の仮想計算機を有する計算機1aと、稼働中の計算機1bとを含むフォールトトレラント計算機システムにおいて、計算機1aは、チェックポイント毎の差分情報からなる、ゲストOS3aのゲストOSスナップショット10aを、計算機1aのメモリ4aに保存し、チェックポイント毎に転送部11a及び11bを介して計算機1bのメモリ4bにゲストOSスナップショット10bとしてコピーする指示を出すスナップショットマネージャ8aを備え、計算機1bは、計算機1aが停止したときにゲストOSスナップショット10bに基づきゲストOS3bを起動するスナップショットマネージャ8bを備える。

(もっと読む)

自動リセット回路、自動リセット方法、プログラム、自動リセット装置および情報端末

【課題】 MPUを用いることなく、ハードウェアリセットに依らなければ回復不可能な異常発生の際に、ハードウェアリセットを実施しシステムを回復する自動リセット回路を提供する。

【解決手段】 電源電圧確定回路5が、電源電圧確定信号14を出力し、リセット信号出力手段2が、タイマー1から出力されるタイマー信号11により起動してリセット信号10を出力し、リセット信号出力制御手段4が、コンピュータ起動時に、リセット信号出力手段2を制御し、ファームウェア6が、リセット信号出力制御手段4を稼働させ、タイマー1の初期化とタイマー設定を行いタイマー信号11を無効化し、割り込み検出回路7が、コンピュータ稼働中に、タイマー1の時間の経過により割り込み処理の実行を検出して出力した割り込みハンドラー起動信号13を受けて、割り込みハンドラー6が起動し、タイマー1の初期化とタイマー設定を行い、タイマー信号11を無効化する。

(もっと読む)

情報処理装置、記録方法、及びプログラム

【課題】本発明が解決しようとする課題は、上記問題点を解決することであり、CPUの動作履歴記録用メモリーの容量を少量化することである。

【解決手段】上記課題を解決するための本発明は、記録装置であって、監視対象である情報処理装置のCPUの動作履歴が、ウォッチドッグタイマーのカウンター値がクリアされる周期に対応付けられて記録されている動作履歴記録部と、前記動作履歴を前記動作履歴記録部に記録し、前記クリア後に新たに前記CPUの動作を記録する際、前記CPUに障害が発生しなかった周期の動作履歴に上書きする記録手段とを有することを特徴とする。

(もっと読む)

1 - 20 / 181

[ Back to top ]