Fターム[5B046BA03]の内容

CAD (21,103) | 設計対象(段階、工程) (4,232) | 回路設計 (1,280)

Fターム[5B046BA03]に分類される特許

1,261 - 1,280 / 1,280

テンプレートを利用したドメイン固有の再構成可能な論理

再構成可能な論理コアのアーキテクチャを創成する方法が開示される。このアーキテクチャは、種々の目的に合わせて展開でき、その具体化は、エリア、性能及び電力の面で費用効果がよい。本発明は、テンプレートを用いるとかかるアーキテクチャを記述できるという知見を利用している。この場合、このアーキテクチャをテンプレートのインスタンスとして容易に創成できる。テンプレートは、再構成可能論理コアの論理コンポーネント、経路指定コンポーネント及びインタフェースコンポーネントを定めるモデルである。例えば、論理コンポーネントは、階層的順序で並んだ論理素子、処理素子、論理ブロック、論理タイル、及びアレイであるのがよい。経路指定コンポーネントは、論理コンポーネント相互間の相互接続手段となる経路指定軌道を含む経路指定チャネルから成るのがよい。インタフェースコンポーネントは、入力ポート及び出力ポートから成るのがよい。モデルは、多くのパラメータによって構成され、これらパラメータの値は、アプリケーションドメインに一致する。  (もっと読む)

(もっと読む)

グラフ幅削減装置及びグラフ幅削減方法、並びに論理回路合成装置及び論理回路合成方法

多出力論理関数に対し、中間出力を有するLUT論理回路が合成可能な論理回路合成装置を提供する。

多出力論理関数f(X)の特性関数x(X,Y)の特性関数二分決定グラフ節点テーブル記憶手段8と、LUT記憶手段16と、特性関数二分決定グラフを所定の高さlevの分割線で部分グラフB0,B1に分割し短絡除去処理を行う短絡除去手段11と、分割線における幅Wを計測するBDD幅計測手段12と、幅Wに基づき中間変数の個数を算出する中間変数算出手段13と、部分グラフB0につきLUTを生成するLUT生成手段14と、中間変数の個数uと等しい制御入力数を有する二分木を生成し、部分グラフB0を二分木で置き換え、特性関数二分決定グラフを再構成するBDD再構成手段15とを備えた構成とした。  (もっと読む)

(もっと読む)

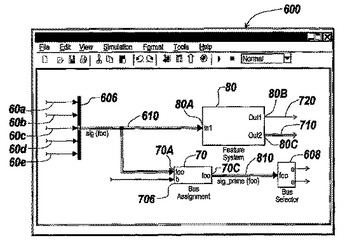

ダイアグラミング環境言語のための単純化データ信号サポート

グラフィカルモデリング環境において、モデルを単純化するため複数信号をグループ化したバス信号は、部分的又は完全な物理的定義を含む。モデルは、このバス信号は、非グループ化することなく、機能的実態を表現するグラフィカルオブジェクト内を通過させることで単純化される。モデルのシミュレーション時に、このモデルの他の構成要素からは独立して、完全な定義を備えたバス信号のコードが生成される。

(もっと読む)

(もっと読む)

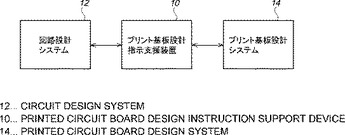

プリント基板設計指示支援方法およびその装置

プリント基板設計作業効率の向上ならびにプリント基板設計品質の向上に資する回路設計とプリント基板設計間におけるプリント基板設計指示支援方法、回路設計とプリント基板設計間におけるプリント基板設計指示支援装置、Webシステム、プログラムおよびコンピューター読み取り可能な記録媒体を提供するものであり、設計ルールが適用される回路部品を選択すれば、回路設計システムとプリント基板設計システムとの連携により、回路図とプリント基板上のチェック対象部分とを同時に表示して、チェック時間の短縮と手間を低減するようにした。  (もっと読む)

(もっと読む)

特定用途向け集積回路設計の設計検証を高速化する方法及び装置

フィールド・プログラマブル・ゲート・アレイ・デバイス(FPGA)などのリプログラマブル・デバイスを用いてソフトウェア・シミュレータの動作を高速化する方法及びシステムである。この方法及びシステムは、リプログラマブル・デバイスを用いて、特定用途向け集積回路(ASIC)のデジタル回路設計のエミュレーション及びプロトタイピングを行うようにしたものである。このシステムは、設計検証マネージャ・ソフトウェア・プログラムを備えており、このソフトウェア・プログラムは、クロック・ソースを探索するサブルーチン、クロック・ソースからクロック信号を受取っている同期要素を探索するサブルーチン、それに、クロック・ソースとかかる同期要素との間にエッジ検出回路を挿入するサブルーチンを含んでいる。この新規な方法は、基本クロックである設計クロックを、クロック・トリガ入力端子へ供給する替わりにクロック・イネーブル入力端子へ供給するようにし、また、その設計に含まれているその他全てのクロックに対して自動的に遅延させた新たなクロックを生成してクロック・トリガ入力端子へ供給することにより、クロック・タイミングに関する問題を解消できるようにしたものである。このシステムは、自動的なリターゲッティングによってASIC設計をリプログラマブル・デバイスに変換する際に、その変換後のリプログラマブル・デバイスが、ASICとFPGAとで互いにクロッキング・チェーンのタイミングが異なることから、複数のフリップフロップ及び複数のラッチを異なった時刻にトリガすることになるような場合に生じていた障害を解消するものである。  (もっと読む)

(もっと読む)

製造を容易にする設計

【課題】製造容易性を改善するために、既存の超小型装置設計を変更する技術を提供する。

【解決手段】これらの技術により、設計者は、設計に於けるデータに関連した製造基準を受領する。次に、関連した設計データが識別されて、超小型装置設計者へ供給され、該設計者は、製造基準に基づいて設計変更を選択することが出来る。このようにして、設計者は、超小型装置の元の設計に於いて、半導体ファンドリからの製造基準を直接的に包含させることが出来る。

(もっと読む)

マスクプログラム可能なロジックデバイスをプログラムする方法およびその方法によってプログラムされたデバイス

マスクプログラム可能なロジックデバイス(MPLD)に対するユーザーのロジック設計は、互換性を有するユーザープログラム可能なロジックデバイス(UPLD)上で設計されMPLDに移行され得る、または直接MPLD上で設計され得る。設計がUPLD上でなされる場合には、目標のMPLDの制約(例えば、デバイスの間の差異)が考慮され、その結果、移行は成功する。設計が直接MPLD上でなされる場合には、その設計を試験のためにUPLDに移行することをユーザーが意図するときに、互換性を有するUPLDの制約が考慮される。これは、ロジック設計のUPLDとMPLDとの間で行き返りの移行が意図される場合にのみ、特徴の一致が使用され得ることを意味する。移行を助長するためにデバイスのペアの間の固定されたマッピングが生成され得る。  (もっと読む)

(もっと読む)

集積回路開発システム

本発明の実施形態には、集積回路開発用のシステムが含まれる。この開発システムの要素には、ハードウェアオブジェクトとソフトウェアオブジェクトが含まれる。これらのオブジェクトは、ソフトウェア環境においてインスタンス化され、整列され、パラメータが決められ、接続されることにより異なる機能を実現する。ソフトウェアにおいては、その記述により1組のオブジェクトのトポロジと特性、ひいては機能全体が定義される。これらのオブジェクトは1組のプリミティブオブジェクトから階層的に構成されている。予め確立され、カプセル化されたハードウェアオブジェクトとして設定されたプリミティブオブジェクトをモデル化することができるハードウェアを使用すれば、トポロジと特性とが、所望の実行機能を発揮できるハードウェアを定義する。本発明の実施形態を用いれば、回路設計者は、ハードウェアまたはハードウェアデザインについてほとんど知識がなくても、あるいは全く知識がなくても、高レベルなソフトウェア記述だけでハードウェアシステムを設計することができる。 (もっと読む)

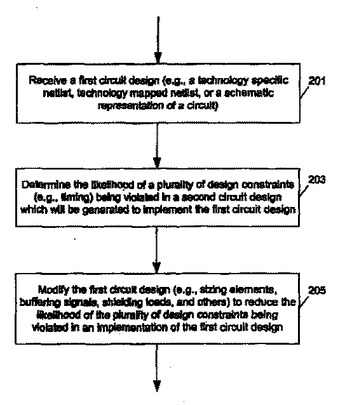

自動回路設計のための方法と装置

回路の後の実装で生じうる逸脱に応じて回路設計を自動的に修正する方法と装置。一態様では、回路を設計する方法は、回路の設計の後の配線実装時に設計制約条件に違反する可能性があるかどうかを判定することと、後の実装で設計制約条件に違反する可能性を低減するように回路設計を修正することを含む。例えば、2よりも大きい多数のファンアウトを持ち、タイミング・クリティカル・パスまたはクリティカルに近いパス上のネットに対する経路は、経路トポロジに敏感であると考えられ、代替配線経路であると、タイミング制約に違反する可能性があり、その後の配線ソリューションのタイミング問題が発生する可能性を低減するために、コスト関数を悪化させない範囲で、回路設計に変換を選択的に適用するとよい。  (もっと読む)

(もっと読む)

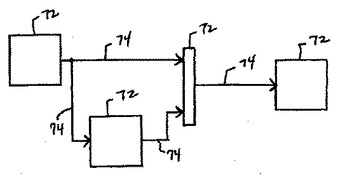

回路設計およびリタイミングの方法および装置

回路を階層的にリタイミングする方法と装置。本発明の少なくとも1つの実施形態では、(例えばモジュール・レベルでのリタイミングを介して)異なる複数の最小クロック周期を有するように異なる複数のレイテンシを備える回路のモジュールが設計される。一例では、モジュールの配置配線の後、詳細なタイミング分析から最小クロック周期が決定され、モジュールを含む回路のリタイミングの際に、回路の目的のクロック周期、とレイテンシと最小クロック周期との間の相関に基づいてモジュールのデータ・フロー・グラフ表現が構築される。本発明の少なくとも1つの実施形態では、階層的なリタイミングが実行される。これは、回路の一部分がリタイミングされて(例えば異なるレイテンシについての)結果が生成され、その結果が目的のクロック周期に基づく回路全体のリタイミングに選択的に使用されるものである。  (もっと読む)

(もっと読む)

ブロックモデリング入出力バッファー

ブロックダイヤグラム・モデルのブロックにおける信号I/Oバッファーをアドレス指定する方法は、基底アドレスと、要素オフセットと、折り返しサイズと、先頭オフセットと、ストライド因子とを決定する段階を含む。

(もっと読む)

(もっと読む)

マルチチャネル回路の自動合成の方法および装置

シングルチャネル回路から時間多重化マルチチャネル回路を自動的に生成する方法および装置である。本発明の少なくとも1つの実施形態は、シングルチャネル回路の設計からマルチチャネル回路の時間多重化設計を自動的に生成することによって時間多重化リソース共有のためのマルチチャネルハードウェアを自動的かつ効率的に合成する。シングルチャネル設計のチャネル固有の要素(例えば、レジスタやメモリ)は、複数のチャネルの信号処理をパイプライン化するための、N倍の容量を有する、対応する要素に置き換えられる。 (もっと読む)

カットベース手法を用いたリタイミング回路

集積回路をリタイミングするための方法および装置について説明する。本発明のいくつかの実施形態によれば、リタイミングは、集積回路内の1つまたは複数のパスについてタイミング解析を実行してスラック値を取得するステップと、取得したスラック値に基づいてパスの1つを選択するステップと、選択したパス沿いのリタイミング可能カットを決定するステップとを含む。これらの例示的な実施形態におけるリタイミング可能カットは、集積回路内の1つまたは複数の論理インスタンスの一組の入力ピンを含み、選択したパスのスラック値を改善するため、それらのピンに1つまたは複数のリタイミングした順序素子を結合することができる。具体的な実施形態では、リタイミング可能カットは、選択したパス沿いの複数の可能なカットから自動的に選択される。集積回路をリタイミングするためのその他の実施形態、ならびに開示の方法によってリタイミングされる集積回路、および回路設計データベースも開示される。開示の方法を実行するための命令を保存するコンピュータ実行可能媒体も開示される。  (もっと読む)

(もっと読む)

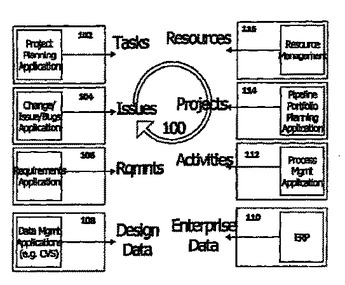

分散設計ネットワークを管理するためのシステム及び方法

分散設計ネットワークを、特にデータが複数のアプリケーション内にあり、複雑な相互関係によってリンクされているドメインに対して、管理するために用いられる、システム、アーキテクチャ及びデータ構造が開示される。発明によって統合される設計ネットワークは、新製品を設計及び開発するために共同している、複数のサイトにある複数の会社を含むことができる。発明の目的は、設計に関係する相互にリンクされたデータを含む、既存の様々なレガシーアプリケーションをシームレス及び公明に統合し、よって分散設計ネットワーク管理の要件に対処することである。  (もっと読む)

(もっと読む)

LSI回路のリグレッションテストシステム、及びそれに用いる装置とそのリグレッションテスト方法

【課題】検証中のLSI回路の設計変更があるごとにリグレッションテストの必要性を判断し、必要なら実行可能とする。

【解決手段】データ管理装置1で、入力設計データ11、テストベンチ12を登録済みデータとの差分チェックを行いながらデータベース13に登録し、検証内容に応じたデータをシミュレーション装置2へ送る。差分チェックにおいて入力設計データに差分があると、シミュレーション装置で実行中(予約中)のリグレッションテストがあるか問合せ、ある場合は、利用者の確認を得てから中止させる。ない場合及び中止後は、利用者の確認を得てから最新の設計データに関連するテストベンチをデータベースより読み出し最新の設計データと組にしてシミュレーション装置へ送出する。

(もっと読む)

非同期シリアルパラレル変換方法および変換回路

【課題】従来方式の非同期シリアルパラレル変換回路のVHDL記述では、内蔵クロックバッファが使用できない場合に、クロックスキューが大きくなり、複数の非同期シリアルパラレル変換回路を正常に駆動することができなかった。

【解決手段】シリアルクロック(sr_clk)を、バッファ12、13により分岐し、それぞれ独立したシリアルクロックsr_clk3およびsr_clk2をoddデータ用の第1シフトレジスタを構成するFF14〜FF17およびevenデータ用の第2シフトレジスタを構成するFF18〜FF21に入力する。これにより、同一のシフトレジスタ内では、同一のバッファから出力されるクロックを使用するように、意図的に個別のバッファを挿入するようVHDLで記述することにより、クロックスキューを小さくする。

(もっと読む)

マイクロストリップ線路放射電磁界解析装置及び方法及び解析用プログラム

【課題】実際には放射に寄与しない伝送モードや表面波モードの影響を省き、近傍領域において放射に関与する電磁界成分のみを解析することができ、外部不均質性の放射電磁界の与える影響を評価することができるマイクロストリップ線路放射電磁界解析装置、放射電磁界解析方法及び放射電磁界解析用プログラムの提供。

【解決手段】マイクロストリップ線路の電流分布に応じて、配線部電流分布から波数空間の電流分布にフーリエ変換し、波数空間の電流分布から波数空間の電磁界分布を計算し、得られた波数空間の電磁界分布から表面波モードと伝送モードに相当する電磁界分布を消去し放射モードに相当する電磁界分布のみを実空間の電磁界分布にフーリエ逆変換することにより、近傍領域において放射電磁界のみを抽出し、さらにその近傍領域放射電磁界分布から遠方領域の電磁界分布も算出する。

(もっと読む)

伝送線路における誘電損をモデル化する方法

【課題】高周波においても、伝送線路における誘電損を正確にモデル化する。

【解決手段】コンピュータチップまたは回路基板上の伝送線路における誘電損を、回路シミュレーションアプリケーションを用いてモデル化するソフトウェアによる方法を開示する。線路の抵抗、自己インダクタンスおよび自己キャパシタンスが、直列接続された抵抗およびインダクタと並列接続されたキャパシタンスを持つ集中素子回路として計算されモデル化される。2ポート散乱行列を使用して、誘電損をモデル化する。この方法は、線路を取り囲む媒体の誘電率、該線路の長さ、および信号の周波数に関連する行列を用いる。この方法は、回路基板またはICチップの典型的な低損失状態を仮定し、これにより、該線路の固有インピーダンスは損失による影響を受けず、上記行列は該固有インピーダンスに正規化される。

(もっと読む)

プリント基板の配線構造チェックシステム

【課題】 チェック対象とする電源プレーン上に配線される高速信号配線の配置を、他配線層への電磁的な悪影響を及ぼさない位置に指定する。

【解決手段】 チェック対象となる信号配線に関し、電源プレーン1上に、高速信号配線13が存在する場合に、該高速信号配線13に最も近い電源プレーン1の端部と該高速信号配線13との垂直距離(dist)を測定すると共に、上記信号配線に係る回路仕様から、上記垂直距離として最低限確保すべき距離を予め計算し、上記測定した垂直距離(dist)と、上記計算した最低限確保すべき距離とを比較して、上記測定した垂直距離(dist)が、上記最低限確保すべき距離を超えていない場合には、上記信号配線名に対応する適切な指示メッセージを表示する。

(もっと読む)

集積回路装置の設計方法

【課題】 各ブロックの無駄なセルのない消費電力の小さいシステムLSIの設計を容易に行なうことができる設計方法を提供する。

【解決手段】 インターフェイス、消費電力、動作モデル,トップ階層の接続などに関する情報を格納するモジュールスペック1と、各ブロックの動作の排他律を記述する排他的動作情報2と、各機能の同時作動を回避するための優先機能情報3とを自動生成ツールであるジェネレータ4に入力して、省電力化のためのパワー&クロックマネジメントモジュール5と、接続情報に関するWrapper・BANK・セレクトモジュール6と、共有可能な資産に関する共有リソースモジュール7と、最適化されたトップ階層の接続情報に関する最適化トップ階層モジュール8とを生成する。資産の共有化による小型化と、パワーマネジメントによる省電力化とを実現する。

(もっと読む)

1,261 - 1,280 / 1,280

[ Back to top ]