Fターム[5B046KA06]の内容

CAD (21,103) | ファイル、データベース/その他 (1,236) | データベース (1,035) | ライブラリ (209)

Fターム[5B046KA06]に分類される特許

1 - 20 / 209

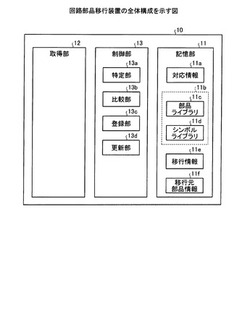

回路部品移行装置、回路部品移行プログラムおよび回路部品移行方法

【課題】シンボルを引継いで回路部品を移行できる回路部品移行装置、回路部品移行プログラムおよび回路部品移行方法を提供する。

【解決手段】回路部品移行装置10は、特定部13aと、比較部13bと、登録部13cとを有する。特定部13aは移行元の回路部品に対応する移行先の回路部品を示す対応情報11aに基づき、移行対象の回路部品に対応する移行先の回路部品を特定する。比較部13bは特定された移行先の回路部品を表すシンボルと前記移行対象の回路部品を表すシンボルとの形状を比較する。登録部13cは比較の結果、同一の形状でない場合、移行先の回路部品を記憶する移行先部品情報11bに前記移行対象の回路部品を表すシンボルを特定された移行先の回路部品に関連付けて登録する。

(もっと読む)

図面作成支援装置

【課題】多数のページにわたる図面の作成にテンプレートを利用する場合に、必要な操作手順を少なくして作業効率を向上することができる図面作成支援装置を提供する。

【解決手段】図面作成支援装置において、新規に図面ファイルを作成するときの基礎として利用可能なように標準化された複数の図面テンプレートと、複数の図面テンプレートの相対的なページ位置関係を定義するテンプレート配置リストと、を予め記憶する記憶装置と、ユーザの操作により、複数の図面ファイルと複数の図面ファイルのページ位置関係を規定するファイル配置リストとを作成可能な図面管理手段と、を備え、図面管理手段は、テンプレート配置リストに定義された相対的なページ位置関係を維持したまま、複数の図面テンプレートを複製したものを、複数の図面ファイルとしてファイル配置リストに登録する構成とする。

(もっと読む)

遅延ライブラリの生成方法及び遅延ライブラリ生成装置

【課題】静的タイミング解析ツールの処理結果に対する後処理時間を短くすること。

【解決手段】本発明にかかる遅延ライブラリの生成方法は、入力クロック信号を内部で分周するマクロの遅延ライブラリの生成方法であって、マクロの設計情報に基づいて、入力クロック信号を内部で分周する分周回路を抽出するステップと、抽出された分周回路が静的タイミング解析においてクロックラインの一部とみなされるように設計情報を修正する修正ステップと、修正された設計情報を用いて遅延ライブラリを生成する生成ステップと、を有する。

(もっと読む)

レイアウトデータ作成装置及び半導体装置

【課題】従来のようにピラーの分割単位が小数点数とならず、単位ピラートランジスタのピラーの径の変更を行う必要が無くなり、半導体装置を製造するプロセスを複雑化することなく、ピラー型のトランジスタによりセルを、セルロウ内に効率的に配置するレイアウトデータ作成装置を提供する。

【解決手段】本発明のレイアウトデータ作成装置は、集積回路における複数の単位ピラー型トランジスタで構成されるピラー型トランジスタを、配置領域内に配置可能な単位ピラー型トランジスタの整数単位に分割し、配置領域内に配置するサブピラー型トランジスタを生成するトランジスタ調整部2を備えている。

(もっと読む)

コンピュータ支援設計のシステム内でオブジェクトのアセンブリを設計するための方法およびシステム

【課題】オブジェクトの反復アセンブリを容易および高速にする。

【解決手段】コンピュータ支援設計のシステム内でオブジェクトのアセンブリを設計するコンピュータ実行方法であって、少なくとも1つの三次元ジオメトリ要素を備えた三次元ジオメトリモデル形成オブジェクトを提供するステップ(90)と、少なくとも1つの論理構成要素を備えた論理モデル形成オブジェクトを提供するステップ(91)と、少なくとも1つの三次元ジオメトリ要素のセットを少なくとも1つの論理構成要素のそれぞれのセットと関連付けるステップ(92)とを含み、少なくとも1つの三次元ジオメトリ要素の対応する関連するセット上に一部重畳された少なくとも1つの論理構成要素のセットの表現を三次元シーン内に表示するステップ(93)をさらに含むことを特徴とする方法。

(もっと読む)

階段用CAD/CAMシステム

【課題】システムに予め登録された組合せ階段や単一部品の仕様とは異なる仕様の組合せ階段や単一部品を登録できるようにして、汎用性を持たせた階段用CAD/CAMシステムを提供する。

【解決手段】階段を設計するCADシステム部11と、階段の単一部品のNC加工データを作成するCAMシステム部12とを含むCAD/CAMシステムにおいて、CADシステム部11は、階段を構成する単一部品を定義して登録する単一部品登録部13と、組合せ階段を定義して登録する組合せ階段登録部14とを備える。単一部品登録部13は、単一部品を、部品識別コードと、各頂点の座標を仕様パラメータを変数として求める数式とによって定義して登録する。組合せ階段登録部14は、組合せ階段を、組合せ階段識別コードと、単一部品の部品識別コード及び数量とによって定義して登録する。

(もっと読む)

マスクデータ検証装置、設計レイアウト検証装置、それらの方法およびそれらのコンピュータ・プログラム

【課題】半導体装置の製造期間を短縮できると共に、効率的に開発を行なって製造歩留を向上させることが可能なマスクデータ検証装置を提供すること。

【解決手段】マスクデータ検証装置は、設計レイアウト21と既存種ライブラリ22に格納される設計レイアウトパターンとを比較して、同一でなく類似でもない設計レイアウトパターンを新種の設計レイアウトパターンとして抽出する(S62)。そして、新種ライブラリ23に格納された新種の設計レイアウトパターンに対してOPC/RETを用いてマスクデータを作成し(S63)、後検証を行なう(S64)。したがって、予め新種の設計レイアウトパターンの検証が行なえ、半導体装置の製造期間を短縮できると共に、効率的に開発を行なって製造歩留を向上させることが可能となる。

(もっと読む)

ホールドエラー修正方法、ホールドエラー修正装置及びホールドエラー修正プログラム

【課題】ホールドエラーをより確実に修正することが可能なホールドエラー修正方法、ホールドエラー修正装置及びホールドエラー修正プログラムを提供する。

【解決手段】ホールドエラー修正方法は、レイアウトデータ53に対しタイミング解析を行ってタイミングレポート54を生成し、ホールドエラーセルとは別のセルを置換元セルに選択し、置換元セルよりも駆動能力が小さいセルを置換先セルに選択し、レイアウトデータ53において置換元セルを置換先セルに置換し、置換により生成された空き領域に、ホールドエラーセルのホールドエラーを修正するためのホールドバッファを挿入して、挿入したレイアウトデータを生成するものである。

(もっと読む)

論理集積回路のCADシステム及びスピントロニクス論理集積回路の設計方法

【課題】設計フローの最小限の変更のみでスピントロニクス論理集積回路の設計体系を確立する。

【解決手段】論理集積回路のCADシステムは、ハードウェア記述言語で記述された動作記述レベルあるいは論理ゲートレベルの論理集積回路ネットリストから、論理合成ツールの入力となるスピントロニクス論理ゲートを含む動作レベルの論理集積回路ネットリストへの変換手段を含む。変換手段は、指定される不揮発化対象の論理信号を入力とする組み合わせ回路の一部をスピントロニクス論理回路に変換する。

(もっと読む)

三次元シーンにおけるオブジェクトの三次元モデル化アセンブリの設計

【課題】本発明は、三次元シーンにおいてオブジェクトの三次元モデル化アセンブリを設計するためのコンピュータ実装方法を提供する。

【解決手段】上記方法は、三次元シーンにおいて三面体の事前に規定されたセットを位置付けおよび方位付けするステップであって、それぞれの三面体が位置と方位とを規定する、位置付けおよび方位付けするステップ(S100)と、オブジェクトのセットを提供するステップ(S120)と、オブジェクトのセットのそれぞれのオブジェクトを三面体の事前に規定されたセットの対応する1つの三面体に取り付けるステップ(S130)と、三面体の事前に規定されたセットの対応する三面体の位置と方位とに従って、それぞれのオブジェクトを位置付けおよび方位付けするステップ(S140)とを含む。

(もっと読む)

半導体集積回路のレイアウト装置、レイアウト方法及びそれらに用いられるセルデータ

【課題】タイミング違反を容易に解消して工数の増大を抑制すること等が可能な半導体集積回路のレイアウト装置を提供すること。

【解決手段】本発明にかかる半導体集積回路のレイアウト装置は、セルデータを記憶する記憶装置13と、記憶装置13からセルデータを読み出して自動配置配線を行うレイアウト部242と、を備える。また、セルデータは、ターゲットセルに対する配置の状況に応じた遅延をターゲットセルに対して付加する遅延考慮フィラーセルの情報を有する。

(もっと読む)

製品設計支援装置及び製品設計支援方法

【課題】既存の生産設備及び治具に起因する制約を考慮した製品設計を、簡単且つ効率的に行うことを可能とする製品設計支援装置及び製品設計支援方法を提供する。

【解決手段】CADを用いて、複数の設備及び治具により構成された生産ラインによって生産される製品の設計支援を行うための製品設計支援装置であって、製品を生産する際に用いる複数の設備及び治具の形状のうち、選択された部位の形状だけを複写して三次元モデルとして集約し、当該集約した三次元モデルの形状情報を利用して製品設計を行う。

(もっと読む)

半導体集積回路の設計方法、設計プログラム、及び設計支援装置

【課題】半導体集積回路の設計TATを短縮する。

【解決手段】本発明による半導体集積回路の設計方法は、コンピュータ装置10によって実行される半導体集積回路の設計方法であって、論理セル500と配線セル400をチップ上に配置するステップと、論理セル500内のゲート505に対するアンテナルール122を配線セル400の第1アンテナ用ライブラリ101に追加することで、第1アンテナ用ライブラリ101を第2アンテナ用ライブラリ201に変更するステップと、配線セル400と他の論理セル510を第1配線550で接続するステップと、第2アンテナ用ライブラリ201に規定されたアンテナルール122に従い、ゲート505の面積に対する前記第1配線550の面積の比を検証する第1検証ステップとを具備する。

(もっと読む)

設計支援装置及び設計支援方法

【課題】設計効率の向上を図ること。

【解決手段】設計支援装置10は、既存の半導体集積回路に含まれる機能マクロの情報と、機能マクロ間の接続情報を含むアーキテクチャ情報が品種毎に管理されたデータベースから、作成する半導体集積回路に搭載する機能マクロを含む品種を検索する。そして、設計支援装置10は、検索により得られた品種のアーキテクチャ情報を前記データベースから抽出し、作成する半導体集積回路のアーキテクチャ情報と、抽出した前記品種のアーキテクチャ情報を比較し、設計する半導体集積回路のアーキテクチャ情報に類似するアーキテクチャ情報の品種を抽出する。

(もっと読む)

検証スティミュラス生成装置およびその検証スティミュラス生成方法

【課題】正常終了するシナリオと全てのエラーが発生するシナリオを個別に作成し、これらのシナリオから検証スティミュラスを生成していたので、作成するシナリオの数が膨大になり、かつ検証スティミュラス生成に時間を要していた。本発明は検証スティミュラスを効率よく生成できる方法及び装置を提供することを目的にする。

【解決手段】正常終了およびエラー発生のシナリオ定義を生成し、このシナリオ定義を検証シナリオテンプレートに適用してシナリオを生成してスティミュラスライブラリを生成し、定義番号を用いてシナリオ定義とスティミュラスライブラリ中のスティミュラスを読み込んで検証スティミュラスを生成する。効率よく検証スティミュラスを生成できる。

(もっと読む)

レイアウト設計装置、レイアウト設計方法、及びプログラム

【課題】シミュレーションを実行することなく、最適な配線幅の取得を行えるようにすることにより、シミュレーションの複数回実行による処理時間増大を防ぐ。

【解決手段】レイアウト設計装置は、フリップチップ構造の半導体集積回路のRDL(パッド−I/O端子間)配線処理において、I/Oセルの所要電流量と配線長に適した配線幅を取得するためのテーブルをライブラリ化して保持する手段と、パッドとI/Oセルの位置関係から配線に必要な距離を算出する手段と、パッドとI/Oセル端子間の配線に必要な距離とI/Oセルの所要電流量と前記テーブルから適切な配線幅を取得する手段とを有することを特徴とする。

(もっと読む)

三次元CADプログラム、装置および三次元CADの処理方法

【課題】三次元CADの剛体モデルから、部品の動作シミュレーションが可能な柔軟体モデルを算出する。

【解決手段】開示の三次元CADプログラムは、コンピュータに、線状の柔軟物を含む設計対象装置の三次元モデルの形状データを保持する手順、該形状データから該線状の柔軟物の断面を特定する手順、特定された該断面上の基準位置を決定する手順、該線状の柔軟物の該断面間を結ぶ曲面を構成するデータを特定する手順、特定された該曲面を構成するデータから、該断面間を結ぶ曲線を抽出する手順、特定された該線の法線方向を特定する手順、特定された該曲面の法線方向とは逆方向に、該断面の該基準位置間に合うように移動させることにより、該断面間を結ぶ経路を特定する手順、該断面の形状および基準位置と、該経路から、該線状の柔軟物の柔軟体モデルを特定する手順、を実行させる。

(もっと読む)

ライブラリ情報漏洩防止装置、ライブラリ情報漏洩防止方法及びライブラリ情報漏洩防止プログラム

【課題】計算機利用設計で用いるライブラリ情報の過度な漏洩を容易に防止できるライブラリ情報漏洩防止装置、ライブラリ情報漏洩防止方法及びライブラリ情報漏洩防止プログラムを提供することを課題とする。

【解決手段】ライブラリ情報漏洩防止装置であって、入力された設計データに含まれるライブラリ情報の項目を入力項目一覧データに登録する入力処理手段31と、入力項目一覧データ62を保持する入力項目一覧データ保持手段と、出力する設計データに含ませるライブラリ情報の項目を、入力項目一覧データ62に登録したライブラリ情報の項目に合わせる出力処理手段33とを有することにより上記課題を解決する。

(もっと読む)

部品ライブラリ作成装置及び部品ライブラリ作成方法

【課題】

本発明は、ライセンスキーの紛失を予防することで、確実にライブラリを作成できる部品ライブラリ作成装置または部品ライブラリ作成方法を提供することである

【解決手段】

本発明は、電子部品を撮像する部品撮像装置と前記撮像結果から前記電子部品の部品ライブラリデータを作成する処理プログラムを有するデータ作成装置とを有し、前記処理プログラムを起動するのに必要なライセンスキーを前記部品撮像装置に固定して設けたことを特徴とする。また、部品撮像装置は前記処理プログラムを起動するのに必要なライセンスキーを前記データ作成装置に送り、前記データ作成装置は送られてくるはずの前記ライセンスキーの存在を判断し、存在すれば前記処理プログラムを起動することを特徴とする。

(もっと読む)

半導体集積回路の設計方法および半導体集積回路の設計プログラム

【課題】配線が混雑する領域であっても最適な配線をすることができる半導体集積回路の設計方法を提供することである。

【解決手段】本発明にかかる半導体集積回路の設計方法は、所定の単位領域に配置されたレイアウトセルの端子数を調査し、単位領域のうち前記レイアウトセルの端子数が所定の値よりも大きい単位領域において、端子が存在する配線トラックである端子存在トラックと端子が存在しない配線トラックである空トラックとに分類すると共に、当該端子存在トラックが所定数以上連続する箇所を調査し、端子存在トラックが所定数以上連続する箇所における端子の位置を移動する。

(もっと読む)

1 - 20 / 209

[ Back to top ]