Fターム[5B054AA11]の内容

Fターム[5B054AA11]に分類される特許

1 - 20 / 50

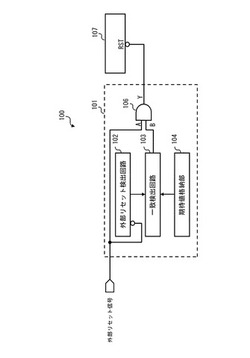

リセット信号生成回路及びそれを備えた半導体集積回路

【課題】電源投入後から外部リセット信号が最初にアクティブになるまでの期間にリセット信号をアクティブにすることが可能なリセット信号生成回路を提供すること。

【解決手段】本発明にかかるリセット信号生成回路101は、外部リセット信号が最初にアクティブになったことを検出する外部リセット検出回路102と、外部リセット検出回路102の検出結果が、外部リセット信号が最初にアクティブになる前であることを示す場合、外部リセット信号に関わらずリセット信号をアクティブにする制御回路と、を備える。

(もっと読む)

情報処理装置及びその起動方法

【課題】本発明は、優先順位の高い機能の初期化時間を遅延させることなく、全機能の初期化時間を短縮することが可能な情報処理装置、及びその起動方法の提供を目的とする。

【解決手段】本発明は、初期化により利用可能となる機能を複数有する情報処理装置である。本発明の情報処理装置は、前記機能をそれぞれ初期化する複数の初期化手段1〜nと、前記初期化手段1〜nの実施順序を決定する初期化順序決定手段12と、装置処理負荷を監視する装置処理負荷監視手段13と、実施中の前記初期化手段が1つ以上ある場合、当該1つ以上の初期化手段の処理に遅延が生じない第1の閾値に基づいて前記装置処理負荷を判定することにより、次の前記初期化手段Iの実施タイミングを決定する初期化タイミング決定手段15とを備える。

(もっと読む)

リセット回路

【課題】複数の電源電圧を駆動電圧とするSoC IC(System on a Chip Integrated Circuit)に対し、負荷変動やノイズに影響されること無く、複数の電源電圧の供給とリセット解除タイミングとのシーケンスを守ってリセットを行う。

【解決手段】供給ラインL1とリセット端子16との間においてエミッタを供給ラインL1に向けつつコレクタをリセット端子16に向けて介挿されたトランジスタTr1と、トランジスタTr1のベースとグランドとの間においてコレクタをトランジスタTr1のベースに向けつつエミッタをグランドに向けて介挿されたトランジスタTr2と、トランジスタTr1のコレクタとグランドとの間においてコレクタをトランジスタTr2のコレクタに向けつつエミッタをグランドに向けて介挿されたトランジスタTr3とを備える。

(もっと読む)

電子機器

【課題】瞬断等による従来見られた不具合発生を防止する。

【解決手段】リセット端子を備えるメインICと、リセット端子に接続された追加回路とを備え、追加回路は、メインICへ供給される電源電圧を入力する第1入力端子と、メインICが稼働状態にあるときにメインICから出力される制御信号を入力する第2入力端子と、第2入力端子からの制御信号の入力があり且つ第1入力端子における電源電圧のレベルが上記所定レベルより高い所定のしきい値を下回ったときにオン状態となるスイッチ素子とを備え、スイッチ素子がオン状態となったときにリセット端子にリセット信号を与え、メインICは、リセット端子にリセット信号が与えられたときにリセット状態へ移行する。

(もっと読む)

選択可能閾値リセット回路

【課題】低電圧試験のためのリセット回路及び方法を提供する。

【解決手段】低電圧試験回路125と、システム100および200と、集積回路パッケージ104および204における回路127の低電圧試験を実行する方法が、電源電圧の一部分である電圧を生成する電圧分割ラダー320、一部分を基準電圧と比較する比較器310、電圧分割ラダーのトポロジーを制御し、それによって一部分の値を変更するスイッチ350を含む、選択可能閾値リセット回路125を含み、スイッチは製品試験装置102および202からの信号によって制御され、信号は、選択可能閾値リセット回路のリセット閾値を標準リセット閾値未満に低減されるようにして、標準リセット閾値未満の電源電圧で回路を試験することを可能にする。

(もっと読む)

情報処理装置

【課題】情報処理装置において省電力化を図る。

【解決手段】本発明に係る情報処理装置1は、リセット時間よりも短い設定時間であって、動作状態毎に異なる設定時間の値を記憶し、変移した動作状態に対応する設定時間を周期としてタイマ初期化信号を出力するタイマ初期化処理と、再起動開始信号の入力に応じて再起動する再起動処理を実行する制御部11と、タイマ初期化信号が入力されてからの経過時間を計時するとともに、経過時間がリセット時間に至った場合、制御部に対して再起動開始信号を出力する監視部12と、を備えたことを特徴とするものである。

(もっと読む)

コンピュータのリセット方法およびコンピュータ

【課題】筐体を開放しないでRTCメモリをリセットする。

【解決手段】カレンダー時刻およびBIOSの設定情報を記憶するRTCメモリ25には、バックアップ電池51から電力が供給される。コンピュータがパワー・オフ状態のときにパワー・コントローラ31には電力が供給される。パワー・オフ状態においてキーボード63のFnキーおよびパワー・ボタン61を同時に押下すると、パワー・コントローラ31はリセット・スイッチ91を所定時間だけオフにしその後オンにする。その後、パワー・コントローラ31は自らに供給されている電力を一旦停止してから復帰させる。

(もっと読む)

シリアル通信装置及びその制御方法

【課題】内部回路との間で所定の同期クロックを用いて通信を行う送受信回路と、入力される基準クロックに基づいて上記同期クロックを発生するPLL回路とを備えたインターフェース回路を備えたシリアル通信装置において、インターフェース回路及び内部回路の誤動作を防止する

【解決手段】遅延回路5は、基準クロックREFCLKの周波数が100MHzで安定した後に発生されるリセット信号PERST#を、所定の遅延時間Δtだけ遅延させて内部リセット信号PERST2を発生し、リンクコントローラ31に出力する。PHY回路2は、リセット信号PERST#に応答してリセットされ、リンクコントローラ31は、内部リセット信号PERST2に応答してリセットされる。また、遅延時間Δtは、PLL回路23の回路仕様に基づいて予め計算されたロックアップ時間より長く設定される。

(もっと読む)

リセット装置

【課題】 従来より安価で簡単な回路構成で、確実に制御手段にリセット動作を実行させることができるリセット装置を提供する。

【解決手段】 制御手段にリセット信号を供給するリセット装置であって、ユーザによって操作可能である第1操作部及び第2操作部と、該第1操作部及び第2操作部が所定時間以上継続して同時に操作されているか否かを検出する検出部と、リセット信号を該制御手段に供給するリセット信号生成部とを備え、該第1操作部及び第2操作部が所定時間以上継続して同時に操作され、その後、同時に操作されなくなったときに、該リセット信号生成部がリセット信号を該制御手段に供給する。

(もっと読む)

携帯情報端末

【課題】 リセット動作を制限する。

【解決手段】 携帯電話1は、アプリケーションプログラムを実行可能なCPU21と、電源をオンした状態とオフした状態とに切換える指示を受付けるための電源スイッチ14Bと、電源スイッチ14Bが所定時間閉ざされると、CPU21を再起動させるためのリセット信号を出力するリセット検出回路20とを備え、CPU21は、リセット可能な状態とリセット不可能な状態とのいずれかを示す状態信号SL1を出力し、リセット検出回路20は、状態信号SL1がリセット可能な状態を示すこことを条件に、ハイの信号S4(リセット信号)をリセット回路41に出力する論理積素子27を含む。リセット回路41は、リセット検出回路20からハイの信号S4(リセット信号)が入力されると、CPU21にローの信号SL5(リセット信号)を出力する。

(もっと読む)

電子機器及びプログラム

【課題】ウォッチドックタイマのタイムアウトによる再起動が不用意に繰り返されてしまうことを防止することが可能な電子機器及びプログラムを提供する。

【解決手段】自己の装置の起動時に計時を開始する計時手段と、前記計時手段のカウント値が所定のタイムアウト値に到達するタイムアウト時に、自己の装置の再起動を行うリブート手段と、前記タイムアウト値よりも小さい一定の間隔毎に、前記計時手段のカウント値をリセットするカウント値リセット手段と、前記リブート手段により連続的に行われた再起動の回数を集計する集計手段と、前記集計手段による集計結果が所定の回数を上回った場合に、前記計時手段による計時を停止させた状態で起動を行う制御手段と、を備える。

(もっと読む)

電子機器

【課題】電子機器において、その回路規模をより小さくするとともに信号配線をより簡単にするための技術を提供する。

【解決手段】電子機器は、CPUと、当該CPUとリセット信号線で接続された特定の処理を行う第1処理回路とを備える。省電力モード時には、第1処理回路の電源はオフされる。ここで、リセット信号線はプルダウンされており、第1処理回路の電源がオフである場合に、CPUはリセット状態になる。

(もっと読む)

半導体集積装置およびその制御方法

【課題】複数の機能ブロックのうち1以上を選択し、当該選択した機能ブロックをリセットする半導体集積装置および半導体集積装置の制御方法を提供する。

【解決手段】本発明にかかる半導体集積回路20は、クロック信号35及びリセット信号36が供給されることでリセットされる機能ブロック24と、機能ブロック24をリセットするリセット信号36を出力するリセット信号出力部21と、機能ブロック24に供給するクロック信号35を停止するクロックマスク回路23と、クロックマスク回路23を制御するクロックマスク制御回路22を有する。

(もっと読む)

集積回路

【課題】 クロックゲーテイングの同期リセット型同期FFを用いたASICのパワーオン時や、ASICのリセット端子を用いたスタンバイ時のローノイズ化、低昇温化、省電力に関する。

【解決手段】 同期リセットFF回路や、クロックドゲートで制御される同期リセットFF回路で設計された同期リセットFF回路で構成された回路を含むASICで、ASICの外部から外部リセット信号が入力できるリセット端子を具備し、少なくともそのリセット端子には、パワーオン時にリセットICによるパワーオンリセット信号が入力され、その外部リセット信号がアクテブ状態から非アクテブ状態に遷移するタイミングを基準として、ASIC内部の回路(リセット制御回路を除く)を初期化するためのリセット信号を生成するリセット制御回路を具備する。

(もっと読む)

情報処理装置及び情報処理方法

【課題】エラー状態になった記憶装置を正常な状態に復帰させることができる情報処理装置及び情報処理方法を提供する。

【解決手段】液晶表示装置11は、メモリーカード20から画像ファイルの読み出し又は転送を行なう旨の制御指令を出力する画像再生制御装置13を備えている。この画像再生制御装置13は、制御指令が出力されてからの経過時間が予め設定された経過時間閾値以上になっても、制御指令に対する応答信号を出力しない、又は制御指令に対応した処理を完了しないエラー状態の記憶装置が検出された場合に、該エラー状態の記憶装置に対してリセット信号を出力する。

(もっと読む)

ストレージシステム、ストレージ管理装置、ストレージ管理方法

【課題】 初期化処理のタイムアウトとなる時間を延長することで、記憶装置を搭載した搭載装置の停電を検出することができるストレージ管理装置を提供する。

【解決手段】 記憶装置を少なくとも一つ搭載する搭載装置が複数カスケード接続されることで成る、複数のループのうちの少なくとも一つのループで、初期化処理が実行された場合、初期化処理が完了しているかを判定する初期化完了判定部1と、初期化完了判定部1による判定結果が否である場合、初期化処理の実行時間が設定時間を経過しているか否かを判定する初期化時間判定部2と、初期化時間判定部2による判定結果が否であり、かつ、初期化処理が複数のループで実行されている場合、設定時間を延長する時間延長部と、を備えるストレージ管理装置を提供する。

(もっと読む)

制御装置

【課題】FPGA等の書換え可能なデバイスの初期化処理完了タイミングと、制御部のリセット解除タイミングのずれによる誤動作を防止することができる制御装置を提供する。

【解決手段】メインスイッチSW1がオンされると、FPGA2、電源監視IC5にバッテリ電源電圧BATTが供給され、FPGA2はコンフィグレーションROM3からコンフィグレーション情報を読み出して、初期化処理を開始する。一方、イグニッションスイッチ信号IGSWがメインリレー回路6に入力されると、電源監視IC5がCPU1に電源電圧Vccを供給するとともに、一定時間後にリセット解除信号RESETをAND回路8に出力し、FPGA2がコンフィグ完了信号を出力した後、AND回路8がCPU1のリセット解除信号入力端子にオン信号を入力する。

(もっと読む)

計算機初期化システム、及び計算機初期化システムに用いられるメディア入力装置

【課題】計算機のハードウエア構成及びソフトウエア構成の相違に柔軟に対応でき、かつ、簡便な計算機初期化システムに用いられるメディア入力装置を提供する。

【解決手段】本発明のメディア入力装置6は、初期化対象計算機の初期化データを生成する初期化データサーバに通信手段を介して結合され、初期化データサーバから転送される初期化データを通信バッファ95に格納する初期化通信部94と、初期化対象計算機に通信手段を介して結合され、初期化対象計算機の初期化データを取得する要求に応じて、通信バッファ内の初期化データを読み出す初期化プログラム84を初期化対象計算機に転送する計算機インターフェース82とを有して構成される。

(もっと読む)

遅延回路および半導体集積回路

【課題】 遅延時間が変更可能な不揮発性の遅延回路を提供する。

【解決手段】 強誘電体キャパシタの一端は、バッファ回路に接続される。強誘電体キャパシタの他端には、第1スイッチ回路を介して第1電圧が供給され、あるいは第2スイッチ回路を介して第1電圧と反対の論理レベルに対応する第2電圧が供給される。リセット制御回路は、リセット期間にバッファ回路に信号を出力することで強誘電体キャパシタの一端に第1電圧を与えるとともに、第1スイッチ回路をオフし、第2スイッチ回路をオンする第1スイッチ制御信号を出力する。また、リセット制御回路は、通常動作期間に第1スイッチ回路をオンし、第2スイッチ回路をオフする第2スイッチ制御信号を出力する。リセット期間に設定された分極値は電源がオフしても保持されるため、遅延時間が変更可能な不揮発性の遅延回路を実現できる。

(もっと読む)

電子制御装置

【課題】通信モジュールに対する初期化処理を実施しても初期化処理以外の制御処理の遅れを防止する電子制御装置を提供する。

【解決手段】ECU10は、エンジンスタート時、および異常発生時のECU10の再起動時等において、通信ソフト20により、通信モジュール30に対する初期化処理を複数回に分けて実施する。例えば、ECU10は、通信ドライバ60の送受信キュー62、コントローラ50のメッセージボックス52、コントローラ50のレジスタ54に初期値を書き込んで初期化するとともに、トランシーバ40の端子42を初期設定する。さらにECU10は、コントローラ50のレジスタ54に対して所定データを書き込み、書き込んだ所定データの値とレジスタ54から読み出した値とが一致するかを判定する動作確認処理を実施する。ECU10は、複数回に分割された各回の初期化処理が終了すると、初期化処理以外の車両制御を実施する。

(もっと読む)

1 - 20 / 50

[ Back to top ]