Fターム[5B061FF02]の内容

バス制御 (3,799) | バスアダプタ(バス結合装置) (397) | バス間接続用バスアダプタの作用効果 (343) | バス幅変換のため (52)

Fターム[5B061FF02]の下位に属するFターム

Fターム[5B061FF02]に分類される特許

1 - 20 / 49

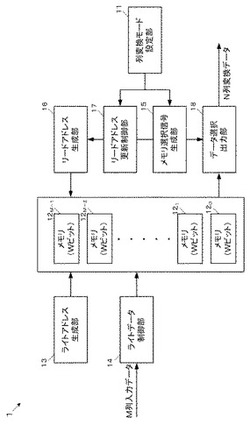

列変換回路、および、列変換方法

【課題】論理回路の増大を抑制しながら列変換モードを拡張可能な列変換回路を提供すること。

【解決手段】変換後の列数Nを設定する列変換モード設定部11と、M個のメモリ12と、各メモリ12におけるライトアドレスを生成するとともに次のM列入力データの書込位置を示すようライトアドレスを更新するライトアドレス生成部13と、M列入力データの各ビットを、各メモリ12のライトアドレスの位置に書き込むライトデータ制御部14と、M個のメモリ12のうちN個を示す選択信号を生成するとともに次の他のN個を示すよう選択信号を更新する選択信号生成部15と、選択信号が示すN個の各メモリ12におけるリードアドレスを生成するリードアドレス生成部16と、リードアドレス生成部16を制御するリードアドレス更新制御部17と、選択信号およびリードアドレスに従いM個のメモリ12からN列データを読み出すデータ選択出力部18とを備える。

(もっと読む)

電子機器

【課題】スペクトラム拡散クロックに基づき動作する第1の回路ユニットとPLLクロックに基づき動作する第2の回路ユニットとの間で通信を行う場合,クロック乗り換え処理によるデータ通信のレイテンシを小さくし,単位時間当たりのデータ通信量の低下を防止する電子機器を提供する。

【解決手段】検出部5は,スペクトラム拡散クロックの周波数とPLLクロックの周波数との周波数差が第1の所定範囲内か否かを検出する。バスブリッジ部3は,周波数差が第1の所定範囲内の場合に,第1の回路ユニット1と第2の回路ユニット2との間で同期通信を実行し,周波数差が第1の所定範囲外の場合に,第1の回路ユニット1と第2の回路ユニット2との間で非同期通信を実行する。

(もっと読む)

データ転送装置

【課題】バイト単位のデータ転送を実現しようとするとFIFO等の使用するハードウェアの規模が大きくなる。

【解決手段】ライト用バイトイネーブル保持回路10は、FIFO40の最新のライトアドレスに書き込まれているデータのバイトイネーブルを保持し、リード用バイトイネーブル保持回路20は、1タイミング前のライトデータのバイトイネーブルまたは該バイトイネーブルと1タイミング前の自保持内容との論理和または1タイミング前の自保持内容を保持する。バイト読出し判定フラグ50は、リードデータのバイトイネーブルを解読してFIFOの1ワード分の全バイト読出しであるか否かを示す。否のとき、セレクタ503は、回路20の保持内容、全バイト読出しであるときは回路10が保持しているバイトイネーブルを選択して、リードデータのバイトイネーブルとする。

(もっと読む)

リードアクセス制御装置およびその制御方法

【課題】 回路規模を減らしつつ、読み出し対象に対するリードアクセスを正確に行えるようにする。

【解決手段】 読み出し対象であるレジスタ201から現在のリードアクセスによって出力されたデータである現アドレスのデータを、必要に応じて補正してエンジンCPU12へ出力する出力データ補正部102と、それから送られてくる出力データを、次の出力データが出力データ補正部102から送られてくるまで保持する出力データ保持部103と、レジスタ201からの1リードアクセス前にアクセスされたアドレスのデータである1アクセス前データと出力データ保持部103からのデータである保持データとを比較し、その比較結果に基づいて桁上がりの有無を判定する桁上がり判定部104とを設け、出力データ補正部102は、桁上がり判定部104によって桁上がりが有ると判定された場合に、上記現アドレスのデータに対して1デクリメントを行う。

(もっと読む)

バスシステム

【課題】複数の異なるバスプロトコルのスレーブバスを有し、簡易な構成によってマスタ装置からスレーブ装置へのアクセスを分割することのできるバスシステムを提供する。

【解決手段】複数個のスレーブバス60〜63は、それぞれが、少なくとも1つのスレーブと接続され、互いに異なるバスプロトコルを有する。複数個のスレーブIF12,14,16,18は、それぞれが、マスタバス58、および1つのスレーブバスに接続される。バス制御部8は、アドレスマップに基づいて、アクセス対象のスレーブのアクセスビット幅を特定する。バス制御部8は、マスタ2,4,6からのアクセス要求ビット幅がアクセス対象のスレーブのアクセスビット幅よりも大きいか否かを判断する。バス制御部8は、大きい場合には、複数回に分けてスレーブIF12,14,16,18を介してアクセス対象のスレーブにアクセスする。

(もっと読む)

入出力制御装置、及び情報処理装置

【課題】未使用の記憶領域の生成を防ぐ

【解決手段】第1処理装置、第2処理装置、第1記憶装置、及び第2記憶装置に対してデータを入出力する入出力制御装置であって、第1処理装置が出力する第1データを分割するデータ分割部と、分割した第1データを、第1記憶装置及び第2記憶装置にそれぞれ格納するとともに、第2処理装置が出力し且つ第1データよりビット数が少ない第2データを、第1記憶装置及び第2記憶装置の何れか1つに格納する格納制御部と、を備える入出力制御装置が提供される。

(もっと読む)

データ通信制御装置

【課題】バスの動作タイミングを適切に調整することができるデータ通信制御装置の提供。

【解決手段】本発明によるデータ通信制御装置は、CPUコア10と周辺機器60の間にバスブリッジ20を備え、前記CPUコアと前記バスブリッジの間は、高速バス70で接続され、前記周辺機器と前記バスブリッジの間は、低速バス72で接続され、前記周辺機器から前記バスブリッジを介して前記CPUコアへデータを送信する際に、前記周辺機器から前記バスブリッジへの前記低速バスによるデータの送信方法を、シリアル通信とパラレル通信の間で動的又は静的に切り換える切換制御部30,62Aを備えることを特徴とする。

(もっと読む)

デバイスのための複数プロトコル、多重データ転送速度、自動速度交渉アーキテクチャ

ローカルデバイスにおいて使用するためのインターフェースは、少なくとも3つのデータ転送速度にプログラマブルに構成可能な送信機部分と、少なくとも3つのデータ転送速度にプログラマブルに構成可能な受信機部分と、少なくとも3つのデータ転送速度のうちの最も可用性のある1つである単一のデータ転送速度において、遠隔デバイスと通信するために、送信機部分および受信機部分を構成するように、送信機部分および受信機部分に動作可能に接続されている自動速度交渉モジュールとを含む。データ転送速度は、送信機データパス幅および受信機データパス幅を調節し、送信機データパスおよび受信機データパスの周波数を調節し、オーバーサンプリングすることによって、調節することができる。  (もっと読む)

(もっと読む)

8ビットベースのデータ処理システム

【課題】ホストとクライアントの間を、ホスト側のOS進化などで実質的にスポイルされない形で結ぶ。

【解決手段】一実施の形態に係るデータ処理システムは、8ビット以上の外部データを扱うホスト100を、8ビット単位の内部データおよび8ビットの内部アドレスを用いて1以上のクライアント600につなぐ構成を持つ。このシステムにおいて、接続部500を介して変換モジュール300Sに複数のクライアント600が接続される場合には、これら複数クライアントのうち、前記内部アドレスにより特定された1つ(ターゲットI/Oボード)が、変換モジュール300Sと情報交換できるように構成される。ここで、ホスト100は、変換モジュール300Sに対して、前記内部アドレスの8ビット空間の1箇所を指定し、指定したアドレス空間に対してデータの送受を行う。指定されたアドレス空間に接続されたターゲットI/Oボードは、受け取ったデータに対して自身の処理を行う。

(もっと読む)

帯域幅同期化回路及び帯域幅同期化方法とこれを含むデータプロセッシングシステム

【課題】高周波数狭帯域CPUと低周波数広帯域バスとの間の帯域幅ボトルネックを解消することができる帯域幅同期化回路及び帯域幅同期化方法とこれを含むデータプロセッシングシステムを提供する。

【解決手段】帯域幅同期化回路はアップサイザー及びシンクダウン部を含む。アップサイザーは第1クロックによって作動するシンクパッカー及びシンクアンパッカーを含む。シンクダウン部はアップサイザーと接続され、第1クロックの周波数より低い周波数の第2クロックに応答してアップサイザーのデータに対してシンクダウン動作を実行する。

(もっと読む)

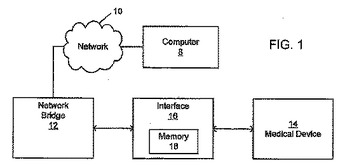

医療デバイスとネットワークとの間の通信のためのインターフェースデバイス

本発明は、医療デバイスとコンピュータシステムとの間の通信のためのインターフェースデバイスおよび方法に関する。いくつかの実施形態では、インターフェースデバイスは、変換デバイスおよび/またはプロセッサ送受信機と、変換デバイスと電気通信するメモリとを備え、メモリは、変換デバイスおよび/またはプロセッサ送受信機に医療デバイスとの通信方法を命令するためのデータを含む。一実施形態において、プロセッサ送受信機は、マイクロコントローラを備える。  (もっと読む)

(もっと読む)

コンピュータシステム

【課題】SATAのデバイスとPATAのホストとをPATA/SATA変換チップを用いて接続する際に、手動でのBIOS設定を行わなくとも、PATAバスでの転送速度がPATA/SATA変換チップが本来発揮可能な転送速度よりも小さくなることを防ぐ。

【解決手段】G経路を介して接続されたホストモードのPATA/SATA変換チップ31とデバイスモードのPATA/SATA変換チップ32とに接続されたマイコン回路33がIdentifyコマンドを出力し、返信を受信したら、PATA転送能力が最高速度値に設定されたIdentifyDeviceデータをPATA/SATA変換チップ32に出力する。PATA/SATA変換チップ32は、受信したIdentifyDeviceデータのPATA転送速度値と自らのPATAバス側の転送速度値とを比較し、その値が小さい方をPATAバス側の転送速度値としてマイコン回路33に設定させる。

(もっと読む)

メモリデバイス、メモリデバイス制御装置

【課題】各バス、ホストPC、メモリデバイスの特性に合わせて最適な動作モードで動作可能とすることができる。

【解決手段】メモリデバイスが接続されたことを認識した時に、メモリデバイスに対してデバイス情報を要求するデバイス情報要求部と、デバイス情報要求部で取得したデバイス情報に基づき、メモリデバイスの拡張機能を有効化する拡張機能有効化部とを備えている。メモリデバイス制御装置は、メモリデバイスにおける拡張機能を用いてメモリデバイスへアクセスを行う。

(もっと読む)

マルチプレックスバスを有するバスシステム

【課題】データ信号やアドレス信号の構成ビット数が多くても、それら信号を伝送するマルチプレックスバスの構成伝送線数を少なくして、マルチプレックスバス内の構成伝送線の同長配線性を高めて、それにより、マルチプレックスバス接続距離が伸長しても、また、バスクロックが高速化しても、そのことによる動作上への影響を軽減して、信頼性の高いバスシステムを構築する。

【解決手段】バス幅構成kビット(2mと2nの共通約数)のマルチプレックスバス内において、2mビット構成のアドレス信号をパラレル伝送ビット数をkビットとして(2m/k)バスサイクルに時分割してシリアル伝送し、2nビット構成のデータ信号をパラレル伝送ビット数をkとして(2n/k)バスサイクルに時分割してシリアル伝送するバスシステム。

(もっと読む)

バススイッチ,電子機器及びデータ転送方法

【課題】シリアル転送インターフェースのデータ転送性能を容易に向上させることができるバススイッチ,電子機器及びデータ転送方法を提供することを目的とする。

【解決手段】メモリ制御手段103と、複数の処理制御手段104,106との間に設けられたシリアル転送インターフェースのバススイッチ107であって、処理制御手段104,106との間で行うデータ送受信を制御する第一のデータ送受信手段202,203と、メモリ制御手段103との間で行うデータ送受信を制御する第二のデータ送受信手段201と、第一のデータ送受信手段202,203と第二のデータ送受信手段201との接続を切り替える切替手段とを有し、第一のデータ送受信手段202,203は、処理制御手段104,106からの1回の命令によりメモリ102との間で転送可能なデータ量以上の容量のバッファ204,205を有することにより上記課題を解決する。

(もっと読む)

直交変換回路

【課題】複数種類のビット幅のデータを、効率的に直交変換して転送することのできる直交変換回路を提供する。

【解決手段】4面の2ポート直交変換メモリ(TM0−TM3)を設ける。これらの直交変換メモリに対し、システム側との間のデータ転送用のデータバス(50)と、主演算回路側とのデータ転送を行なうデータバス(55)を設ける。システムバス側制御部(60)において、これらの直交変換メモリとの間でバス接続およびアドレスシーケンスをデータビット幅に応じて更新して、順次データを転送する。主演算ブロック側制御部(65)において、これらの直交変換メモリから、データビット幅に応じてバス接続を切換え、またデータ配列を64ビットバッファ(68)を用いて調整して、偶数データおよび奇数データの組を、主演算ブロックとの間で転送する。

(もっと読む)

バスシステム

【課題】データの転送効率を向上させたバスシステムを提供する。

【解決手段】データ幅が32ビットのマスタ10A,10Bと、マスタ10A,10Bが接続されるマスタ側バス20A,20Bと、データ幅が64ビットのスレーブ50と、スレーブ50が接続されるスレーブ側バス40と、マスタ側バス20A,20Bとスレーブ側バス40が接続されるバス調停器30とを備える。そのバス調停器30は、アドレス生成器31によって、マスタ10AのアドレスAに対応したスレーブ50のアドレスCAを生成するとともに、マスタ10BのアドレスBに対応したスレーブ50のアドレスCBを生成し、スレーブ50に対して、データA,BをそれらアドレスCA,CBに書き込む。

(もっと読む)

バス制御装置

【課題】配線混雑によりチップ面積が大きくなるのを防止するようにバスを構成して制御するバス制御装置を提供すること。

【解決手段】調停部21は、複数のマスタ1〜N(1−1〜1−N)からのアクセス要求を調停する。スレーブアクセス制御部23は、スレーブ4に対して調停部21によって調停されたアクセスを行なう。そして、バス制御装置2が片方向のリードバスRDとライトバスWD1〜WDNとによって複数のマスタ1〜N(1−1〜1−N)と接続され、ライトバスWD1〜WDNのバス幅がリードバスRDのバス幅よりも狭くなるように構成される。したがって、配線混雑によりチップ面積が大きくなるのを防止することが可能になるという効果がある。

(もっと読む)

データ転送制御装置及び電子機器

【課題】パラレルATAとシリアルATAのバスブリッジ機能を実現しながらホストとシリアルATAデバイスとの間の転送の整合性についても適正に維持する。

【解決手段】データ転送制御装置はPATAI/F10とSATAI/F50とシーケンスコントローラ30を含む。PATAI/F10はタスクファイル・レジスタTFR12を有する。SATAI/F50はホスト2によりアイデンティファイ・デバイス・コマンドが発行された場合に、それに対応するレジスタFISをデバイス5に送信する。シーケンスコントローラ30は、アイデンティファイ・デバイス・コマンドの返値であるアイデンティファイ・デバイス情報が設定されたデータFISを受信した場合に、アイデンティファイ・デバイス情報の書き換え処理を行う。

(もっと読む)

データ転送制御装置及び電子機器

【課題】パラレルATAとシリアルATAのバスブリッジ機能を実現しながら初期化シーケンス処理についても適正に実現する。

【解決手段】データ転送制御装置は、PATAバスに接続されるPATAI/F10と、SATAバスに接続されるSATAI/F50と、転送シーケンス制御を行うシーケンスコントローラ30を含む。シーケンスコントローラ30は、SATAのデバイス4に代わって初期化シーケンス管理を代行する初期化シーケンス管理部34を含む。初期化シーケンス管理部34は、マスタ・スレーブ設定端子(CSEL)によりデータ転送制御装置がマスタ側に設定された場合には、ハードリセット後にスレーブ検知処理と自己診断処理を行い、マスタ・スレーブ設定端子によりデータ転送制御装置がスレーブ側に設定された場合には、ハードリセット後にスレーブ検知信号、自己診断信号の制御を行う。

(もっと読む)

1 - 20 / 49

[ Back to top ]