Fターム[5B062CC01]の内容

マイクロコンピュータ (2,258) | 種類 (331) | シングルチップマイクロコンピュータ (204)

Fターム[5B062CC01]の下位に属するFターム

命令用メモリとデータ用メモリとが分離 (6)

プログラムメモリがPROM (23)

ワンチップマルチ (58)

特定用途向け (31)

Fターム[5B062CC01]に分類される特許

1 - 20 / 86

電力の島を使用した集積回路での電力の管理

情報処理装置、データ復帰方法

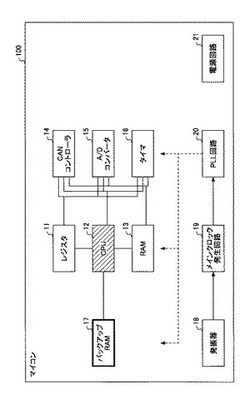

【課題】製造プロセスの影響を抑制してスリープ時の消費電力を低減できる情報処理装置を提供すること。

【解決手段】プログラムを実行する第1の動作モード中に作業用記憶手段に作成されたデータを第2の動作モード中に保持する退避データ記憶手段を有する情報処理装置100であって、第2の動作モードの動作クロックと、第2の動作モードの動作クロックよりも大きい第1の動作モードの動作クロックを生成するクロック生成手段19,20と、第2の動作モードから復帰する際、前記クロック生成手段が第1の動作モードの動作クロックに上昇させる前に、当該情報処理装置の状態を示す情報処理装置ステータスデータを前記退避データ記憶手段から作業用記憶手段に復帰させる第1のデータ復帰手段41と、前記クロック生成手段が第1の動作モードの動作クロックに上昇させた後、第1の動作モード中に作成されたデータを退避データ記憶手段から作業用記憶手段に復帰させる第2のデータ復帰手段46と、を有することを特徴とする。

(もっと読む)

半導体装置および半導体装置の制御方法並びに半導体装置の設計支援方法

【課題】本発明の課題は、組み込みシステムのアーキテクチャに左右されることなく、DVFSの実行に必要なサイクル数を容易に取得することである。

【解決手段】ファームウェア(21)は、サイクル数概算ルーチン(213)と、動作電圧・周波数算出ルーチン(213)とを有する。サイクル数概算ルーチンは、サイクル数概算関数を備える。サイクル数概算関数は、ユーザ回路(6)の処理内容を決定づける属性パラメータの入力でタスクのサイクル数を概算する。動作電圧・周波数算出ルーチンは、サイクル数概算ルーチンの実行によって得られたサイクル数に基づいて、ユーザ回路(6)の目標動作電圧・周波数を算出する。

(もっと読む)

車載用ECU

【課題】内部のマイコンの動作不要時における消費電力を最小限に抑えた車載用ECUを得る。

【解決手段】車載用ECU10は、間欠動作モード設定時において、マイコン1の動作不要時には電源入力部VCCへの動作電源V4の供給を完全に停止させている。マイコン1は、間欠動作モードを指示するセット状態の判別用データCDを書込む第1の書込み処理、及び通常モードを指示するクリア状態の判別用データCDを書込む第2の書込み処理を共に内部の不揮発性RAM15に対する個別書込み動作によって行っている。また、不揮発性RAM15における判別用データCDの格納ブロックに対する一括消去動作を、マイコン1が通常モード設定時の定周期処理として実行する。

(もっと読む)

入出力ポート制御装置及びそれを含む集積回路装置

【課題】 各ポートに割り当てられる各機能の特性に応じた割り当てを実現出来る装置を提供する。

【解決手段】 同一の機能を有する複数の1次機能処理部と、それぞれが異なる機能を有する複数の2次機能処理部と、1次機能処理部或いは2次機能処理部の出力データ、或いは前記各処理部に対する入力データが選択的に接続されるポートを備え、前記ポートに出力端子が接続される複数の第1のセレクタ群の一方の入力部には、1次処機能部の各出力処理部接続され、前記複数の第1のセレクタ群の他方の入力部には、2次機能処理部の出力処理部が接続され、前記ポートに入力端子が接続される複数の第2セレクタ群の各入力端子には前記ポートの出力が1対1に接続され、前記第2セレクタ群の各出力が、それぞれ前記2次処理機能部の入力処理部に接続される。

(もっと読む)

マイクロコンピュータ

【課題】ソフトウエア処理によらずに、かつ短時間でAD変換結果の頻度分布を高速に得ることができるマイクロコンピュータを提供する。

【解決手段】AD変換器1は、センサによる検出信号をデジタル信号に変換する。複数のレジスタ2_1〜2_nは、互いに異なるデータを保持する。複数の比較器3_1〜3_nのそれぞれが、AD変換器1の出力値と、複数のレジスタ2_1〜2_nのうち対応するレジスタ内のデータとを比較する。複数のカウンタ4_1〜4_nのそれぞれが、複数個の比較器3_1〜3_nのうちの対応する比較器での比較結果が一致した回数をカウントする。

(もっと読む)

マイクロコンピュータ

【課題】リソースでの無駄な消費電力を削減することができるマイクロコンピュータを提供することを目的とする。

【解決手段】外部から電源を供給されるマイクロコンピュータにおいて,それぞれの所定の機能を有し,外部から供給される前記電源の起動時に電源が供給されない複数のリソースと,前記複数のリソースにバスを介して接続され,前記リソースに前記バスを介してアクセス信号を供給する制御ユニットと,前記複数のリソースにそれぞれ設けられ,電源起動信号に応答して外部から供給される前記電源から対応するリソースにリソース内電源を供給する複数のリソース内電源供給部と,前記複数のリソースにそれぞれ設けられ,前記バスを介して供給されるアクセス信号が対応するリソース宛か否かを検知し,前記アクセス信号が対応するリソース宛の場合に前記電源起動信号を対応するリソース内電源供給部に出力できる電源制御部とを有する。

(もっと読む)

半導体集積回路及び半導体集積回路の動作制御方法

【課題】温度が高くなりすぎたりあるいは低くなりすぎたりする発振状態となって、半導体集積回路が誤動作、動作停止等することを防止する。

【解決手段】実施形態によれば、半導体集積回路1は、回路部の温度又は動作速度に基づいて、温度が安定するように、回路部の制御パラメータを調整して、フィードバック制御を実行する制御部と、温度の時系列データである第1の履歴データと、制御パラメータの時系列データである第2の履歴データとを含む履歴データを格納する履歴レジスタ17と、履歴データからフィードバック制御の有効性を判定する有効性判定部24とを有する。

(もっと読む)

ディジタル・パワー・スロットルを備えたマイクロプロセッサ

【課題】 プロセッサ内の電力消費を調整するためのディジタルベースのメカニズムを提供する。

【解決手段】 本発明は、プロセッサ内の電力消費を調整するためのディジタルベースのメカニズムを提供する。このプロセッサは、1つまたは複数の機能ユニットと、プロセッサの機能ユニットの活動状態を監視して、プロセッサの電力消費を推定するディジタル・スロットルとを含む。このディジタル・スロットルの一実施形態は、1つまたは複数のゲート・ユニットと、1つの監視回路(320)と、1つのスロットル回路(330)とを含む。各ゲート・ユニットは、プロセッサの機能ユニットへの電力送付を制御し、その関連機能ユニットの活動状態を示す信号を出力する。監視回路は、信号から推定電力消費レベルを決定し、その推定電力消費としきい電力レベルを比較する。推定電力消費レベルがしきい電力レベルを超える場合、スロットル回路はプロセッサ内の命令フローを調整する。

(もっと読む)

クリティカルパスに基づく解析のための性能モニタリングアーキテクチャ強化

【課題】マイクロアーキテクチャの性能をモニタリングし、そのモニタリングされた性能に基づいてマイクロアーキテクチャをチューニングする方法及び装置を提供する。

【解決手段】シミュレーション、解析上の推論、リタイアメントプッシュアウト測定、全体実行時間、およびインスタンス当たりのイベントコストを決定する他の方法によって性能がモニタリングされる。インスタンス当たりのイベントコストに基づき、マイクロアーキテクチャおよび/または実行ソフトウェアは、性能を強化すべくチューニングされる。

(もっと読む)

データプロセッサ

【課題】データ処理の高速化とCPUの負担軽減を実現するイベント応答制御技術を提供する。

【解決手段】データプロセッサは、命令を実行する中央処理装置(2)と、中央処理装置による制御を受ける第1乃至第3の内部回路とを有する。第1の内部回路は、第2の内部回路又は第3の内部回路から供給されるイベント信号に応答して中央処理装置に割り込み要求信号を出力する割込みコントローラ(13)である。第2の内部回路は、前記第1の内部回路又は前記第3の内部回路から供給されるイベント信号に応答して前記第3の内部回路に対する起動制御信号を出力するイベントリンクコントローラ(6)である。前記第3の内部回路は、複数の回路モジュールで構成され、前記中央処理装置と前記イベントリンクコントローラにより並列に制御されることが可能である。

(もっと読む)

マイクロコンピュータ及びデータ処理システム

【課題】マイクロコンピュータにおいてメモリアクセスコマンドの生成などの点でシリアルアクセスメモリに対するアクセスのオーバーヘッドを減らす。

【解決手段】 CPUが出力するアクセス要求に含まれるアドレス及びコマンドに基づいて、シリアルフラッシュメモリに、チップ選択信号及びクロック信号を供給し、前記クロック信号に同期してメモリアドレス及びメモリコマンドを出力してシリアルアクセスメモリのアクセス制御を行うシリアルメモリインタフェースコントローラ(60)をマイクロコンピュータに搭載し、このシリアルメモリインタフェースコントローラには、前記アクセス要求に応答するメモリアドレス及びメモリコマンドに基づくデータリードを完了したとき、そのリードデータの最後のメモリアドレスに続くアドレスへのリードアクセス要求以外のアクセス要求を検出するまで前記チップ選択信号の活性状態を維持する動作モードを採用する。

(もっと読む)

マイクロコントローラ及びその制御方法

【課題】消費電力の低減を可能にするとともに、プログラム開発の複雑化を低減する。

【解決手段】本発明に係るマイクロコントローラ100は、CPU103により指定されるアドレスが指定領域155の範囲内である場合、RAMアクセス動作を行い、当該アドレスが指定領域155に含まれない場合、フラッシュEEPROM101からプログラムを読み出すRAM制御部107を備える。RAM制御部107は、RAMアクセス動作として、バリッドビット171が無効状態を示す場合、フラッシュEEPROM101からプログラムを読み出し、読み出したプログラムをRAM102に格納するとともに、バリッドビット171を有効状態に変更し、バリッドビット171が有効状態を示す場合、RAM102に格納されているプログラムをCPU103へ出力する。

(もっと読む)

半導体装置

【課題】外部装置を駆動する駆動回路が形成されたチップの面積の増加を抑制することができる半導体装置を提供する。

【解決手段】フラッシュメモリ22がリード動作を実行する場合は、セレクタ26は、ロジック回路30から入力された選択信号SELに応じて基準電圧VREF1を選択する。VLCD昇圧回路28は、基準電圧VREF1を昇圧した駆動電圧VLCDをLCDパネルドライバ12に出力する。また、フラッシュメモリ22は、電源電圧VDDの供給のみでリード動作を実行する。プログラム動作またはイレース動作を実行する場合は、セレクタ26は、選択信号SELに応じて基準電圧VREF2を選択する。VLCD昇圧回路28は、基準電圧VREF2を昇圧した電圧VPPをフラッシュメモリ22に出力する。フラッシュメモリ22は、電圧VPPの供給を受け、プログラム動作またはイレース動作を実行する。

(もっと読む)

マイクロコンピュータ及びマイクロコンピュータの制御方法

【課題】CPUのモードの遷移に伴う消費電流を抑えること。

【解決手段】本発明にかかるマイクロコンピュータは、少なくとも通常動作モードと、クロック供給が停止されるスタンバイモードとからなる複数のモードを有するCPUと、CPUへ供給するクロックを生成するクロック生成回路と、CPUのモードを監視し、当該CPUのモードと、CPUへの割り込み要求の種類に応じてCPUが遷移すべきモードを決定し、決定したモードに応じてクロック生成回路を制御する制御回路と、を備える。

(もっと読む)

I/O拡張回路

【課題】 汎用ロジックICのシフトレジスタを使ってI/Oポートを拡張すると共に、動作速度を向上させることができるI/O拡張回路を提供する。

【解決手段】 ワンチップマイコン1と汎用シフトレジスタIC2との間で連続出力モードを持つクロック同期方式を用いて、ワンチップマイコン1から汎用シフトレジスタIC2にシリアルデータ、同期クロック、ラッチタイミングの信号を送信し、汎用シフトレジスタIC2では、汎用ロジックICをカスケード接続した構成であり、受信した同期クロック、ラッチタイミングの信号に従って、シリアルデータを複数ビットのパラレルデータに変換するI/O拡張回路である。

(もっと読む)

マイクロコンピュータ、半導体装置及びマイクロコンピュータ応用機器

【課題】一のアナログ回路で発生したノイズがアナログ電源経路を介して他のアナログ回路に回り込む虞を未然に抑制する

【解決手段】並列動作可能であって共通のアナログ電源端子に接続された複数個のアナログ回路(43〜46)に関し、相互に一のアナログ回路は、既にアナログ動作を開始している他のアナログ回路のアナログ動作サイクルにおいて当該一のアナログ回路のアナログ動作の開始を抑止する区間を特定するタイミング制御データに基づいてアナログ動作の開始が制御されるようにする。要するに、一のアナログ回路の動作が開始されたとき、その動作サイクルにおいて他のアナログ回路のアナログ動作の開始によって影響を受けるタイミングを予めタイミング制御データとして保持し、一のアナログ回路の動作の開始に同期してタイミング制御データを用いて他のアナログ回路のアナログ動作の開始を遅延させたり一時的に抑制したりする制御を行う。

(もっと読む)

シングルチップマイクロコンピュータ

【課題】ランダムアクセスによってリード・ライト可能な不揮発性記憶装置を、プログラム/データ兼用のメモリとして搭載した場合のセキュリティの向上を図るための技術を提供する。

【解決手段】予め設定されたプログラムに基づく演算処理を可能とするCPU(103)と、上記CPUによるランダムアクセスによってリード・ライト可能な不揮発性記憶装置(101)と、を含むシングルチップマイクロコンピュータ(100)である。上記不揮発性記憶装置は、記憶領域として上記プログラムが格納される不揮発保持領域とデータを格納可能な不揮発性保持無効化領域とを含む。リセット状態を示すリセット信号により、上記記憶領域のうち上記不揮発性保持無効化領域に対してライト動作を行うことで、上記不揮発性保持無効化領域のデータを消去する。

(もっと読む)

LSI,鉄道用フェールセーフLSI,電子装置,鉄道用電子装置

【課題】従来のフェールセーフLSIは、チップ内のプロセッサや比較回路の配置について言及されていたが、パッケージの信号ピン配置までは言及されていなかった。また、多様な周辺回路や高速な外部メモリへの対応も考慮されていなかった。

【解決手段】2つのプロセッサからの出力を照合して一本化された内部インタフェースを共通系内部バスに接続し、その共通系内部バスに複数の外部インタフェース回路を接続する。また、2つの系統に関する信号ピンをパッケージの対角に配置するともに、それらの間に共通系に関する信号ピンを配置するようにする。

(もっと読む)

半導体装置、マイクロコンピュータの制御方法

【課題】信頼性の高い統計多重制御が可能な統計多重装置を提供する

【解決手段】本発明によるマイクロコンピュータ10は、ステータスレジスタ5に設定された状態フラグ102に応じて、ユーザモードとプログラミングモードの一方を選択し、ユーザモードが選択された場合、不揮発性メモリ2内のユーザプログラムを実行し、プログラミングモードが選択された場合、不揮発性メモリ2へのユーザプログラムの書き込み又は消去を制御する書き込み用ファームウェア3を実行する。

(もっと読む)

1 - 20 / 86

[ Back to top ]