Fターム[5B062HH06]の内容

マイクロコンピュータ (2,258) | クロック、電源、リセット (407) | 低消費電力モード (100)

Fターム[5B062HH06]の下位に属するFターム

低消費電力モードからの復帰 (36)

Fターム[5B062HH06]に分類される特許

1 - 20 / 64

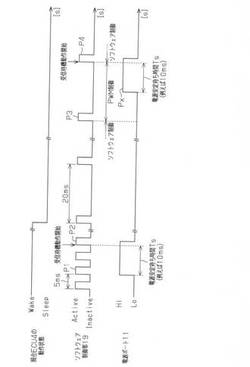

IC出力ポート切換制御装置

【課題】電源を省電力化することができるIC出力ポート制御装置を提供する。

【解決手段】ワイヤレスキーシステムの照合ECU4は、自身のメモリに記憶されたプログラムにて所定周期で動作するソフトウェア制御部19と、自身に元から備わるPWMリソースとを有する。照合ECU4のスリープ中、車両受信機が受信待機動作をとるパルスP4の1周期前のパルスP3で電源ポート11をソフトウェア制御からPWM制御に変更することにより、電源ポート11をPWM制御に切り換える。このため、PWM制御のパルスPxがHiレベルに立ち上がってからの時間が電源安定待ち時間Tsとして車両受信機に供給される。

(もっと読む)

車載用ECU

【課題】内部のマイコンの動作不要時における消費電力を最小限に抑えた車載用ECUを得る。

【解決手段】車載用ECU10は、間欠動作モード設定時において、マイコン1の動作不要時には電源入力部VCCへの動作電源V4の供給を完全に停止させている。マイコン1は、間欠動作モードを指示するセット状態の判別用データCDを書込む第1の書込み処理、及び通常モードを指示するクリア状態の判別用データCDを書込む第2の書込み処理を共に内部の不揮発性RAM15に対する個別書込み動作によって行っている。また、不揮発性RAM15における判別用データCDの格納ブロックに対する一括消去動作を、マイコン1が通常モード設定時の定周期処理として実行する。

(もっと読む)

半導体装置

【課題】スタンバイ状態時にSRAMにデータを保持できる電圧が与えられている場合に、パワーオンリセットがかからないようにすることができる半導体装置を提供する。

【解決手段】CPU5は、スタンバイ状態に遷移することを通知する。電源制御回路11は、スタンバイ状態時に、SRAM4における電力消費を低減させる。POR回路2は、外部電源電圧の値と、現在の状態がスタンバイ状態であるかに応じて、パワーオンリセット信号の活性化を制御する。

(もっと読む)

半導体集積回路及び半導体集積回路の動作制御方法

【課題】温度が高くなりすぎたりあるいは低くなりすぎたりする発振状態となって、半導体集積回路が誤動作、動作停止等することを防止する。

【解決手段】実施形態によれば、半導体集積回路1は、回路部の温度又は動作速度に基づいて、温度が安定するように、回路部の制御パラメータを調整して、フィードバック制御を実行する制御部と、温度の時系列データである第1の履歴データと、制御パラメータの時系列データである第2の履歴データとを含む履歴データを格納する履歴レジスタ17と、履歴データからフィードバック制御の有効性を判定する有効性判定部24とを有する。

(もっと読む)

異種計算機システム動作方法

【課題】異種計算機システムを動作させる方法を提供する。

【解決手段】1つ以上の高性能プロセッサ620と、高性能プロセッサ620のソフトウェアのタスク実行を支援するプロセッサ支援論理回路6410と、高性能プロセッサ620より少電力なハイパーバイザプロセッサ610を有し、ハイパーバイザプロセッサ610は、自身が処理するのに十分な処理能力を有するソフトウェアのタスクを実行し、高性能プロセッサ620を電力節約状態にするか、又は高性能プロセッサ620を電力節約状態から抜け出させて、自身が処理するのに不十分な処理能力を有するソフトウェアのタスクを実行させるか、又は高性能プロセッサ620とハイパーバイザプロセッサ610とが全てのプロセッサの結合された処理能力を必要とするソフトウェアのタスクを同時に実行する。

(もっと読む)

状態保持回路における状態保全性の検証

【課題】 本発明は、データ処理動作を行うよう構成されたデータ処理回路を備えたデータ処理装置を提供する。

【解決手段】 複数の状態保持回路がデータ処理回路の一部を形成し、これらの回路は、低電力モードに入ったデータ処理回路のそれぞれのノードにてそれぞれの状態値を保持するよう構成される。1以上のスキャンパスは、状態値がそれぞれのノードにスキャンインまたはアウトされてもよいよう、複数の状態保持回路を直列に接続する。複数のパリティ情報生成要素はスキャンパスに結合され、状態保持回路によってそれらそれぞれのノードにて保持されたそれぞれの状態値を示すパリティ情報を生成するよう構成される。複数のパリティ情報生成要素は、それぞれの状態値の一つが変化した場合にパリティパスの出力にて生成された出力パリティ値を反転するよう、1以上のパリティパスを提供し、状態保持回路によって保持された状態値の保全性の外部指示を提供するよう配置される。

(もっと読む)

デュアルパスマルチモード順次記憶素子

【課題】デュアルパスマルチモード順次記憶素子

【解決手段】本明細書では、デュアルパスマルチモード順次記憶素子(SSE)(10)が説明されている。一実施例では、デュアルパスマルチモードSSEは、第1(14)および第2(12)の順次記憶素子、データ入力、データ出力ならびに選択機構(16)を備えている。第1および第2の順次記憶素子(14、12)は、それぞれ、入力および出力を有する。データ入力は両方の順次記憶素子の入力に結合され、データを受け入れるように構成される。データ出力は両方の順次記憶素子の出力に結合され、データを出力するように構成される。選択機構(16)は、データ入力からのデータをデータ出力に渡すために、順次記憶素子のうちの1つを選択するように構成される。一実施例では、第1の順次記憶素子はパルストリガー式記憶素子(14)を備えており、第2の順次記憶素子はマスタースレーブ記憶素子(12)を備えている。

(もっと読む)

半導体集積回路装置およびその制御方法

【課題】確実にスリープモードに設定することが可能な半導体集積回路装置およびその制御方法を提供する。

【解決手段】まず、第1の値に設定された第1のイネーブル信号を演算部に供給し、演算部を通常動作モードより消費電力が小さいスリープモードに設定する。次に、第1の期間経過後に第1のイネーブル信号が第1の値であるか否かを判定し、第1の値である場合、第2の値に設定された第2のイネーブル信号をメモリに供給し、メモリをスリープモードに設定する。次に、第2の期間経過後に第2のイネーブル信号が第2の値であるか否かを判定し、第2の値である場合、第3の値に設定された第3のイネーブル信号をアナログ回路に供給し、アナログ回路をスリープモードに設定する。次に、第3の期間経過後に第3のイネーブル信号が第3の値であるか否かを判定し、第3の値である場合、第4の値に設定された第4のイネーブル信号をレギュレータに供給し、レギュレータをスリープモードに設定する。

(もっと読む)

半導体装置および半導体装置の動作試験方法

【課題】ROMに試験用プログラムを記憶させることができない場合にも初期動作の試験が可能な半導体装置の実現。

【解決手段】CPUコア11と、ROM13と、RAM14と、アドレス信号をデコードして、ROMまたはRAMの選択信号を発生するROM/RAM選択アドレスデコーダ15と、スタンバイ制御回路19と、RAM、ROM/RAM選択アドレスデコーダおよびスタンバイ制御回路の電源を、通常電源とバックアップ電源の間で切り替えるバックアップ電源切換機構と、を備え、スタンバイ制御回路は、スタンバイモードから通常動作状態に変化すると、CPUコアがROMの替わりにRAMをアクセスするように、ROM/RAM選択アドレスデコーダを設定可能であり、CPUコアがRAMに記憶された初期動作プログラムにしたがって起動動作を実行可能である。

(もっと読む)

マイクロコンピュータ

【課題】CPUが、例え、低消費電力モード中に外来ノイズの影響を受けたとしても外部信号端子はハイインピーダンス状態となっているので、その端子によって外部デバイスが駆動されることはなく、信頼性を向上する。

【解決手段】端子制御手段は、CPUが低消費電力モードに移行する場合に出力するコマンドに応じて、外部信号端子42に接続される出力バッファ43Aをハイインピーダンス状態に設定するための信号を出力する。そして、前記出力信号は、前記CPUが動作している期間に前記外部信号端子42を制御するために出力されるポート制御信号と共に、論理ゲート41を介して前記出力バッファ43Aに与えられる。

(もっと読む)

マルチコアプロセッサ及びこれを用いる車載電子制御装置

【課題】各コアの動作周波数を時系列で適切に変動させることで、放射ノイズ等の問題点を少なくとも部分的に解決すること。

【解決手段】 本発明は、複数のコアを搭載したマルチコアプロセッサ1,2であって、複数のコアA,B,Cは、同一の周期Tで周期的に周波数が変動する動作クロックで動作するように構成され、コアの動作クロックの周波数の変動位相が、前記複数のコア間でずらされることを特徴とする。好ましくは、各コアの動作クロックの周波数の変動位相は、時間T/N(Nはコア数)に相当する位相ずつずらされる。好ましくは、コアの動作クロックの周波数の変動態様は、複数のコア間で、変動位相が異なる以外は同一である。

(もっと読む)

マイクロ・コンピュータ及びその制御方法

【課題】特に休止からの再稼動時に最適な周波数を迅速に設定するマイクロ・コンピュータ及びその制御方法を提供すること。

【解決手段】本発明に係るマイクロ・コンピュータ1は、外部又は内部からの要求により、クロック信号の供給が停止される演算部18と、外部から供給されるクロック信号の周波数を変更し、異なる周波数のクロック信号を1以上生成するクロック信号生成部16と、演算部の稼動状態にかかわらずマイクロ・コンピュータの動作電圧を検出する電圧検出部と、クロック信号生成部16で生成されたクロック信号又は外部から供給されるクロック信号のうちいずれかを選択して演算部18に供給する選択部17と、演算部18の稼動状態にかかわらず電圧検出部の検出結果に基づき、選択部17がクロック信号を選択するための選択信号34を生成する選択信号生成部14とを有する。

(もっと読む)

マイクロコンピュータ

【課題】マイクロコンピュータの動作に用いられる低速クロックが安定していないときにマイクロコンピュータの動作が停止しないようにすることができる構成を提供する。

【解決手段】マイクロコンピュータ10に低速クロックの状態を判定するための低速クロック確認部40を備える。この低速クロック確認部40は、確認用クロック発振部41で発生させた確認用クロックを用いて時間測定部42にて低速クロックの数を数え、比較部43にて低速クロックの数が規定値を満たすか否かを判定する。そして、比較部43が低速クロックに異常があると判定すると、低速クロック確認部40は出力部44から低速クロックの異常状態を示す異常信号を間欠制御部70、クロック制御部50、および機能部80に出力する。これにより、マイクロコンピュータ10が低速クロックを用いた低速動作に遷移しないようにする。

(もっと読む)

半導体装置

【課題】消費電流を低減させる。

【解決手段】半導体装置は、外部電源電圧より低い内部電圧を第1出力端子から定常的に出力する第1降圧回路、状態制御信号に応じて第1モードの時に内部電圧を第2出力端子から出力し、第2モードの時にHZにする第2降圧回路、第3モードの時に内部電圧を第3出力端子から出力し、第4モードの時にHZにする第3降圧回路、第5モードの時に内部電圧を第4出力端子から出力し、第6モードの時にHZにする第4降圧回路、第1内部回路、第2内部回路及びスイッチを備える。第1,第2出力端子は共通に平滑容量素子に接続される。第3,第4出力端子は共通に接続され、スイッチを介して容量素子に接続される。第1,第2出力端子から出力される内部電圧は、第1内部回路に供給される。第3,第4出力端子から出力される内部電圧は、第2内部回路に供給される。

(もっと読む)

情報処理装置及び制御方法

【課題】書き換え可能なメモリがICチップの外部に配置されていても消費電力を抑えることができる情報処理装置を提供することを目的とする。

【解決手段】本発明に係る情報処理装置は、CPU、内部メモリ及び前記CPUと前記内部メモリとを接続する内部配線が搭載されたICチップと、前記ICチップの外部にあり、インターフェースで前記内部配線と接続される外部メモリと、処理待機時に前記内部メモリ内の待機プログラムを前記CPUに実行させ、外部からの処理要求時に前記外部メモリ内の処理プログラムを前記CPUに実行させる実行番地遷移手段と、前記処理待機時に前記外部メモリを停止させ、前記処理要求時に前記外部メモリを動作させる外部メモリ制御手段と、を備える

(もっと読む)

シングルチップデータプロセッサ及び半導体集積回路

【課題】接続している別のデータプロセッサから、当該データプロセッサの内部機能若しくは当該データプロセッサの外付け回路を効率良く利用する方法を提供する。

【解決手段】一のデータプロセッサ101に他のデータプロセッサ100との接続を可能にするためのインタフェース手段119を設け、このインタフェース手段に、一のデータプロセッサ内の内部バス108に他のデータプロセッサをバスマスタとして接続可能にする機能を設け、内部バスにメモリマップされた周辺機能を前記インタフェース手段を介して外部より当該他のデータプロセッサが直接操作できるようにする。これにより、データプロセッサは、実行中のプログラムを中断することなく、別のデータプロセッサの周辺機能等を使うことが可能となる。要するに、一のデータプロセッサは別のデータプロセッサの周辺リソースを共有することが可能になる。

(もっと読む)

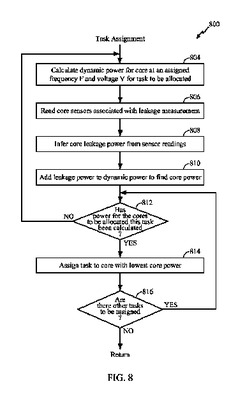

非対称マルチプロセッサに対する適応型スレッドスケジューリングのための装置および方法

本発明によれば、システムのエネルギー使用を低減するための、複数のコアを対象とした適応型スレッドスケジューリングの技法が提供される。一実施形態において、スレッドスケジューラは、複数のコアに関連した漏れ電流情報を受け取る。漏れ電流情報は、システムのエネルギー使用を低減するために、複数のコアのうちの1つコアに対してスレッドをスケジュール設定するように用いられる。また、センサのオンチップ較正が提供される。  (もっと読む)

(もっと読む)

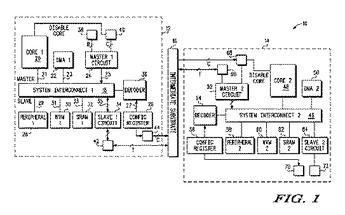

集積回路を相互接続するための技術

処理コア(20,48)及びオンボードメモリ(30,32,60,62)をそれぞれ有する2つの集積回路ダイ(12,14)は、相互接続されて一体にパッケージ化されて、多チップモジュール(10)を形成する。第1のダイ(12)はプライマリであると考えられ、第2のダイ(14)はセカンダリであると考えられ、インターポーザー(16)を介して接続されている。第1及び第2のダイは同じ設計であってよいため、周辺装置(28,56)及びメモリなど同じリソースを有してよく、好適には共通のシステム相互接続プロトコルを有する。第2のダイのコアは使用不能とされるか、少なくとも低電力モードとされる。第1のダイは、第2のダイに対し相互接続を行うための最小の回路(34,26)を備える。第2のダイはいくつかの必要なインタフェース回路(52)と、1つのアドレス変換器(50)とを有する。その結果、第1のダイのコアは、第2の集積回路のメモリ及び他のリソースを用いるトランザクションを、そのメモリ及びリソースが第1のダイ上に存在する場合のように、実行することができる。  (もっと読む)

(もっと読む)

マイクロコンピュータ

【課題】リセット期間中の消費電力を削減する。

【解決手段】マイクロコンピュータは、プロセッサと、第1発振周波数の第1発振信号を出力する第1発振回路と、第1発振周波数より低い第2発振周波数の第2発振信号を出力する第2発振回路と、通常状態または初期化状態の何れか一方を指示するリセット信号に基づいて、通常状態の場合は第1発振信号をプロセッサの動作用の動作クロックとして出力し、初期化状態の場合は第2発振信号を初期化処理用の初期化クロックとして出力するクロック選択回路と、を備える。

(もっと読む)

マイクロコンピュータ

【課題】暗電流を増加させることなくレジスタのリフレッシュを行うことが可能なマイクロコンピュータを提供する。

【解決手段】CPUの動作モードを、CPUが動作している通常動作モードと、CPUが停止しているスリープモードとの間で切り替える動作モード切換手段と、通常動作モードにて動作し、CPUを動作させるためのメインクロックを生成するメインクロック生成手段と、メインクロック生成手段とは別に設けられ、サブクロックを生成するサブクロック生成手段と、CPUの設定状態や動作状態を含むCPU状態情報を記憶する第一記憶手段と、リフレッシュ用のCPU状態情報を記憶するする第二記憶手段と、スリープモードにおいて、サブクロックに基づいて予め定められたタイミングでリフレッシュ信号を生成するリフレッシュ信号生成手段と、リフレッシュ信号に基づいて、第二記憶手段に記憶されたCPU状態情報を読み出して、第一記憶手段に書き込むデータリフレッシュ手段と、を備えることを特徴とする。

(もっと読む)

1 - 20 / 64

[ Back to top ]