Fターム[5B065CA12]の内容

外部記憶装置との入出力 (22,430) | 入出力制御 (3,777) | 外部記憶制御装置;入出力制御装置 (748) | マイクロプロセッサを含むもの (140)

Fターム[5B065CA12]に分類される特許

21 - 40 / 140

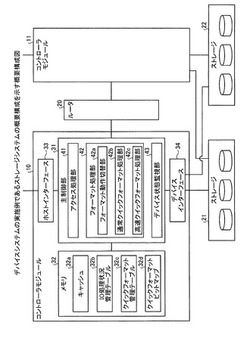

デバイス管理装置、デバイス初期化方法、デバイス初期化プログラムおよびデバイスシステム

【課題】アクセスのバックグラウンドで実行するフォーマットにおいて、デバイスへのアクセス性能を確保しつつ、フォーマットの所要時間を短縮すること。

【解決手段】ストレージ21,22内のデバイスに対するフォーマット進捗状況をクイックフォーマットビットマップ32dで管理し、ビットマップの1ビット分のフォーマット毎にコントローラモジュール11に進捗状況を通知する通常クイックフォーマットと、所定ビット分のフォーマット毎にコントローラモジュール11に進捗状況を通知する高速クイックフォーマットとを設け、フォーマット動作切替部42aがアクセスの発生状況やデバイスの動作状態に基づいて通常クイックフォーマットと高速クイックフォーマットとを切り替える。

(もっと読む)

ミラーリングシステム

【課題】ミラーリングによる信頼性を向上させることを可能とする。

【解決手段】クライアント端末10のRAIDコントローラ12は、ライト要求に応じてSSD11にデータを書き込む。RAIDコントローラ12は、ライト要求をミラーサーバ20に送信する。ミラーサーバ20は、ライト要求に含まれる端末識別情報によって識別されるクライアント端末10に対してミラーサーバ20がメインサーバとして動作するかサブサーバとして動作するかを、クライアント情報テーブルに保持されている動作情報に基づいて判定する。ミラーサーバ20は、メインサーバとして動作すると判定された場合、ライト要求に応じてHDD21にデータを書き込む。ミラーサーバ20は、サブサーバとして動作すると判定された場合、ライト要求に応じてデータが書き込まれるHDD21における書き込み位置をライト位置情報テーブルに登録する。

(もっと読む)

コピー制御装置

【課題】キャッシュビジー状態の発生に起因するコピー処理速度の低下を防止することを課題とする。

【解決手段】キャッシュ上の記憶領域を確保してディスク間のコピー処理を実行している最中に、通信可能な状態で接続されたホスト装置から書き込み要求を受け付けた場合に、書き込み要求に含まれているデータの容量を測定し、測定されたデータの容量に応じて、コピー処理用に確保している記憶領域の容量を変更する。例えば、複数のセッションでコピー処理を実行しているときに、ホスト装置から書き込み要求を受け付けた結果、キャッシュにおけるデータ蓄積量が予め設定されている所定の閾値以上になった場合に、現に確立されているセッションの数を1に変更して、コピー処理用に確保している記憶領域の容量を1セッション分に変更する。

(もっと読む)

情報処理装置およびデータ記憶装置

【課題】不揮発性半導体メモリをキャッシュとして内蔵する場合におけるデータアクセスを効率的に行うことを実現した情報処理装置を提供する。

【解決手段】情報処理装置1の外部記憶装置であるハイブリッドHDD19は、記憶部196のキャッシュとして半導体不揮発性メモリ194を内蔵する。ホスト側からリード要求を受けると、制御部191は、記憶部196から読み出したデータを、最も最近読み出された順にキャッシュされるように入れ替えを行いながら半導体不揮発性メモリ194に格納する。また、ホスト側からライト要求を受けると、制御部191は、この書き込みに伴って更新すべきデータが半導体不揮発性メモリ194に格納されていないかを調べ、格納されていれば、記憶部196へのデータ書き込みと共に、その更新対象データを半導体不揮発性メモリ194内において無効化する。

(もっと読む)

外部記憶装置およびそのメモリアクセス制御方法

【課題】セクタデータを連続してアクセスする外部記憶装置において、単一のエラー訂正手段によりエラー検出・訂正を行いながらメモリアクセスを高速化する。

【解決手段】ホスト2がライトするセクタデータは一時ライトバッファ7に格納される。マイクロプロセッサ8は、ライトバッファに格納されたセクタデータが奇数番目のセクタデータの場合には第1のメモリ4に、偶数番目のセクタデータの場合には第2のメモリ5に格納する。ホスト2がセクタデータをリードするときには、データ切換手段11において、第1のメモリから読み出したN番目のセクタデータをシステムバスに対し出力すると同時に、第2のメモリから読み出したN+1番目のセクタデータ(ホストコンピュータが次にリードするセクタデータ)をエラー訂正手段に対し出力する。これにより、N+1番目のセクタデータに対するエラー検出およびエラー訂正に要する時間を見かけ上短縮する。

(もっと読む)

複数のマイクロプロセッサを有するストレージシステム、及び、そのストレージシステムにおける処理分担方法

複数のマイクロプロセッサを備えるストレージシステムにおいて、非同期処理のスループットを確保しつつ、同期処理の非同期処理待ちによるI/Oレスポンスの遅れを防ぐ。

コントローラが有する複数のマイクロプロセッサに、同期プロセッサと、非同期プロセッサが混在する。同期プロセッサは、同期処理を担当し非同期処理を担当しないマイクロプロセッサである。非同期プロセッサは、非同期処理を担当し同期処理を担当しないマイクロプロセッサである。  (もっと読む)

(もっと読む)

ストレージ装置、及びストレージ装置におけるデータ検証方法

ホスト装置20からディスクドライブ210へのデータ書き込み要求を受信した際、当該データ書き込み要求によってディスクドライブ210に書き込まれる書き込みデータについて第1誤り検出符号を生成して記憶し、書き込みデータのディスクドライブ210への書き込み処理を実行し、書き込み処理に要した時間である応答時間が予め設定された閾値を超えているか否かを判断し、応答時間が閾値を超えていた場合に、書き込みデータの書き込み先のセクタから当該セクタに格納されているデータを読み出し、読み出したデータについて第2誤り検出符号を生成し、第1誤り検出符号と第2誤り検出符号を比較して、両者が一致しない場合に書き込み処理が正常に行われなかった旨を示す信号を生成するようにする。 (もっと読む)

USBストレージ同時書込み装置及びそれに用いるUSBストレージ同時書込み方法

【課題】 同種類の複数のUSBストレージ機器にデータを書き込む場合の時間の短縮を図ることができるUSBストレージ同時書込み装置を提供する。

【解決手段】 USBストレージ同時書込み装置(1)は、情報機器(1)から第1のUSBストレージ機器(3)と同一種類の第2のUSBストレージ機器(4)への方向に流れるパケットの中に含まれるUSBアドレスを第1のUSBストレージ機器(3)のUSBアドレスに変換して第2のUSBストレージ機器(4)に渡す制御手段(解析/制御部12)を有し、制御手段(解析/制御部12)により第1のUSBストレージ機器(3)のUSBアドレスと第2のUSBストレージ機器(4)のUSBアドレスとを同一にして第1及び第2のUSBストレージ機器(3,4)に同一データを同時に書込んでいる。

(もっと読む)

クラスタ・ストレージ装置、及びそれを制御する方法

【課題】異なるディスク容量を許容し、稼働中のディスク台数に対して適切な冗長性を維持するクラスタ・ストレージシステムを提供する。

【解決手段】情報記録制御装置と3台以上のストレージ装置から構成されるクラスタ・ストレージを提供し、データの保存に際しては、情報記録制御装置がデータの差異を逐次計算し、複数のストレージ装置に分散保存し、データの出力に際しては情報記録制御装置が複数のストレージ装置からデータ差異を収集し、復元・出力するようにする。本発明によれば異なるディスク容量を許容し、さらに動作しているディスクの台数に応じた冗長性を確保する。

(もっと読む)

ライト完了を検知する機能を有するストレージシステム

【課題】データのライト完了を検知する機能を有したストレージシステムの処理速度が低下しないようにする。

【解決手段】コントローラ部が、一以上のプロセッサ部と、一以上の記憶資源と、プロセッサ部及び記憶資源に接続された一以上の転送制御部とを有する。転送制御部は、受信部と送信部とを有する。受信部が、プロセッサ部からライトパケットを受信し、そのライトパケットに特定のコードを含めて送信する。送信部が、ライトパケットを受信した場合、受信したライトパケットが特定のコードを含んでいれば、そのライトパケット内のライト対象のデータをライト先の記憶資源にライトした後に、ライトの完了を表す応答である応答パケットを生成し、生成した応答パケットを送信する。

(選択図:図1)

(もっと読む)

(もっと読む)

ストレージ装置、及びストレージ装置における制御情報の更新方法

チャネル装置(CHA_PK11)、マイクロプロセッサ(MP_PK12)を備え、CHA_PK11及びMP_PK12は、夫々、MP_PK12がアクセス可能な論理ボリューム(LDEV171)を示す情報である制御情報を記憶し、ホスト装置20からI/O要求を受信すると、CHA_PK11が自身の制御情報に基づきI/O要求の対象の論理ボリュームのアクセス権を有するMP_PK12にI/Oコマンドを送信するストレージ装置10に、CHA_PK11からI/Oコマンドを受信したMP_PK12が、自身が記憶している制御情報に基づき論理ボリュームへのアクセス権の有無を判断し、アクセス権を有しない場合はCHA_PK11に自身の制御情報を送信してCHA_PK11の制御情報を更新する。 (もっと読む)

ストレージシステムおよびその制御方法

【解決課題】非対称性を持つ複数のコアの負荷分散に伴う負荷変動を考慮し、ユーザの設定を踏まえた最適な負荷分散処理を選択して実行する。

【解決手段】複数のコア122を有するコントローラ111は、LU制御権管理情報を基にLU制御権を有するコア122とLU制御権の移行先の候補となるコアとの関係を示すパターンをLU毎に抽出し、複数のリソースの使用状況をLU毎に測定し、測定結果を基に複数のリソースの使用状況の変化と移行処理自体によって発生すると想定されるオーバヘッドをLU毎に予測し、各予測結果を基に、ユーザの設定情報に適合するパターンを選択し、選択したパターンに属するコアにLU制御権を移行する。

(もっと読む)

無線デジタルコンテンツの管理のための方法及び装置

装置のデジタルデータを独立して外部へ送出できない内蔵プロセッサを有する装置において使用されるためのメモリカードにおいて、デジタルデータは前記装置により捕捉され、前記メモリカードは前記装置からのデータの送出を制御するように構成された中央プロセッサと、中央プロセッサに動作可能に接続され送出されるデータを記憶するように構成されている記憶モジュールと、記憶モジュールからデジタルデータを送出するように構成され中央プロセッサとメモリのいずれか一方に動作可能に接続されている無線モジュールとを具備している。 (もっと読む)

ストレージ装置、ストレージ性能管理方法及びストレージ性能管理プログラム

【課題】ユーザが容易に障害解析を行うことができるストレージ装置、ストレージ性能管理方法及びストレージ性能管理プログラムを提供すること。

【解決手段】本発明にかかるストレージ装置は、サーバからの要求に応じてデータの入出力処理を実行する入出力処理部と、前記入出力処理部における入出力処理の応答に関するパフォーマンス情報と、当該入出力処理に関する処理状況を示す処理状況情報とを収集する情報収集部と、前記パフォーマンス情報と前記処理状況情報とを対応付けた収集情報を外部へ出力する情報出力部と、を備える。

(もっと読む)

ストレージシステム及び記憶装置

【課題】ホストにより記憶装置のビジー時間を設定することが可能なメモリシステム及び記憶装置を提供する。

【解決手段】記憶装置は、複数のデータ記憶領域を有する不揮発性メモリと、不揮発性メモリの読み出し及び書き込みを制御するコントローラとを有する。ホストは、記憶装置の動作に先立って、記憶装置の動作に必要で、許容可能な最大ビジー時間を前記記憶装置に指示する。

(もっと読む)

ストレージ装置及びその制御方法

【課題】ストレージシステムに制御モジュールを順次追加できるように設計されても、上位装置に対して、統一された制御資源として管理できるようにしたストレージ装置及びその制御方法を提供する。

【解決手段】複数の制御モジュールのそれぞれに存在する管理部のうち、複数のモジュールに対して統一的な管理を実行する管理部を設定し、この管理部に管理ユーザがアクセスし、管理ユーザがこの管理部を介して複数のモジュールを統一的に管理するようにした。

(もっと読む)

上位装置から指定されるデバイスに関する記憶容量を変更するストレージシステム及び方法

【課題】上位装置に提供されるデバイスに関連付ける論理ボリュームの数を増減させることなく、そのデバイスについての記憶容量を変更できるようにする。

【解決手段】ストレージシステムのコントローラが、デバイスを指定した容量変更指示を受け付け、仮想ボリュームの記憶容量を表すボリューム容量値を含んだ管理情報内の、指定されているデバイスに関連付けられている仮想ボリュームのボリューム容量値を、その容量変更指示に従う記憶容量を表すボリューム容量値に変更する。

(もっと読む)

ディスク装置及びその制御方法

【課題】書き換え回数に制限のある不揮発メモリを含むディスク装置において、不揮発メモリの交替領域を使い果たした後も不揮発メモリを効率的に使用する。

【解決手段】本発明は、書き換え回数に制限のある不揮発メモリ、ディスク、及び不揮発メモリの論理アドレス(LBA:Logical Block Address)と物理アドレスとの対応関係を管理するメモリ管理テーブルを含む制御部を有する。制御部は、不揮発メモリにデータを書き込むべきLBAに対応する物理アドレスの領域の不良発生に応答して、データを書き込むべきLBAとは異なる不揮発メモリのLBAに対応する物理アドレスにデータを書き込み、メモリ管理テーブルにおいて、データを書き込んだ物理アドレスをデータを書き込むべきLBAに対応付ける。

(もっと読む)

ストレージシステム及びオーナー権の移行方法

【課題】ストレージ装置の性能を十分に発揮できるストレージシステム及びオーナー権の移行方法を提案しようとするものである。

【解決手段】複数のマイクロプロセッサと、ドライブ群に形成される複数の記憶領域と、複数の記憶領域のそれぞれにアクセスするオーナー権を各マイクロプロセッサに割当てる割当て部と、各マイクロプロセッサが、複数の記憶領域のそれぞれに対して発行された要求を実行するのに要する時間割合を稼働率として管理する管理部と、任意のマイクロプロセッサに割当てられたオーナー権を稼働率に基づいて決定された他のマイクロプロセッサに移行するために、任意のマイクロプロセッサがオーナー権をもつ1以上の記憶領域から移行対象の記憶領域を検索する検索部と、移行対象の記憶領域に対して割当てられたオーナー権を任意のマイクロプロセッサから他のマイクロプロセッサに移行する移行部と、を有することとした。

(もっと読む)

フラッシュメモリモジュール及びストレージシステム

【課題】ストレージコントローラがフラッシュメモリの記憶領域を意識した制御を行えるようにする。

【解決手段】ストレージコントローラが、論理アドレスとフラッシュメモリ内の記憶領域(例えば物理ブロック)の物理アドレスとの対応関係を表すアドレス変換情報を管理する。ストレージコントローラが、上位装置からのI/O要求が指定する論理アドレスに対応した物理アドレスを、上記アドレス変換情報を用いて特定し、特定された物理アドレスに基づくI/O先情報を有したI/Oコマンドを、フラッシュメモリモジュール内のメモリコントローラに送信する。メモリコントローラは、ストレージコントローラからのI/Oコマンドが有するI/O先情報から特定される、フラッシュメモリ内の記憶領域に対してI/Oを行う。

(もっと読む)

21 - 40 / 140

[ Back to top ]