Fターム[5B079AA04]の内容

Fターム[5B079AA04]に分類される特許

1 - 20 / 85

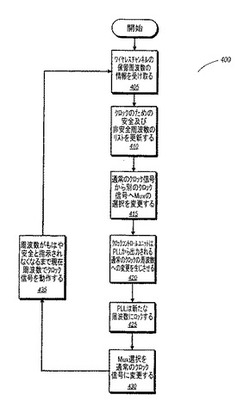

受信器PLL管理を伴う機敏なクロッキング

【課題】干渉を回避するためにクロック信号の周波数を変更する方法及び装置を提供する。

【解決手段】一実施形態において、第1のインターフェイスに搬送されるデータは、第1の周波数のクロック信号に同期される。信号は、別の周波数で第2のインターフェイスに搬送される。第2のインターフェイスに信号が搬送される周波数の変更に応答して、第1のインターフェイスに関連したクロックコントロールユニットが、第2の周波数へのクロック信号の変更を開始する。第2の周波数は、第2のインターフェイスに信号が搬送される周波数との干渉を生じないように選択される。クロック周波数の変更は、インターフェイスのクロックラインにおける擬似的アクティビティを防止するように遂行される。

(もっと読む)

情報処理装置および情報処理装置の制御方法

【課題】バッテリ交換時にシステムが瞬断されることを抑制できる情報処理装置および情報処理装置の制御方法を提供する。

【解決手段】第1のバッテリ102は、第1のバッテリ収納108に着脱可能に収納され、第2のバッテリ103は、第2のバッテリ収納部110に着脱可能に収納され、システム制御部113,114は、第1のバッテリ102または第2のバッテリ103を交換する場合に使用される蓋107,109が開放状態であることが検出された場合に、情報処理装置100の消費電力が低下するように情報処理装置100の動作を制限する制限モードを開始させる。

(もっと読む)

端末機温度制御方法及びこれをサポートする端末機

【課題】端末機の温度制御を効率的かつ安定的な実行を補助する端末機温度制御方法及びこれに基づく端末機を提供すること。

【解決手段】端末機の温度を検出する温度センサと、前記温度センサが収集した前記端末機の温度が事前設定された第1設定温度に該当する場合、事前設定された第1駆動周波数で駆動され、前記第1駆動周波数の駆動によって前記端末機の温度が低下して前記第1設定温度よりも低い第2設定温度まで低下する場合、第1駆動周波数よりも高い第2駆動周波数で駆動されるか、または、前記端末機の温度が事前設定された第1設定温度に該当する場合、事前設定された第1駆動周波数で第1時間間隔の間駆動され、前記第1時間間隔経過後に第2時間の間第1駆動周波数よりも高い第2駆動周波数で駆動される過程を一定時間の間繰り返して行う制御部と、を備える端末機、及びこれに基づく温度制御方法の構成を開示する。

(もっと読む)

位相補間回路及びその設計方法

【課題】トランジスタのばらつきによる影響を抑制し、位相歪みを解消する位相補間回路を提供する。

【解決手段】位相補間回路は、位相の異なる入力波形を受け付ける複数の差動対を含み、複数の差動対のうち、第1の差動対及び第2の差動対の出力波形を合成する位相補間回路である。さらに、複数の差動対にバイアス電流を供給する電流源をn個含み、第1の差動対に供給するバイアス電流を、n個の電流源のうち、m個の電流源から供給可能であると共に、第2の差動対に供給するバイアス電流をn個の電流源のうち、n−m個の電流源から供給可能であって、n個の電流源が供給する電流は、予め定められた単位電流値を基準として、それぞれ重み付けがされている可変電流源と、出力波形の位相シフト量に基づいて、可変電流源のm個の電流源の数を変更する制御回路と、を備えている。

(もっと読む)

半導体装置、それを用いた無線通信端末、及びクロック周波数制御方法

【課題】無線通信端末等に好適な半導体装置を提供すること。

【解決手段】半導体装置1は、制御信号divに応じて、出力するクロック信号の周波数を変化させるクロック生成回路15と、クロック信号に応じて動作する演算回路(例えばCPU0)と、演算回路CPU0からのアクセスに応じ、活性化される記憶回路(例えばIC0)と、記憶回路IC0に対する演算回路CPU0のアクセス回数を検出し、アクセス回数が増えた場合に要求信号(例えばpsreq1)を出力するメモリアクセス検出部12と、要求信号psreq1に応じて、クロック信号の周波数を下げるための制御信号divを生成するクロック制御回路14と、を備える。

(もっと読む)

クロック動作システム

【課題】クロック信号に正確に同期した動作が行えるクロック動作システムを、小さな回路規模で実現すること。

【解決手段】逆相関係のクロック信号対CKq,CKqxを含むクロック信号群を生成する送信クロック生成回路21と、クロック信号群の送信経路22と、クロック信号群に対して逓倍関係を有する複数のクロック信号に基づいて動作するクロック動作回路23-0,23-1,23-nと、を有し、クロック動作回路は、送信経路を介して送信されたクロック信号群から、複数のクロック信号を生成する逓倍クロック生成回路24を有するクロック動作システム。

(もっと読む)

情報処理装置および動作速度制御方法

【課題】第三者作成のアプリが使用される場合でも、リソースの動作に対するユーザの体感速度の低下を抑えた状態で電力消費を低減することができる、情報処理装置を提供する。

【解決手段】情報処理装置100は、動作速度に応じて電力を消費するリソース200を有する装置であって、リソース200の動作速度が、リソース200の動作に対するユーザの体感速度に与える影響の度合いである、影響度を判別する影響度判別部300と、影響度が低いほど、リソース200の動作速度をより低くする動作速度制御部400とを有する。

(もっと読む)

グリッチフリークロック信号マルチプレクサ回路および動作の方法

【課題】クロックマルチプレクサを駆動する第1のクロック入力から第2のクロック入力への切換えにおいて起こるグリッチを低減する。

【解決手段】クロックマルチプレクサ116は、第1のクロック入力を受信し、クロック出力118を提供し、第1のクロック出力における低フェーズ入力レベルに応答してクロック出力における低フェーズ出力レベルを判定する。限定された期間、低フェーズ出力レベルは、第1のクロック入力信号のフェーズレベルに関わらず維持される。クロックマルチプレクサ116は、第2のクロック入力を受信し、第2のクロック入力信号における低フェーズ入力レベルを判定する。第2のクロック入力に応答してクロック出力118を提供することへの切換えは、第2のクロック入力信号における低フェーズ入力レベルの間に起こる。その後、クロックマルチプレクサ116の出力は第2のクロック信号のフェーズレベルに従う。

(もっと読む)

通信システム及びそれに用いられる通信ノード

【課題】通信装置内の内部回路の一部を停止させるのみならず、通信装置内の通信ユニットまでも停止させて、更なる省電力化を図る。

【解決手段】各々が通常モードと省電力モードとを有するノードがLANケーブルを介して相互に接続され、ピアトゥピアで通信を行う通信システムにおいて、各ノードは、他のノードとの間で行う通信の制御を担当する第1制御手段と、第1制御手段で担当しない制御を担当する第2制御手段と、第1制御手段に対して動作クロックを供給するクロック供給手段とを有し、第1制御手段は、ハブから送信される省電力モード切替信号を受信する受信手段と、ハブに対してモード切替することを示す信号を送信する送信手段と、送信手段に対して前記信号を送信するように指示するとともにクロック供給手段に対してモード切替を指示する状態遷移手段と、LANケーブルの電圧変化が所定の閾値を越えたか否かを検知する検知手段とを備える。

(もっと読む)

情報処理装置

【課題】PCの利用状況に適した電力制御を行える情報処理装置を提供する。

【解決手段】情報処理装置本体の稼働中のアプリを監視するアプリ監視手段と、情報処理装置本体の電力状況を監視する状況監視手段と、電力状況を記憶する記憶手段と、情報処理装置本体の動作状況及び電力状況に基づいて情報処理装置本体のハードウエアリソースの消費電力量の制限量を制御する制御手段と、を備えた。

(もっと読む)

クロック供給装置およびクロック供給方法

【課題】発振器のウォームアップの完了を容易に判定できるようにする。

【解決手段】クロック供給装置1は、通信装置内の処理に用いられるクロック信号を供給する。発振器1aは、クロック信号を生成する。測定部1bは、通信装置に接続された伝送路から抽出されたリファレンスクロック信号を取得し、クロック信号とリファレンスクロック信号との周波数ずれを測定する。判定部1cは、周波数ずれの測定結果と電力供給の状況とに基づいて、発振器1aのウォームアップが完了したか否か判定する。

(もっと読む)

マイクロコントローラ及びその制御方法

【課題】低消費電流で動作する構成が求められている。

【解決手段】入力データが入力されると、前記入力データに応じて起動要求信号を出力するデータ入力部と、前記起動要求信号に応じて起動し、クロック信号を生成する発振器と、前記データ入力部からの前記起動要求信号を前記発振器に出力し、起動後に生成される前記発振器からのクロック信号を、前記データ入力部の動作クロック信号である第1のクロック信号と、第2のクロック信号として供給するクロック信号供給制御部と、前記第2のクロック信号を動作クロックとして動作し、その動作時に前記入力データに応じた処理を行うCPUと、を有するマイクロコントローラ。

(もっと読む)

制御装置

【課題】起動時間をより短縮すること。

【解決手段】決済端末装置1は、主電源VMのオン/オフを操作する電源操作部14と、バッテリ電源VBを利用してクロック信号を常時生成する外付けの時計IC20と、時計IC20が生成したクロック信号に従って、主電源VMからの電力を利用して各種制御処理を実行するCPU16と、を備え、CPU16は、電源操作部14によって主電源VMがオフ状態からオン状態に切り替えられたとき、時計IC20が生成したクロック信号に従って起動処理を実行する。これにより、水晶発振器からのクロック信号を用いずに起動処理を開始することができるので、水晶発振器の発振出力が安定するまで待機する必要がなくなり、起動時間を短縮することができる。

(もっと読む)

無線通信端末装置

【課題】細かな時間調整を行うことで、CPUセービングの復帰時間を短縮する無線通信端末装置及びそのセービング復帰制御方式を提供する。

【解決手段】CPU10は外部デバイス30aにセービング要求を通知し(S100)、外部デバイス30aは、割り込み出力待ち設定レジスタ31に割り込み出力待ち時間を設定する(S200)。CPU10は、クロック安定時間設定レジスタ11にクロック安定時間を設定し(S300)、CPUセービングに移行する。外部デバイス30aが起動要求信号を入力し(S400)、外部クロック水晶発振子40に「オン」信号を出力し(S500)、外部クロック水晶発振子40は外部クロックをCPU10に出力する(S600)。外部デバイス30aは、割り込み出力待ち時間の経過後にCPU10に割り込み通知を出力する(S700)。CPU10は、クロック安定時間が経過した後に動作を再開する。

(もっと読む)

クロックデータリカバリ回路および送受信半導体集積回路

【課題】高速ジッタに追従してクロック再生とデータ再生を可能とする。

【解決手段】クロックデータリカバリ回路1のパルス幅整形回路102はハイとローの期間のデューティ比が略5:5の第1多相クロックCLK’0〜9に応答して、デューティ比が略5−α:5+αの第2多相クロックCLK0〜9を生成する。サンプリング回路106は受信データ信号RXDATAを第2多相クロックでサンプリングして、複数のサンプリング信号を生成する。エッジ検出回路105は複数のエッジ検出信号を生成し、位相選択信号生成回路103は複数の位相選択信号を生成する。クロックデータ生成回路104は、複数のサンプリング信号Sample_Φ0〜9と受信データ信号RXDATAの一方の信号と複数の位相選択信号と第2の多相クロックに応答して、再生クロックRCLKと再生データRDATAを生成する。

(もっと読む)

通信装置、通信装置の制御方法および情報処理システム

【課題】LANボードが動作中に省電力動作モードに移行することで生じる通信の遅延を抑止する。

【解決手段】ネットワークカード10は、スキャナー装置30が電力を通常に消費する通常状態、および電力を低減して消費する節電状態の何れの状態かを検出する状態検出部18と、自身が通常状態であり、スキャナー装置30が節電状態であることを状態検出部18が検出した場合、LAN50を介して指示される指示情報の有無に応じて、自身を節電状態に切り替えるか、否かを判断するモード移行判断部20と、モード移行判断部20の判断に基づき、自身を通常状態および節電状態の何れかに切り替えるモード切り替え部26とを備える。

(もっと読む)

通信装置、通信システムおよび通信方法

【課題】通信装置のクロック信号を停止させた休止状態から復帰するまでの期間を短縮する。

【解決手段】復帰処理を開始する一方の通信装置5は、自身のクロック信号が不安定な状態で、休止状態から復帰させる起動信号を送信する。一方の通信装置5は、自身のクロック信号が安定すると、当該クロック信号に基づくデータ送信が可能になったことを通知する送信可能信号を生成して送信する。他方の通信装置6は、起動信号を受信して自身のクロック信号が安定すると、当該クロック信号に基づくデータ送信が可能になったことを通知する送信可能信号を生成して送信する。複数の通信装置5,6の各々は、自らのクロック信号が安定し、相手の送信可能信号を受信すると、休止状態からの復帰処理を完了する。

(もっと読む)

無線デバイスにおける消費電力の最適化に関する装置と方法

無線デバイスのパワー最適化に関する装置と方法が開示されている。前記の装置と方法は、プロセッサからのデータ出力とプロセッサへのデータ入力をバッファするデータ・バッファに記憶されるデータの前記量を監視することに影響する。前記バッファに記憶される前記データの量に依存して、ダイナミックなクロック及び電圧のスケーリング(DCVS)機能のような、制御機能のパラメータは、前記データ・バッファに記憶されるデータの前記量に基づいて修正される。前記制御機能の前記パラメータを修正またはプリエンプティングすることで、これは少なくともプロセッサ周波数で制御するが、前記プロセッサは初期のパラメータ設定をこえてよりダイナミックにアプリケーションを処理できて、特に、1つかそれ以上のリアルタイム・アクティビティが完了に関して厳密な時定数を持つような状況では、増大したバッファの深さにはっきり表されるように前記プロセッサによりハンドルされる。その結果、前記制御機能が処理する条件に対して敏感であるので、電力の使用はさらに最適化される。  (もっと読む)

(もっと読む)

制御装置

【課題】周辺の環境に応じた処理速度で、各種処理を実行することが出来る制御装置を提供する。

【解決手段】マイコン11とフラッシュROM21との間でデータの授受を行う前に、クロック信号の最適化処理を行い、演算処理部12により、クロック生成部13で生成されるクロック信号の周期を縮小(周波数を高く)しながら、ベリファイを繰り返し実行する。そして、ベリファイの結果にエラーが出た場合は、動作周波数をエラーが出る直前の動作周波数(最適周波数)に戻してクロック信号を生成し、当該クロック信号に基づいて、演算処理部12が、マイコン11とフラッシュROM21との間におけるデータの授受動作を実行したり、その他各種の処理動作を実行したりする。

(もっと読む)

ジッタ算出装置、ジッタ算出方法、及びジッタ算出プログラム

【課題】ジッタを正確に見積もる。

【解決手段】回路データに基づいて、複数のセルの各々に供給される電源電圧を供給電圧として算出し、供給電圧データを生成するステップと、複数のセルの各々についてセル遅延量を計算し、セル遅延データを計算するステップと、セル遅延データに基づいて、終点における信号のジッタ値を計算し、ジッタデータを生成するステップとを具備する。セル遅延データを生成するステップは、上段セルに供給される信号の入力波形なまり、及び供給電圧データに基づいて、上段セルのセル遅延量、及び上段セルが出力する信号の出力波形なまりを算出するステップと、上段セルの出力波形なまりを、上段セルの下段に接続された下段セルの入力波形なまりとして設定するステップと、下段セルの入力波形なまり及び供給電圧データに基づいて、下段セルについてのセル遅延量及び出力波形なまりを算出するステップとを備える。

(もっと読む)

1 - 20 / 85

[ Back to top ]