Fターム[5B083BB06]の内容

計算機における入出力系RAS (2,172) | RAS動作 (543) | 保守 (146) | 試験、診断 (143)

Fターム[5B083BB06]の下位に属するFターム

Fターム[5B083BB06]に分類される特許

1 - 20 / 102

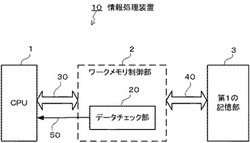

情報処理装置及び記憶部検査方法

【課題】CPUの運用中においても、記憶部の検査のためにCPUによるソフトウェアのデータ処理を一時停止させることがなく、記憶部の異常の有無をチェックすることができる情報処理装置及び記憶部検査方法を提供する。

【解決手段】CPU1とは独立に設置された記憶制御部2は、CPU1から書き込みようの処理データと書き込み先の記憶部3の指定アドレスを受け、検査用データを指定アドレスに書き込み、それを読み出す。記憶制御部2が備えるデータチェック部20は、検査用データと読み出されたデータとを比較し、一致するかどうかを判定する。一致しなければ指定アドレスに異常があると判定し、その旨をCPU1に通知し、一致すれば、記憶制御部は処理データを指定アドレスに書き込む。

(もっと読む)

バス診断機能を備えた制御装置

【課題】安全関連部と非安全関連部が混在している制御装置において、中央処理部が安全関連部にアクセスしたときのみ、データバス及びアドレスバス上の転送エラーを検知する制御装置を提供する。

【解決手段】制御装置の集積回路6a内に、CPU1aが安全関連レジスタにアクセスする際に、安全関連レジスタの値を格納するデータバス診断レジスタ12と、アドレスバスの値を格納するアドレスバス診断レジスタ13と、CPU1aが安全関連レジスタにアクセスする際にのみ、データバス診断レジスタ12に安全関連レジスタの値を、アドレスバス診断レジスタに13アドレスバスの値を夫々格納させるためのバス診断信号(CHKBUS)15を、データバス診断レジスタ12及びアドレスバス診断レジスタ13に供給するバス診断アドレス判定部14とを設ける。

(もっと読む)

集積回路装置、検証装置及び検証方法

【課題】集積回路装置が仕様通りとなっているかの検証の容易化を図る。

【解決手段】集積回路装置10は、マスターモジュール11と、マスターモジュール11に接続されたインターコネクト12と、インターコネクト12によってマスターモジュール11の接続先とされるスレーブモジュール13を含む。集積回路装置10は更に、そのスレーブモジュール13に対してインターコネクト12から送信されてくる読み出し命令信号を受信する固定値応答回路14を含む。インターコネクト12から読み出し命令信号を受信した固定値応答回路14は、インターコネクト12によってマスターモジュール11の接続先とされたスレーブモジュール13固有の固定値を、インターコネクト12に送信する。この固定値に基づき、接続先が仕様通りか否かを検証する。

(もっと読む)

システムバスの診断装置

【課題】 この発明は、機能用のモジュールとシステムバスとを確実に切り離して、故障を切り分けるシステムバスの診断装置を提供することである。

【解決手段】 この発明のシステムバスの診断装置は、管理用のモジュール2から制御線を介して接続回路を制御してシステムバス1から機能用のモジュールを全て切り離した後、管理用のモジュール2から制御線5aを介して接続回路4aを制御してA機能用のモジュール3aとシステムバス1とを接続し、システムバス1を介してA機能用のモジュール3aと管理用のモジュール2との間で通信できるか否かを判定して、A機能用のモジュール3aの故障を切り分けるものである。

(もっと読む)

試験プログラムおよび試験方法

【課題】任意のハードウェア構成を有する対象装置についてハードウェア構成に応じた負荷変動試験を実施することができる試験プログラムおよび試験方法を提供する。

【解決手段】上記対象装置のハードウェア構成を確認する構成確認処理と、構成確認処理で確認されたハードウェア構成に基づいて、このハードウェア構成に含まれている各ハードウェア要素に対する負荷の変動パターンを決定する決定処理と、構成確認処理で確認されたハードウェア構成に含まれている各ハードウェア要素を、決定処理で決定された変動パターンで動作させる動作処理と、動作処理での各ハードウェア要素の動作が正常であるか否かを確認する動作確認処理とを有する。

(もっと読む)

インタフェース障害処理方式、情報処理装置及びインタフェース障害処理方法

【課題】障害発生を契機として診断試験を実施する際に、情報処理装置が自ら動作電圧やクロック周波数などの動作環境を変更可能とすること。

【解決手段】インタフェース202の障害を処理する障害処理方式であり、情報処理装置201は、インタフェース202の診断試験の実行を含む制御を行うインタフェース制御手段203と、障害発生時に、診断試験の実施の通知と、診断試験の実行の指示とを行う障害処理制御手段204と、診断試験の実施通知を受けて診断試験実行時の動作環境の変更を指示する変更指示手段205と、変更指示を受けて診断試験実行時における動作電源電圧及び動作周波数を選択して選択した設定値を通知する動作環境選択手段206と、設定値の通知を受けて動作電源電圧の設定値を設定する電源制御手段207と、設定値の通知を受けて動作周波数の設定値を設定するCLK制御手段208と、を含む。

(もっと読む)

シリアル通信カード試験装置

【課題】大量の高速シリアルデータの送受信を複数回繰返す動作確認試験を試験員が手作業で行うことは長時間を要する。

【解決手段】一実施形態によれば、シリアル通信路と、基準シリアル通信カードと、被試験シリアル通信カードと、記憶部及びCPUを持つ第1の処理装置と、ネットワークと、記憶部及びCPUを持つ第2の処理装置と、これらの処理装置の各記憶部に各試験プログラムをロードし、操作指令を発行して各シリアル通信カード間の送受信を制御する制御装置とを備え、この制御装置は、各シリアル通信カードにシリアルデータの送受信を複数回繰返させ、送受信終了後、各記憶部からそれぞれ送受信データを収集し、データの相互比較により被試験シリアル通信カードの動作確認試験を行うシリアル通信カード試験装置が提供される。

(もっと読む)

競合試験装置

【課題】本発明の一実施例では、擬似アクセス信号発生手段を設けることなく、確実にアクセス競合を発生させる競合試験装置を提供することを目的とする。

【解決手段】プログラムを記憶する記憶部と、該記憶部に記憶されたプログラムを読み出し、読み出した該プログラムを実行する第1および第2の演算部と、該記憶部の同一アドレス空間に同時になされた読み出し要求に対するプログラムの転送処理を調停し調停結果を出力する調停部とを有する演算装置のアクセス競合試験を行う競合試験装置は、該記憶部の奇数個のアドレス空間にそれぞれ該調停部の調停動作を試験する試験プログラムを記憶させ、該記憶部に記憶された複数の試験プログラムを所定の順序に従って該第1の演算部に読み出させ、該記憶部に記憶された複数の試験プログラムを該所定の順序と逆の順序に従って該第2の演算部に読み出させ、該調停部の調停結果を記録する。

(もっと読む)

バックエンドでの通信の規格がSASであるストレージシステム

第1のコントローラ及び複数の記憶デバイス(PDEV)に接続された第1の通信経路と、第2のコントローラ及びそれら複数のPDEVに接続された第2の通信経路がある。各通信経路は、直列に接続された複数のエクスパンダを有する。通信経路がI/Oに使用されない時間を短くするために、(A)通信経路についてI/O抑止が設定されている時間長を短くする、又は、(B)I/Oの処理以外の処理(例えばディスカバープロセス)にかかる全体的な時間が短くされる。(A)では、I/O抑止の通信経路について、エクスパンダとエクスパンダ間の接続が切断されているか否かが判断され、その判断の結果が否定的であれば、その通信経路についてI/O抑止を解除してから、ディスカバープロセスが行われる。(B)では、エクスパンダが有するルーティング制御情報を更新するためのコマンドの発行数が減らされる。 (もっと読む)

データ転送システム,切替装置,診断方法及び診断プログラム

【課題】障害発生時の被疑箇所を容易に特定できるようにする。

【解決手段】情報処理装置20に対して、診断信号を送信させる診断信号送信制御部101と、切替装置10における診断信号の伝送経路上の複数の所定位置のそれぞれにおいて、診断信号を折り返して送信する複数の折り返し手段RE,ROと、各折り返し手段RE,ROに対して、診断信号を折り返させ折り返し信号として情報処理装置20に送出させる折り返し制御部103と、この折り返し制御部103によって送出させた折り返し信号に基づく診断結果に基づき、被疑箇所の特定を行なう特定部104とをそなえる。

(もっと読む)

半導体装置

【課題】バスシステムがロックされてしまった場合でも、容易に不具合の原因を特定することが可能な半導体装置を提供する。

【解決手段】複数の機能回路と、各機能回路に共有される内部バスとを備える半導体装置であって、前記内部バスを介して各機能回路が送受信する通信情報を収集及び保存する通信情報収集部を備える。

(もっと読む)

入出力接続装置、情報処理装置及び入出力デバイス検査方法

【課題】入出力デバイス内部の異常を早期に検出する。

【解決手段】生成部11は、パケットを一意に識別するタグを付与した検査用パケットを生成し、送信部12は、検査用パケットを入出力デバイスへ送信する。受信部13は、パケットを受信し、第1判定部14は、受信部13によって受信された受信パケットのタグに基づいて、該受信パケットが、送信部12から送信された検査用パケットに対する応答パケットであるか否かを判定する。第2判定部15は、第1判定部14によって受信パケットが応答パケットであると判定された場合に、受信パケットを解析して、入出力デバイスが異常であるか否かを判定する。

(もっと読む)

周辺デバイス部のオンラインテスト機能を備えたCPUボード、及びそのオンラインテスト方法

【課題】周辺デバイス部のオンラインテスト機能を備えたCPUボード、及びそのオンラインテスト方法を提供することを目的とする。

【解決手段】プログラムを実行するCPU1と、その周辺デバイス部3−1〜3−nと、周辺デバイス部に対して自己診断テストを実行するテスト回路部5と、前記CPUとテスト回路部とが、夫々異なる周辺デバイス部に同時アクセスを可能に接続するクロスバースイッチ型のバス制御部4とを備え、テスト回路部5は、CPUのアクセス予測を監視し、CPUが次にアクセスしない周辺デバイス部に対してテストを行う周辺デバイス部を求め、CPUが現在アクセス中の周辺デバイス部と異なる周辺デバイス部であり、且つ、次のバスサイクルでもアクセスしない周辺デバイス部を選択して自己診断テストを実行するようにしたことを特徴とする。

(もっと読む)

AXI転送発生装置、AXI転送発生方法及びAXI転送発生プログラム

【課題】AXI仕様を用いたデータを転送する処理において、発行転送数を拡大することができるAXI転送発生装置を提供することを目的とする。

【解決手段】AXI仕様を用いてデータを転送する処理を実行するAXI転送発生装置100であって、転送制御情報を動的に生成して格納する動的生成手段101と、動的生成手段101が動的に生成して格納した転送制御情報に基づいて、データを転送する処理を実行する転送制御手段102とを備えたことを特徴とする。

(もっと読む)

障害箇所推定システム、障害箇所推定装置および障害箇所推定方法

【課題】ネットワークの異常の原因となる範囲を絞り込み、システムのトラブル調査を支援すること。

【解決手段】障害箇所推定システム10の関連クラス適用部11は、構成情報21、関連クラス適用ルール22および関連クラス23を参照し、構成情報21に含まれる構成要素間の関係について、関連クラス適用ルール22に基づいて関連クラスを適用する。調査範囲限定部12は、関連クラス23、調査内容24、異常検知情報25を参照して、異常が発生した構成要素の各々について調査範囲に従って辿った構成要素及び関連を調査範囲限定ツリーとして求める。障害発生箇所候補推定部13は、異常が発生した構成要素の各々について求めた調査範囲限定ツリーにおける構成要素の出現頻度に基づいて異常の原因となる障害が発生した箇所の候補を推定する。

(もっと読む)

試験方法、試験プログラム、試験装置、及び試験システム

【課題】従来の試験方法に比べて、試験効率を向上することができる試験方法、試験プログラム、試験装置及び試験システムを提供する。

【解決手段】本体装置2から切断された外部記憶装置にアクセスするCPUが、データ転送命令が正常終了するまで、データ転送命令の実行、及び保存された初期値の再設定を繰り返す。これにより、データ転送命令が正常終了した場合に、本体装置2に接続される全ての外部記憶装置に書き込まれた複数のデータ、又は本体装置2に接続される全ての外部記憶装置から読み出された複数のデータは互いに一致する。よって、データの復元処理の実行、及び試験の停止が不要になる。

(もっと読む)

無線通信端末

【課題】通信アナライザなどの測定器を接続することなく、DTEインタフェースのトレースログを取得することが可能なデータ通信用無線端末を提供する。

【解決手段】無線通信によって基地局と通信を行う通信部と、他の外部装置に接続されデータを入出力する入出力処理部と、上記入出力処理部により入出力されるデータを記憶する記憶部と、上記入出力処理部や上記記憶部および上記通信部を制御する制御部とを具備し、上記制御部は、上記通信部により受信した上記外部装置の動作状態のデータ取得要求に応じて上記入出力処理部から上記外部装置の動作状態のデータを取得し上記記憶部へ記憶した後に上記通信部を介して無線により上記記憶部に記憶した上記外部装置の動作状態のデータを送信する、ことを特徴とする無線通信端末。

(もっと読む)

シリアルデータ通信装置

【課題】再送の頻度を少なくして転送レート及び信号品質を安定させることができるシリアルデータ通信装置を提供する。

【解決手段】リンクトレーニング制御部22が、リンクトレーニング中にエラー集計部21bが集計したエラー数がエラー閾値設定部21cに設定されたエラー数の閾値を超えたレーンを検出した際は、エラー数の閾値を超えたレーンを除いてリンクアップする。

(もっと読む)

拡張カード、障害診断処理方法、情報処理装置及び障害診断処理プログラム

【課題】ホストと、複数のレーンからなるインタフェースを介して、ホストとの間でデータの送受信を行うアドインカードとを含むコンピュータシステムにおいて、障害診断機能を持たないホストでも、信頼性の高いシステムの構築を可能にする。

【解決手段】アドインカード2は、複数のレーンからなるPCI Expressのインタフェースを介して、マザーボード1との間でデータの送受信を行う送受信部3を有し、該送受信部3は、電源投入時に各レーンの自己診断を実施し、自己診断の結果にもとづいて、有効レーン数を切り換える。

(もっと読む)

インタフェース回路および通信システム

【課題】インタフェース動作時テストにおけるオーバヘッドサイクルを削減でき、テストの実施を容易とすることが可能なインタフェース回路および通信システムを提供する。

【解決手段】インタフェース回路13は、アクセスを受け付ける1組以上の第1の入出力端子群131と、アクセス対象機器へのアクセスを発行しうる1組以上の第2の入出力端子群132と、設定値に応じてアクセス対象機器12へのアクセス特性を制御可能な各種設定回路133と、各種設定回路に与える全設定値を格納する第1の設定値レジスタ134と、各種設定回路に与える一部または全部の設定値を格納する第1の設定値レジスタとは別の第2の設定値レジスタ135と、各種設定回路133へ与える設定値を第1の設定値レジスタ134または第2の設定値レジスタ135から選択可能な設定値レジスタ選択器133とを有する。

(もっと読む)

1 - 20 / 102

[ Back to top ]