Fターム[5B125CA11]の内容

リードオンリーメモリ (43,397) | 目的、効果 (6,321) | 安定化、誤動作防止 (2,478)

Fターム[5B125CA11]の下位に属するFターム

供給電圧変動、電源供給遮断時の対処 (130)

温度変動対処 (70)

バラツキ対処 (388)

ノイズ対処 (169)

破壊防止、過電圧、過電流対処 (104)

過消去対処 (97)

過書込対処 (52)

ディスターブ対処 (515)

クロストーク対処 (145)

タイミング、電圧マージンの確保、拡大 (371)

Fターム[5B125CA11]に分類される特許

1 - 20 / 437

メモリシステム及びそれのブロック複写方法

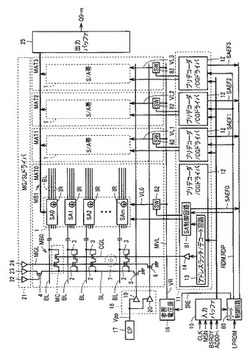

不揮発性半導体記憶装置

【課題】低消費電流で正確なデータ読出を行なうことが可能な不揮発性半導体記憶装置を提供する。

【解決手段】このフラッシュメモリでは、4つのメモリマットMAT0〜MAT3の各々にセンスアンプSA0〜SAmを設け、通常の読出動作モードでは、全メモリマットMAT0〜MAT3のセンスアンプSA0〜SAmに参照電圧VRを供給し、低速読出モードでは、選択されたメモリマットMATのセンスアンプSA0〜SAmのみに参照電圧VRを供給する。したがって、低消費電力で正確なデータ読出を行なうことができる。

(もっと読む)

3次元不揮発性メモリ素子及びその製造方法

【課題】消去動作の際、充分な量の正孔を生成させて消去特性を確保することができる3次元不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】基板から突出されたチャンネル膜と、チャンネル膜に沿って積層された複数のメモリセルと、チャンネル膜の一側端と繋がれたソースラインと、チャンネル膜の他側端と繋がれたビットラインと、チャンネル膜の一側端とソースラインとの間に介在されて、Pタイプの不純物がドープされた第1ジャンクションと、チャンネル膜の他側端と前記ビットラインとの間に介在されて、Nタイプの不純物がドープされた第2ジャンクションと、を含む。

(もっと読む)

不揮発性メモリ装置及びそのソフト判定読出し方法

【課題】不揮発性メモリ装置に対して、読出し/プログラム時間を短縮できる、向上された読出しスキームを提供する。

【解決手段】本発明の一特徴に係る不揮発性メモリ装置のソフト判定読出し方法は、ソフト判定読出し命令を受信し、選択されたワードラインへ読出し電圧を印加し、前記選択されたワードラインの選択されたメモリセルに各々連結されたビットラインをプリチャージし、前記ビットラインのプリチャージされた電圧及び前記選択されたワードラインに供給された読出し電圧は変化されない状態で、前記選択されたメモリセルの状態を連続的に感知することを含む。

(もっと読む)

半導体記憶装置およびデータ書込み方法

【課題】MOS構造を有する各メモリセルにおいて信頼性が高い2ビットのデータの記憶が容易な半導体記憶装置およびデータ書込み方法を提供する。

【解決手段】MOS構造を有するメモリセル10は、ゲート電極13の第1半導体領域121側に設けられた第1記憶部141と、ゲート電極13の第2半導体領域122側に設けられた第2記憶部142とを有する。第1記憶部141に電子を保持させる第1電荷移動ステップと、第2記憶部142に電子を保持させる第2電荷移動ステップとを交互に行うことで、第1記憶部141および第2記憶部142の双方に所定量の電子を保持させる。

(もっと読む)

不揮発性半導体記憶装置

【課題】不良ブロック情報を適切に管理することのできる不揮発性半導体記憶装置を提供する。

【解決手段】一の実施の形態に係る不揮発性半導体記憶装置は不揮発にデータを記憶する複数のメモリセルを配列してなる複数のブロック、並びにメモリセルと接続されるワード線、及びビット線を有するメモリセルアレイと、メモリセルアレイ内に設けられ、ブロックが不良ブロックであること示す不良ブロック情報を不揮発に記憶可能に構成された不良ブロック格納領域と、ワード線を選択するロウデコーダと、メモリセルに対するデータの書き込み、消去及び読み出しを制御する制御回路とを備える。制御回路は、不良ブロック格納領域に書き込まれた不良ブロック情報をビット線を介して外部へ出力する出力動作を実行可能に構成されるとともに、外部から入力された不良ブロック情報をビット線を介して不良ブロック格納領域に書き込む第1の書き込み動作を実行可能に構成される。

(もっと読む)

フラッシュメモリの制御装置

【課題】フラッシュメモリの寿命を延ばすことができる、フラッシュメモリの制御装置を提供する。

【解決手段】フラッシュメモリの複数のブロックを、低頻度データブロックと高頻度データブロックに分ける。低頻度データブロックには、更新頻度の低いデータとして予め設定された低頻度データを記憶する。一方、高頻度データブロックには、更新頻度の高いデータとして予め設定された高頻度データを記憶する。そして、フラッシュメモリに新たに記憶させるデータの種類が低頻度データであれば低頻度データブロックに記憶させ、高頻度データであれば高頻度データブロックに記憶させる。

(もっと読む)

半導体記憶装置

【課題】データの信頼性を向上可能な半導体記憶装置を提供する。

【解決手段】m個のページ(mは自然数)を含むメモリセルアレイと、書き込み動作を制御する制御回路とを備え、n番目のページ(1≦n≦mを満たす自然数)のメモリセルに書き込み動作で、(n+1)番目からm番目のページのメモリセルが消去状態とは異なる閾値を有するデータを保持するとき、前記制御回路は、フェイルを出力する。

(もっと読む)

半導体装置

【課題】

実施形態は、ベリファイ動作の誤判定を低減可能な半導体装置を提供する。

【解決手段】

本実施形態の半導体装置は、メモリセルを含むメモリセルアレイと、ビット線と、センスアンプと、制御部とを備え、センスアンプは、外部から入力された第1又は第2テストデータと第1又は第2ページのメモリセルに保持された保持データとを比較するテスト工程で、第1テストデータと第1ブロックの第1ページに対応する保持データとを比較した後に、第1テストデータと第2ブロックの第1ページに対応する保持データとを比較し、第1テストデータとは異なる第2テストデータと第1ブロックの第2ページに対応する保持データとを比較した後に、第2テストデータと第2ブロックの第2ページに対応する保持データとを比較することを特徴とする。

(もっと読む)

不揮発性半導体記憶装置

【課題】データの劣化を抑制した不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルは、半導体層、電荷蓄積層、及び導電層を備える。半導体層は、半導体基板に対して垂直方向に延び、メモリセルのボディとして機能する。電荷蓄積層は、半導体層の側面に設けられ、電荷を蓄積する。導電層は、半導体層と電荷蓄積層を挟むよう設けられ、メモリセルのゲートとして機能する。制御回路は、第1プログラム動作の後、第2プログラム動作を実行する。第1プログラム動作は、メモリセルのボディに第1電圧を印加し且つメモリセルのゲートに第1電圧よりも大きい第2電圧を印加することによりメモリセルの閾値電圧を正方向に移動させる動作である。第2プログラム動作は、メモリセルのボディをフローティングにし且つメモリセルのゲートに正の第3電圧を印加する動作である。

(もっと読む)

半導体記憶装置

【課題】製造ばらつきにより生じる不良ブロックを判定可能な半導体記憶装置を提供する。

【解決手段】メモリセルと、複数の前記メモリセルを含むページ、複数の前記ページを含むブロックを有するメモリセルアレイと、前記ページのうち、第1カラムに対応する第1メモリセルにデータを書き込むとき、プログラム動作を繰り返した第1回数を保持する第1記憶部63と、前記ページのうち、前記第1カラムとは異なる第2カラムに対応する第2メモリセルにデータを書き込むとき、プログラム動作を繰り返した第2回数を保持する第2記憶部64と、第1回数と第2回数の差が規定値を超えたとき、前記第1メモリセルと前記第2メモリセルとを含むブロックを不良ブロックとして登録する制御部6とを備える。

(もっと読む)

不揮発性メモリ装置、不揮発性メモリ装置の消去方法、不揮発性メモリ装置の動作方法、不揮発性メモリ装置を含むメモリシステム、メモリシステムの動作方法、不揮発性メモリ装置を含むメモリカード、及びソリッドステートドライブ

【課題】向上された信頼性を有する不揮発性メモリ装置、不揮発性メモリ装置の消去方法、不揮発性メモリ装置の動作方法、不揮発性メモリ装置を含むメモリシステム、及びメモリシステムの動作方法が提供される。

【解決手段】本発明の消去方法は複数のメモリセルに消去電圧を供給する段階、複数のメモリセルのワードラインに読出し電圧に読出し動作を遂行する段階、及び複数のメモリセルのワードラインの少なくとも1つのワードラインに消去検証電圧を利用して消去検証動作を遂行する段階を含む。消去検証電圧は読出し電圧より低い。

(もっと読む)

半導体装置

【課題】テスト時間の短縮化を図ることが可能な半導体装置を提供する。

【解決手段】このチャージポンプ回路12では、通常動作時は、ポンプキャパシタC0,C2の一方電極にポンプクロック信号φPを与えるとともにポンプキャパシタC1,C3の一方電極にポンプクロック信号φPの相補信号を与え、ポンプキャパシタC0〜C3の欠陥を検出するテストモード時は、ポンプキャパシタC0〜C3の各々の電極間に外部電源電圧VCCを静的に印加する。したがって、MOSトランジスタのオン耐圧を超える高電圧をポンプキャパシタC0〜C3に印加できるので、テスト時間を短縮化できる。

(もっと読む)

メモリ回路

【課題】電源投入時における誤書き込みが発生しにくいメモリ回路を提供する。

【解決手段】メモリ回路10は、書き込み時のみにソース・ドレイン間に電圧を印加されて書き込まれる、書き込み用のPチャネル型不揮発性メモリ素子15と、コントロールゲート及びフローティングゲートがPチャネル型不揮発性メモリ素子15のコントロールゲート及びフローティングゲートとそれぞれ共通にされ、読み出し時のみにソース・ドレイン間に電圧を印加されて読み出される、読み出し用のNチャネル型不揮発性メモリ素子16と、を備える。

(もっと読む)

半導体記憶装置及びその試験方法

【課題】ローデコーダ側に配置される転送トランジスタの特性評価を実施する。

【解決手段】一つの実施形態によれば、半導体記憶装置は、切り替え部、第一の転送トランジスタ、第一のトランジスタ、及び第二のトランジスタが設けられる。切り替え部が第一の状態のときに第一及び第二のトランジスタがオフし、第一の転送トランジスタがオンし、切り替え部が第二の状態のとき第一及び第二のトランジスタがオンする。

(もっと読む)

半導体装置

【課題】データの信頼性の向上を実現可能な半導体装置を提供する。

【解決手段】例えば、それぞれ独立の内部電源生成回路VGEN1〜VGEN3を持つ3個の不揮発性メモリモジュールFMD1〜FMD3を備える。外部書き込みデータが入力された際には、それを2分割したデータの一方がFMD1のデータ領域DT[1a]に書き込まれ、他方がFMD2のデータ領域DT[1b]に書き込まれる。更に、この2分割したデータによってパリティデータが生成され、それがFMD3のデータ領域PT[1]に書き込まれる。このDT[1a],DT[1b],PT[1]への書き込みは、互いに重複しない期間で行われ、また、各データ領域(例えばDT[1a])に書き込みを行う前後で対応する書き込みスタンプ領域(例えばPS[1a])に識別子が書き込まれる。

(もっと読む)

不良ビットエラーを処理するシステムおよび方法

【課題】半導体不揮発性メモリ装置における不良ビットエラーを補償する。

【解決手段】装置は、メモリ装置120から古いページを受け取り、そのページが不良ビットを有するか否かを決定する不良ビット検出モジュール116を含む。装置は、新しいページを生成する不良ビット修正モジュール118を含む。不良ビット修正モジュール118は、不良ビットの位置を特定し、不良ビットの好適値を決定し、不良ビットのユーザ値を決定する。不良ビット修正モジュール118は、古いページの実質的なデータに対応するビット列に好適値を挿入し、好適値が挿入されたビット列を記録する。不良ビット修正モジュール118は、古いページのアドレスに新しいページを格納する。

(もっと読む)

半導体記憶装置

【課題】ベリファイ・フェイル数を精度良くカウント可能な半導体記憶装置を提供すること。

【解決手段】実施形態の半導体記憶装置1は、複数のメモリセルMTと、論理ゲートチェーン52と、カウンタ30を備える。メモリセルMTは、いずれかのカラムに関連付けられ、データ保持可能である。論理ゲートチェーン52は、いずれかのカラムに対応付けられ、且つ対応付けられたカラムにおけるベリファイ・フェイルの有無を示す論理レベルを次段に出力するように直列接続された複数の論理ゲート51を含む。カウンタ30は、直列接続の最終段の論理ゲートによる、ベリファイ・フェイルがあることを示す論理レベルの出力回数をカウントする。論理ゲートチェーン52は、各々の論理ゲート51の出力する論理レベルの示す内容が、ベリファイ・フェイルのあるカラムに対応する論理ゲート51を境界にして反転するように構成される。

(もっと読む)

半導体記憶装置及びその制御方法

【課題】半導体記憶装置に対する書き込み/読み出しに影響を与えることなく、読み出し時にエラー訂正されたデータを、メモリ本体に再書き込みする。

【解決手段】実施形態に係る半導体記憶装置1は、エラー訂正部9、第1の記憶部10、第2の記憶部11、制御部13を含む。エラー訂正部9は、メモリ本体8から読み出されたデータに対するエラー訂正を行う。第1の記憶部10は、エラー訂正部9によって訂正されたデータを記憶する。第2の記憶部は、エラー訂正部9によって訂正されたデータに対応するアドレスを記憶する。制御部13は、メモリ本体8に対する読み出し/書き込みが実行されていないタイミングにおいて、第1の記憶部10に記憶されているデータと第2の記憶部11に記憶されているアドレスに基づいて、メモリ本体8に対して再書き込みを行う。

(もっと読む)

不揮発性半導体メモリ

【課題】プログラム後の読み出し不良をプログラム動作の終了前に判定する。

【解決手段】実施形態に係わる不揮発性半導体メモリは、選択ワード線に対する書き込みパルスの印加とベリファイ読み出し動作とを繰り返す第1の手段(ステップST1〜ST5)と、ベリファイ回路によりプログラムデータの記録が完了と判断された後に選択メモリセルに対して読み出し動作を行う第2の手段(ステップST6)と、この読み出し動作により読み出されたデータとプログラムデータとが一致するときに外部コントローラにプログラム動作がパスしたことを示すステータス情報を出力し、両者が一致しないときに外部コントローラにプログラム動作がフェイルしたことを示すステータス情報を出力する第3の手段(ステップST7)とを備える。

(もっと読む)

1 - 20 / 437

[ Back to top ]