Fターム[5B125EB04]の内容

リードオンリーメモリ (43,397) | EEPROMセルへの電荷注入、放出構成 (1,604) | 注入、放出方向が特定されているもの (305) | ドレイン側から注入又は放出 (95)

Fターム[5B125EB04]に分類される特許

1 - 20 / 95

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

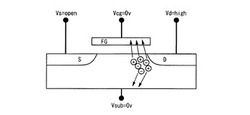

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

メモリのプログラミング方法及びメモリアレイ

【課題】クリティカル・ディメンションの変動に鈍感であり且つ高速なメモリプログラミング方法等を提供する。

【解決手段】メモリの複数のメモリセルの夫々は、ウェルと、ソース及びドレイン領域と、記憶レイヤと、ゲートとを有する。メモリセルはマトリクス状である。同じ列ドレイン領域は同じビットラインへ接続し、同じ行ゲートは同じワードラインへ接続し、同じ列ソース領域は同じソースラインへ接続する。メモリは、いずれかのメモリセルへ電気的に接続されたワードラインへ第1の電圧を印加し、そのメモリセルへ電気的に接続されたビットラインへ少なくともプログラミング閾値だけ第1の電圧と異なる第2の電圧を印加し、そのメモリセルへ電気的に接続されたソースラインへ少なくともプログラミング閾値だけ第1の電圧と異なる第3の電圧を印加し、複数のメモリセルへ基板電圧を印加することによって、プログラミングされる。

(もっと読む)

不揮発性半導体記憶装置及びICカード

【課題】ピーク電流を低減する。

【解決手段】不揮発性半導体記憶装置10は、不揮発性メモリ11と、電圧発生回路24と、検知回路25とを含む。電圧発生回路24は、チャージポンプ30と、チャージポンプ30を動作させるクロックを生成するオシレータ32とを有し、かつ不揮発性メモリ11に電圧を供給する。検知回路25は、外部からの電源電圧を監視し、電源電圧が特定のレベルより低くなったことを検知する。電圧発生回路24は、電源電圧が特定のレベルより低くなった場合に、クロックの周波数を低くする。

(もっと読む)

半導体不揮発性メモリ装置

【課題】 占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】 ドレイン領域内のトンネル領域と微細穴に埋め込まれる形で形成されたフローティングゲート電極の側面との間にはトンネル絶縁膜を設け、微細穴に接するドレイン領域の表面付近には、電気的にフローティング状態である第1導電型のトンネル防止領域を設けた。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得ることを目的とする。

【解決手段】ドレイン領域内のトンネル領域には、ドレイン領域と同一の電位に固定されたドレイン領域に比べて不純物濃度の低い第2導電型の領域と、不純物濃度の低い第1導電型の領域とを形成し、不純物濃度の低い第2導電型の領域と、不純物濃度の低い第1導電型の領域のそれぞれの上面に、フローティングゲート電極への電子注入用と電子引き抜き用のトンネル絶縁膜を独立して設けた。また、データ書き換え時に印加されるストレスが偏らないように、電子引き抜き用のトンネル絶縁膜に比べて電子注入用のトンネル絶縁膜の面積を大きくあるいは厚くした。

(もっと読む)

半導体記憶装置へのデータの書込み方法及び半導体記憶装置

【課題】半導体記憶装置のメモリセルの参照セルとなる副記憶領域の読出し電流の変動を抑制して、メモリセルの読出し電流の判定時における誤判定を低減することができる半導体記憶装置へのデータの書込み方法及び半導体記憶装置を提供する。

【解決手段】メモリセルの第1不純物領域及び第2不純物領域に印加される電圧の大小関係が互いに異なる2つのデータ書込みステップによってメモリセルにデータの書込みをなす。

(もっと読む)

半導体メモリ

【課題】ビット線間の寄生容量による影響を低減することにより、高精度のデータの読出しを可能にする半導体メモリを提供する。

【解決手段】1つの主ビット線に互いに異なるタイミングでオン駆動するセレクタ素子及び当該セレクタ素子のそれぞれに接続された副ビット線を介して当該副ビット線のそれぞれにメモリセルが接続され、当該主ビット線に並置されるとともに固定電位に接続された固定電位線が設けられていること。

(もっと読む)

半導体不揮発性メモリ

【課題】 本発明は、不揮発性メモリ・セルにおける電荷貯蔵層を論理工程において形成する方法を提供する。

【解決手段】 論理工程において不揮発性メモリ・セルにおける電荷貯蔵層を形成する方法は、基板のアクティブ領域の上にセレクト・ゲートを形成するステップ、その基板のアクティブ領域に部分的に重なる長いポリシリコン・ゲートを形成するステップ、及びその長いポリシリコン・ゲートの間に電荷貯蔵層を充填するステップを含む。

(もっと読む)

不揮発性半導体記憶装置及びその駆動方法

【課題】選択トランジスタの占有面積を縮小して、セルの配置効率を向上できるようにする。

【解決手段】ゲート電極が列方向に延伸する第1の選択ワード線23と接続され、ソースが第1の副ビット線20と接続され、ドレインが行方向に延伸する第1の主ビット線22と接続された第1の選択トランジスタ21と、ゲート電極が列方向に延伸する第2の選択ワード線33と接続され、ソースが第2の副ビット線30と接続され、ドレインが行方向に延伸する第2の主ビット線32と接続された第2の選択トランジスタ31とを有している。第1の副ビット線20は、第1の選択トランジスタ21により、同時に消去される複数のメモリセル1ごとに電気的に分離して制御される。一方、第2の副ビット線30は、第2の選択トランジスタ31により、別々に消去される複数のメモリセル1に共通に接続されている。

(もっと読む)

不揮発性半導体メモリ

【課題】データ書込み時における電流量の変化を抑制し、メモリセルへのデータ書込みを高精度に行うことができる不揮発性半導体メモリを提供する。

【解決手段】複数のメモリセルと、複数のメモリセルに接続されたワード線と、複数のメモリセルの各々に接続されたビット線と、を含み、ビット線から少なくとも2つを選択し、選択されたビット線に接続されたメモリセルに対して、電源供給ラインから同時に電流を供給してデータを書込む不揮発性半導体メモリであって、複数のメモリセルの各々に蓄積された電荷量を測定する電荷量測定部と、ビット線の各々に接続された電流路切替回路と、を有し、選択されたビット線に接続された電流路切替回路は、電荷量測定部による電荷量の測定値に応じて、メモリセル又は所定端子のいずれかに対して選択的に電源供給ラインから電流を供給すること。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の動作方法

【課題】不揮発性半導体メモリの保持特性の悪化を抑制しつつ、消去動作に要する時間を短縮する。

【解決手段】(a)メモリセルアレイのデータ消去対象領域に消去パルスを印加するステップと、(b)データ消去対象領域に配置されたメモリセルの閾値電圧が消去レベルに達したか否かを判定するステップと、(c)ベリファイ結果に基づいて、新たな消去パルスを印加するか、待機状態に移行するかを決定するステップとを具備する方法で、不揮発性半導体メモリの消去動作を実行する。(b)ステップは、消去パルスの印加が行われた印加期間が経過した後、待機状態に移行する前に閾値電圧が消去レベルに達したか否かを判定する。(c)ステップは、閾値電圧が消去レベルに達していないとき、データ消去対象領域に新たな消去パルスを印加するステップと、閾値電圧が消去レベルに達しているとき、新たな消去パルスの印加を禁止するステップとを含む。

(もっと読む)

不揮発性フラッシュメモリ

【課題】低消費電力、低減されたリーク問題、および単純なプロセスを伴った新規なフラッシュメモリ、新規なプログラミング方法、およびそのセンシングスキームを提供する。

【解決手段】ワード線218、第1のビット線204、および第2のビット線206を備えた不揮発性メモリセル200を動作させる方法は、メモリセル200をプログラミングする工程を有し、そのプログラミングする工程が、高い正電圧のバイアスを第1のビット線に印加し、接地バイアスを第2のビット線に印加し、高い負電圧のバイアスをワード線に印加することを備え、正帯電ホールが誘電体層212を介してトラッピング層214に突き抜けるようにする。

(もっと読む)

半導体不揮発記憶回路

【課題】データが書き込まれていない状態(製造直後の状態)で、データ読み出し時の出力論理が不定とならない不揮発性メモリセルを提供する。

【解決手段】半導体不揮発記憶回路は、1ビットのデータを格納するメモリセルCELとして、第1トランジスタN1と、第1トランジスタN1よりもオン電流の高い第2トランジスタN2と、を一対としたトランジスタペアを集積化して成り、前記メモリセルは、第2トランジスタN2のオン電流が第1トランジスタN1のオン電流よりも高い状態をデータ「0」の記憶状態とし、逆に第2トランジスタN2のオン電流が第1トランジスタN1のオン電流よりも低い状態をデータ「1」の記憶状態とする。

(もっと読む)

フラッシュEPROMの閾値電圧降下方法及びその構造

【課題】過剰にプログラムされた電界効果トランジスタ(FET)不揮発性メモリ(NVM)セルに応用する閾値電圧降下方法を提供する。

【解決手段】(a)第一電圧と第二電圧を過剰にプログラムされたFET NVMセルのコントロールゲートとボディにそれぞれ印加する。(b)所定時間内に、信号を前記過剰にプログラムされたFET NVMセルのドレインに印加して、有限閾値電圧減少量を生じさせる。そのうち、前記第一電圧と第二電圧の極性は、前記信号の極性に相反する。これにより、蓄積材料中の電荷配置を特定電荷状態の小さい範囲内に正確に制御し、更に、高デジタル蓄積密度を達成することができる。

(もっと読む)

電荷を非対称に捕獲する多値メモリセル

【課題】高メモリ密度、低電力消費、及び高信頼性を達成可能なNAND型多値メモリセルを提供する。

【解決手段】NAND型多値メモリセルは、2つのドレイン/ソース領域を基板に有する。2つのドレイン/ソース領域の間における基板の上方には、酸化物−窒化物−酸化物構造体が形成される。このうち窒化物層は、電荷を非対称に捕獲する層として機能する。酸化物−窒化物−酸化物構造体の上方には、制御ゲートが配置される。ドレイン/ソース領域に非対称のバイアスをかけることで、ドレイン/ソース領域に高い電圧が生じ、これによってドレイン/ソース領域の略近傍における電荷捕獲層にGIDL(ゲートに起因するドレインでの電流漏れ)正孔注入処理を行い、正孔を非対称な分布で注入する。

(もっと読む)

マルチドットフラッシュメモリ

【課題】マルチドットフラッシュメモリの書き込み/消去の低消費電力化を図る。

【解決手段】本発明の例に係わるマルチドットフラッシュメモリは、書き込み/消去の対象となる選択されたフローティングゲートの左側に存在するビット線BL13,BL12,BL11,…の電位V2(1), V2(2), V2(3),…を、V2(1)>V2(2)>V2(3)>…とし、選択されたフローティングゲートの右側に存在するビット線BL14,BL15,BL16,…の電位V1(1), V1(2), V1(3),…を、V1(1)<V1(2)<V1(3)<…とする。但し、V2(1)は、プラス電位、V1(1)は、マイナス電位である。また、ビット線の電位は、選択されたフローティングゲートから離れるに従い、0Vに収束する。

(もっと読む)

不揮発性半導体集積回路装置

【課題】不揮発性半導体集積回路装置のチップサイズを縮小させる。

【解決手段】シリコン基板上に隣り合って配置された第1および第2ゲート電極とそれらの側方下部のシリコン基板に形成された一対のソース・ドレイン領域とを有し、第2ゲート電極とシリコン基板との間に配置された第2ゲート絶縁膜に電荷を蓄えることで情報を記憶するメモリセルにおいて、メモリセルの消去動作時には、消去非選択セルの第1ゲート電極に正電圧を印加する。

(もっと読む)

集積回路デバイス、集積回路デバイスの製造方法およびデータとコードの保存方法

【課題】電気的に書き込み可能かつ消去可能な不揮発性メモリを有する集積回路デバイスの製造方法およびデータとコードの保存方法を提供する。

【解決手段】第1の動作アルゴリズムに従って第1のデータ用途のためのデータを保存する第1のメモリアレイと、第2の動作アルゴリズムに従って第2のデータ用途のためのデータを保存する前記半導体基板上の第2のメモリアレイと、を備え、前記第1のメモリアレイと前記第2のメモリアレイにおける電荷蓄積不揮発性メモリセルは、窒化物電荷トラッピング構造を備えた互いに略同一構造を有する複数のフラッシュメモリセルを含み、前記第1の動作アルゴリズムは、ホール注入によって書き込みすることと、電界アシストエレクトロン注入によって消去することを含み、前記第2の動作アルゴリズムは、エレクトロン注入によって書き込みすることと、ホール注入によって消去することを含むことを特徴とする集積回路デバイス。

(もっと読む)

半導体記憶装置

【課題】誤書込みやアクセス遅延等の発生しない半導体記憶装置を提供する。

【解決手段】書込み制御回路30Aは、ドレイン駆動電位MCDを、制御信号 ̄PGMがHレベルのときに0.8Vとし、LレベルのときにVCC+2Vtn(6V)とし、ワード線駆動回路200,…は、選択すべきワード線の電位を制御信号 ̄PGMがHレベルのときにVCC(4V)とし、LレベルのときにVPP(10V)とし、データ書込み回路40C,…は、制御信号 ̄PGMがLレベルへ切り替わったときには、ソース駆動電位BLA1,BLA2を、データD1,D2が採るべき論理値に応じた電位とする。

(もっと読む)

不揮発性半導体記憶装置並びにその駆動方法

【課題】 注入効率が高く、書き込まれた情報が安定的に保持される不揮発性半導体記憶装置並びにその駆動方法を提供する。

【解決手段】 メモリセル1は、N型基板2上に、P型の不純物拡散領域3,4を離間して形成し、両領域間に係る前記基板上において、不純物拡散領域3に隣接して形成された第一積層部15と、不純物拡散領域4に隣接し前記第一積層部15と離間して形成された第二積層部16を備える。メモリセル1に対する書き込み処理時において、第一ゲート電極8に対し、同ゲート電極下方に位置する基板2の表面が弱反転状態となる条件の第一負電圧を印加し、第二ゲート電極10に対し、前記第一負電圧よりも絶対値の大きい第二負電圧を印加し、不純物拡散領域4に対して前記第一負電圧よりも絶対値の大きいドレイン電圧を印加し、不純物拡散領域3に対して、前記ドレイン電圧よりも電位の高いソース電圧をそれぞれ印加する。

(もっと読む)

1 - 20 / 95

[ Back to top ]