Fターム[5B125FA01]の内容

リードオンリーメモリ (43,397) | 図面、表情報 (5,864) | フローチャート (1,667)

Fターム[5B125FA01]に分類される特許

1 - 20 / 1,667

メモリシステム及びそれのブロック複写方法

不揮発性半導体メモリおよびそのデータの読出し方法

半導体記憶装置

ホスト装置、装置、システム

暗号化演算装置を搭載する不揮発性半導体記憶装置

メモリカード、ストレージメディア、及びコントローラ

不揮発性メモリ装置及び不揮発性メモリ装置を制御するコントローラの動作方法

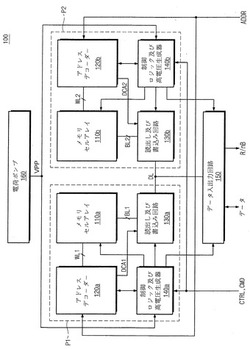

【課題】向上された動作速度を有する不揮発性メモリ装置及び不揮発性メモリ装置を制御するコントローラの動作方法を提供する。

【解決手段】本発明の不揮発性メモリ装置は、データのプログラム、読出し又は消去を遂行する第1プレーン、データのプログラム、読出し又は消去を遂行する第2プレーン、及び第1プレーン又は第2プレーンから共通バスを通じて伝送されるデータを外部へ出力し、外部から受信されるデータを、共通バスを通じて第1プレーン又は第2プレーンへ伝送するデータ入出力回路を含む。第1プレーンでプログラム、読出し又は消去が遂行される時、データ入出力回路は共通バスを通じて第2プレーンとデータを交換する。

(もっと読む)

半導体ディスク寿命監視装置

【課題】不揮発性の半導体ディスクの寿命を監視する半導体ディスク寿命監視装置を提供する。

【解決手段】半導体ディスク5−1〜5−Kの書込み制御を行うファイルシステム3と、当該ファイルシステム3と前記半導体ディスク5−1〜5−Kを接続するインタフェースドライバ4を備え、当該インタフェースドライバ4により書込みが行われる半導体ディスク5−1〜5−Kの寿命を予測する半導体ディスク寿命監視装置1であって、前記ファイルシステム3からの書込みを書込情報として測定する測定部7と、前記測定結果を累積し第1の保存データ32として保存する保存部8と、前記保存した累積書込情報に基づいて、半導体ディスク5−1〜5−Kの寿命を予測する。

(もっと読む)

メモリシステム及びそれの動作方法

【課題】動作速度及び電力消耗を減らすことができるメモリシステム及びそれの動作方法が提供される。

【解決手段】本発明の実施形態によるメモリシステムは不揮発性メモリ装置と、前記不揮発性メモリ装置を制御するように構成されたメモリ制御器と、を含み、前記メモリ制御器は前記不揮発性メモリ装置から読み出されたデータのエラーの位置情報を含むエラーフラッグ情報を前記不揮発性メモリ装置へ提供する。

(もっと読む)

半導体記憶装置

【課題】インタリーブ動作を実行可能に構成され且つLMアドレススキャン動作を実行する半導体記憶装置における消費電力の削減、及び動作の高速化を図る。

【解決手段】複数のカラムのうちの少なくとも1つは、複数ビットのデータの書き込み動作の進行状況を示すLMフラグデータを記憶するためのLMカラムである。カラム制御回路の各々は、対応するメモリコアにLMカラムが存在するか否かを確認するためのLMアドレススキャン動作をする。そのLMアドレススキャン動作の結果をレジスタに格納し、その後の各種動作においては、前記データラッチ回路に保持されたデータが第1のデータである場合、そのメモリコアにおいて前記LMカラムからLMフラグデータを読み出す動作を実行する一方、前記レジスタに保持されたデータが第2のデータである場合、そのメモリコアにおいて前記LMカラムからLMフラグデータを読み出す動作を実行しない。

(もっと読む)

不揮発性メモリ装置、不揮発性メモリ装置のプログラム方法、不揮発性メモリ装置を含むメモリシステム

【課題】向上された信頼性を有する不揮発性メモリ装置のプログラム方法が提供される。

【解決手段】本発明のプログラム方法は、第1メモリセルトランジスターの閾値電圧がプログラム状態から移動する傾向を判別する段階と、判別結果に応答して、複数の検証電圧の中で第1検証電圧を選択する段階と、第1メモリセルトランジスターの閾値電圧が変化するように第1メモリセルトランジスターをプログラムする段階と、で構成される。プログラムする段階は第1メモリセルトランジスターの閾値電圧が十分に変化されたかを第1検証電圧を利用して検証する段階を含む。判別する段階は第1メモリセルトランジスターの閾値電圧の第1範囲からの変化を判別する段階を含む。

(もっと読む)

不揮発性半導体記憶装置

【課題】閾値電圧分布の広がりを抑制した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリセル、ビット線、ワード線、及び制御回路を有する。メモリセルは、電気的にデータを書き換え可能に構成される。ビット線は、メモリセルの電流経路の一端に電気的に接続される。ワード線は、ビット線と交差する方向に配列されたメモリセルに共通に接続される。制御回路は、ワード線に書込電圧を印加してデータを書き込むべきメモリセルの閾値電圧を所定の閾値電圧以上になるまで移動させる書込動作を実行する。制御回路は、書込動作時に、ワード線に逐次上昇する書込電圧を印加しつつ、書き込むべきメモリセルの閾値電圧と書込電圧の印加回数との関係に基づいてビット線に印加する電圧を逐次変更する。

(もっと読む)

半導体記憶装置

【課題】消費電力を低減出来る半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、選択トランジスタ、メモリセル、ワード線、セレクトゲート線、ドライバ回路12、ロウデコーダ11−0、及び検知回路16を備える。ドライバ回路12は、第1電圧Vss,Vccを出力する。ロウデコーダ11−0内の第1転送トランジスタは、ワード線及びセレクトゲート線の各々に関連付けられ、ドライバ回路12から出力された第1電圧を、ワード線及びセレクトゲート線に転送する。検知回路16は、データの消去時において、ビット線及び/またはソース線に印加される第2電圧を検知して、検知結果に応じてフラグを生成する。ドライバ回路12は、フラグが生成されたことに応答して第1電圧の値を変更して、第1転送トランジスタをカットオフさせる。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体メモリの情報書き換え方法

【課題】不揮発性半導体メモリの書き換え時に、適切なパルス電圧および適切なパルス幅を備える信号を印加可能な不揮発性半導体記憶装置を提供することである。

【解決手段】本発明にかかる不揮発性半導体記憶装置は、記録されている情報を所定のパルス電圧および所定のパルス幅を備える信号を印加することで書き換え可能な不揮発性半導体メモリ11と、不揮発性半導体メモリ11の書き換えを制御する書き換え制御部12と、を備える。書き換え制御部12は、不揮発性半導体メモリの総書き換え回数に基づき仮のパルス電圧および仮のパルス幅の少なくとも一つを決定する。更に、決定された仮のパルス電圧および仮のパルス幅の少なくとも一つを不揮発性半導体メモリ11の温度に基づいて補正することで、書き換え時に不揮発性半導体メモリ11に印加する信号のパルス電圧およびパルス幅の少なくとも一つを決定する。

(もっと読む)

メモリ装置

【課題】、復号効率のよいメモリカード3を提供する。

【解決手段】メモリカード3は、複数のメモリセル13Dと、HB読み出し電圧とSB読み出し電圧とを、メモリセル13Dに印加する制御を行うCPUコア11と、閾値電圧をもとにLLRテーブルから取得したLLRに基づき軟判定復号を行うECC部1と、を具備し、第1のLLRテーブル20Aから取得したLLRに基づいた復号が失敗した場合に、最高電圧の第1のHB読み出し電圧H07を中心とする閾値電圧分布を測定し、閾値電圧分布の最小頻度電圧VMと第1のHB読み出し電圧H07との差である第1のシフト値ΔV1が「負」の場合には、第2のLLRテーブル20Bから取得したLLRに基づき復号を行い、第1のシフト値ΔV1が「正」の場合には、第3のLLRテーブル20Cから取得したLLRに基づき復号を行う。

(もっと読む)

高速OTP感知スキーム

【課題】不揮発性メモリアレイのための高速感知スキームを提供する。

【解決手段】メモリアレイは、ビット線をVSSなどの第1電圧レベルまで予備充電するための予備充電回路を備えた、相補形ビット線構成で配置された不揮発性メモリセルと、相補形ビット線対の基準ビット線に基準電荷を印加するための基準回路と、相補形ビット線対の間の電圧差を感知するためのビット線感知増幅器とを備えている。データビット線の電圧は、起動されたワード線に接続されたプログラム済みの不揮発性メモリセルがワード線電圧をデータビット線に結合すると変化する。

(もっと読む)

多数の外部電力供給部を有する不揮発性半導体メモリ

【課題】メモリ動作を可能にするために、低いまたはより低い電圧入力をより高い電圧に変換することは、変換器効率を低下させ、チャージポンプ回路のサイズおよび複雑さを増加させる。

【解決手段】メモリデバイスはデータを記憶するためのフラッシュメモリなどのコアメモリを含む。メモリデバイスは、フラッシュメモリに電力を供給するのに使用される第1の電圧を受け取るために第1の電力入力部を含む。さらに、メモリデバイスは、第2の電圧を受け取るために第2の電力入力部を含む。第2の電圧を受け取り、1つまたは複数の内部電圧を引き出すように構成された電力管理回路をメモリデバイスは含む。電力管理回路は内部電圧をフラッシュメモリに供給または伝達する。電力管理回路(例えば電圧変換器回路)によって発生され、コアメモリに供給される様々な内部電圧は、コアメモリ中のセルに関する読出し/プログラム/消去などの動作を可能にする。

(もっと読む)

不揮発性半導体記憶装置

【課題】多値書き込み時におけるメモリセルのしきい値分布の拡大を抑制する。

【解決手段】書き込み制御部7aは、レベルの高い第1のしきい値分布についての第1書き込み動作を行い、前記第1のしきい値分布の第1ベリファイ動作を行い、前記第1ベリファイ動作の結果に基づいて、第2書き込み動作を行い、前記第1のしきい値分布よりもレベルの低い第2のしきい値分布についての書き込み動作を開始する。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルのしきい値分布の拡大を抑制しつつ、書き込みの高速化を図る。

【解決手段】書き込み制御部7aは、メモリセルの低レベル領域と高レベル領域を検索する条件ベリファイ動作を行い、条件ベリファイ動作以降の書き込み動作において前記低レベル領域と前記高レベル領域の書き込み電圧を共通に設定するとともに、前記低レベル領域と前記高レベル領域のビット線電圧を別個に設定する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法とデータ書き換え方法

【課題】データ保持時間を、マスクROMと同様の無限大とすることができる、長期にわたりデータを保持できる信頼性の高いEEPROMを提供する。

【解決手段】不揮発性半導体記憶装置は、所定のセンスレベルに対して熱平衡状態しきい値電圧が正方向である第1の不揮発性半導体記憶素子100に正のデータを記憶し、熱平衡状態しきい値電圧が負方向である第2の不揮発性半導体記憶素子200に負のデータを記憶することでデータ保持時間を無限大にする。

(もっと読む)

1 - 20 / 1,667

[ Back to top ]