Fターム[5C080DD09]の内容

陰極線管以外の表示装置の制御 (251,852) | 目的、効果 (44,953) | 誤動作防止 (2,465)

Fターム[5C080DD09]の下位に属するFターム

クロストーク防止 (911)

Fターム[5C080DD09]に分類される特許

401 - 420 / 1,554

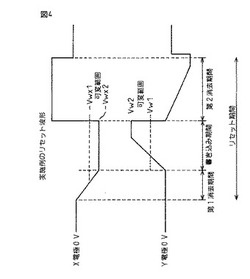

プラズマディスプレイ装置の駆動方法

【課題】隣接セルの電極が近くに存在するALIS方式のパネルでも、背景発光を低減し、暗室コントラストを更に向上したPDP装置の駆動方法の実現。

【解決手段】第1方向に伸びる第1電極Xと第2電極Yを隣接して交互に配置し、第2電極の両側で第1及び第2表示ラインを形成し、これらを交互に別々のフィールドで表示するインターレース表示を行うプラズマディスプレイ装置の駆動方法であって、1表示フィールドは複数のサブフィールドで構成され、各サブフィールドは、少なくともリセット期間、アドレス期間及び維持放電期間より構成され、リセット期間は、少なくとも書き込み放電工程と消去放電工程とを備え、書き込み放電工程の電圧を、少なくとも一部のサブフィールドで異ならせる。

(もっと読む)

液晶表示装置の駆動方法

【課題】解像度の低い画像を、解像度を高くして表示しつつ、消費電力を低減することを課題とする。

【解決手段】超解像処理を用いて、解像度を高くする。そして、超解像処理の後、ローカルディミングを用いて、バックライトの輝度を制御して、表示を行う。バックライトの輝度を制御することにより、消費電力を低減することが出来る。また、超解像処理の後で、ローカルディミングを用いることにより、正確に表示を行うことが可能となる。

(もっと読む)

電子機器及びシフトレジスタの制御方法

【課題】ゲートドライバのシフトレジスタの出力を安定化させる。

【解決手段】ゲートドライバ12は、n段のシフト回路が直列に接続されたシフトレジスタを備え、各シフト回路は出力信号OUT(1)〜OUT(n)を出力する。コントローラ14は、このゲートドライバ12に、スタート信号Start1、クロック信号ck1,ck2を供給し、また、出力信号OUT(n)を出力した直後から次の出力信号OUT(n−1)を出力する直前まで、Highレベルの出力信号OUT(n)の電位を変位させるend信号を供給する。この出力信号OUT(n)の電位が変位することにより、最終段のシフト回路の動作が安定し、後段から順次動作が是正され、予め設定された期間が経過したときは、すべての段のシフト回路が安定し、正常動作状態に落ち着く。

(もっと読む)

表示装置の駆動装置

【課題】本発明は画像信号の異常発生の時に生じるラッチアップ現象を防止する液晶表示装置の駆動装置に関する。

【解決手段】本発明のゲート駆動部は、一列に連結された複数のシフトレジスタを含み、各シフトレジスタは蓄電器と、バッファートランジスタ及びプルダウントランジスタを含む。プルダウントランジスタは、バッファートランジスタの入力端子に連結され、前段シフトレジスタの出力によりバッファートランジスタがターンオンされる場合、後段シフトレジスタの出力によりプルダウントランジスタがターンオンされて、前記第1電圧がバッファートランジスタを通じて蓄電器に充電できないようにすることによりラッチアップ現象を防止する。

(もっと読む)

プロジェクタ

【課題】光変調素子の短命化を回避しつつ、電源ボタン等の操作に関して誤解を与えることなく画像再表示までの時間を短縮化し得る表示装置を提供する。

【解決手段】光源ランプ2、光変調素子および制御部を備えて画像を投射表示可能に構成され、光源ランプ2および光変調素子の間に配設されて光源ランプ2からの光を調光する調光パネル5を備え、制御部は、消灯指示信号が出力されたときに(電源ボタンがオフ操作されたときに:ステップ22)調光パネル5を制御して光源ランプ2からの光を遮光させ(ステップ23)、その状態で所定時間が経過したときに(電源ボタンがオン操作されなかったときに:ステップ24)光源ランプ2を消灯させると共に(ステップ26)所定時間内に点灯指示信号が出力されたときに(ステップ24)調光パネル5を制御して光の遮光を解除させる(ステップ31)。

(もっと読む)

画像表示装置及び画像表示方法

【課題】表示画面の視認性を向上するとともに、誤操作の発生を確実に抑えること。

【解決手段】情報を表示する表示部11と、表示部の近傍を撮影するカメラ13と、カメラ13により撮影された画像情報を解析する顔解析部114、追跡処理部115と、解析結果に基づいて、表示部11に表示されている情報を拡大表示する拡大・縮小処理部117と、を備える。

(もっと読む)

アクティブマトリクス型ディスプレイ装置及びこれを備える電子機器

【課題】電圧検知素子の特性によらないメモリ回路内蔵画素を有するディスプレイ装置等を提供する。

【解決手段】各画素100は、表示素子Clcの電圧状態を記憶するキャパシタC11と、表示素子とキャパシタとの間に接続され、サンプリング期間中にオンするスイッチング素子Q12と、キャパシタとスイッチング素子との間に現れる電圧を検知する電圧検知回路Q13とを有する。ディスプレイ装置は、電圧検知回路Q13に接続されていない側のキャパシタC11の端子に接続され、サンプリング期間に、表示素子Clcの電圧状態の変動範囲内にある所定電圧をキャパシタへ印加する第1のキャパシタ電圧源20及び/又はスイッチング素子Q12に接続されていない側の表示素子Clcの端子に接続され、サンプリング期間に、表示素子の電圧状態の変動範囲内にある所定電圧を表示素子へ印加する第2のキャパシタ電圧源40を更に有する。

(もっと読む)

投射型表示装置、その制御方法、及びその制御プログラム

【課題】起動時間を短縮できる投射型表示装置を提供する。

【解決手段】投射型表示装置1は、光源ランプ211から射出された光束を変調して画像を形成し、画像を投射して投射画像Fを表示する。この投射型表示装置1は、当該投射型表示装置1を動作させるための制御プログラムを実行する主制御部41と、主制御部41に制御される動作デバイス43,44とを備える。主制御部41は、光源ランプ211を点灯起動させるランプ制御手段411と、ランプ制御手段411が、光源ランプ211を点灯起動させる際に発生する点灯ノイズの発生期間を判定する判定手段412と、判定手段412にて発生期間と判定した場合は、当該主制御部41内部で閉じた内部処理を実行する内部処理手段414と、発生期間を除いた他の期間は、動作デバイス43,44に制御信号を出力して外部処理を実行する外部処理手段413と、を備える。

(もっと読む)

表示装置およびその駆動方法

【課題】表示装置及びその駆動方法を提供する。

【解決手段】原映像信号及び入力制御信号を受信し、入力制御信号に応答して制御クロック信号を提供する受信部1100と、原映像信号に基づいて制御クロック信号に同期したデータ信号を提供する映像信号処理部1210と、データ信号を受信し、データ信号をサンプリングして生成されてデータクロック情報が埋め込まれたデータ情報を含む映像信号を提供する送信部1300からなる信号制御部1000を含む表示装置。

(もっと読む)

ヘッドマウントディスプレイ

【課題】表示された画像の表示状態の変更を眼の動作で正確に操作でき、誤動作を防止することが可能となるヘッドマウントディスプレイを提供する。

【解決手段】CPU51は、CCDセンサ18によって撮像された右眼6の撮像画像を画像認識することによって、右眼6の瞼6Aの動作を検出する。そして、CPU51は、右眼6の瞼6Aが閉じられている場合には、CCDセンサ16を介して検出された左眼5の眼球5Aの眼球運動に従って左眼5に表示されるコンテンツ(画像)の表示制御を行う。

(もっと読む)

液晶表示装置

【課題】製造コストを低減する。

【解決手段】液晶表示装置10はアレイ基板ARおよび対向基板CT間にOCB液晶を保持した液晶表示パネルDPと、液晶表示パネルDPを照明するバックライトBLと、液晶表示パネルDPおよびバックライトBLの駆動制御を行う駆動制御回路DRとを備える。駆動制御回路DRは内部電源電圧Voutを得るために電源電圧Vinを昇圧するDC/DCコンバータ5、液晶表示パネルDPに印加されて液晶分子の配向状態をスプレイ配向からベンド配向に転移させる転移電圧を内部電源電圧Voutから生成する転移回路3、バックライトBLに印加される光源駆動電圧を内部電源電圧Voutから生成するインバータ回路LD、並びに電源電圧Vinの投入に伴って内部電源電圧Voutを転移回路3に出力し、転移電圧による液晶表示パネルDPの初期化後に内部電源電圧Voutの出力先をインバータ回路LDに切換えるスイッチ6を含む。

(もっと読む)

液晶表示装置、および液晶表示装置を具備した電子機器

【課題】容量素子と接続されるトランジスタの数を減らすことを課題とする。

【解決手段】容量素子と、一つのトランジスタとを有し、容量素子の一方の電極は配線と接続され、容量素子の他方の電極はトランジスタのゲートと接続される構成とする。当該配線には、クロック信号が入力されるので、クロック信号は容量素子を介してトランジスタのゲートに入力される。そして、トランジスタの導通状態は、クロック信号に同期した信号によって制御され、トランジスタはオンになる期間とオフになる期間とを繰り返す。こうして、トランジスタの劣化を抑制することができる。

(もっと読む)

プロジェクタ装置およびその制御方法

【課題】主制御プロセッサのソフトウェア暴走で制御情報の誤りを発生させない。

【解決手段】プロジェクタ装置は、映像に対応した光源からの光を投射する投射部20と、制御情報を保持するEEPROM13と、様々な操作を行うユーザインタフェース11,12と、起動後に制御情報に基づいて投射部20を制御するメインCPU14と、ユーザインタフェース11,12の操作に従ってメインCPU14を起動または停止させる制御およびメインCPU14の動作の監視を行うサブCPU15とを備える。サブCPU15はメインCPU14のソフトウェア暴走を検出し、この検出時点までにメインCPU14の動作において生じた制御情報の変更をEEPROM13に保持される制御情報に反映させ、さらにメインCPU14を再起動する。

(もっと読む)

電気光学装置、電気光学装置の製造方法、電子機器

【課題】不揮発性メモリと画素TFTとを同一基板上に形成でき、且つ両者を良好に動作させることが可能な電気光学装置を提供する。

【解決手段】画素TFTのゲート絶縁膜18を不揮発性メモリのトンネル絶縁膜(第1の絶縁膜)35と、トンネル絶縁膜35よりも膜厚の大きい第2の絶縁膜37によって構成する。また、フローティングゲート電極36のコントロールゲート電極60側の面を凹凸とし、該凹凸によってフローティングゲート電極36の表面積を拡げる。これにより、フローティングゲート電極36とコントロールゲート電極60との間の容量を、フローティングゲート電極36と半導体層33との間の容量よりも大きくする。

(もっと読む)

マトリクス装置の駆動回路、マトリクス装置、画像表示装置、電気泳動表示装置、及び電子機器

【課題】瞬間的に大きな電力消費が発生するのを抑えることができ、安定して動作させることができるマトリクス装置の駆動回路を提供する。

【解決手段】データ線駆動回路62は、シフトレジスタ160と、シフトレジスタ160の出力端子及びデータ信号線と接続された第1のデータラッチ回路161と、第1のデータラッチ回路161の出力端子に接続されるとともに前記データ線と直接又は他の回路を介して接続された第2のデータラッチ回路162とを有し、第2のデータラッチ回路162は、一又は複数のデータ線68に対応するラッチ回路により構成される複数段のブロックLAT2に分割されており、ブロックLAT2ごとに異なるラッチ有効化信号を入力する複数のラッチ有効化配線166が設けられていることを特徴とする。

(もっと読む)

表示装置、電子機器および表示装置の駆動方法

【課題】従来よりも信頼性を向上させることが可能な表示装置を提供する。

【解決手段】ドレイン線DSLの電圧がVccとなっている発光期間中において、信号線DTLの電圧がVofsとなっている時に、ゲート線WSLの電圧がVoffからVonに上げられたのちにVonからVoffに下げられるオン期間を設ける。これにより、トランジスタTDrのVth変動が抑えられ、そのようなVth変動に起因したVgsの低下による発光電流値の低下が抑えられる。なお、そのようなオン期間後において信号線DTLの電圧がVofsとなっている時に、オン期間を再度設けると共に、その再度のオン期間時におけるドレイン線DSLの電圧をVccからVcc’へ変動させるようにするのが好ましい。

(もっと読む)

シフトレジスタ

【課題】シフトレジスタを提供する。

【解決手段】シフトレジスタの各段階はプルアップ回路、プルアップ制御回路、プルダウン回路とプルダウン制御回路を含む。プルアップ回路は、第1クロック信号CK1と第2クロック信号XCK1を受信するための入力端、出力信号Onを応答可能に出力するための出力端と入力節点Qnを有する。プルアップ制御回路は、入力節点Qnに電気的に接続され、第1入力信号を受信した時、応答可能に信号を発生し、プルアップ回路の入力節点Qnに提供し、プルアップ回路を始動する。プルダウン回路は、入力節点Qnに電気的に接続され、第1電圧を入力節点Qnとプルアップ回路の出力端のいずれかに提供する。プルダウン制御回路は、第3クロック信号CK2と第4クロック信号とのいずれかを受信し、応答可能に第1電圧を発生し、Sn段階のプルダウン制御回路とSn−1段階とSn+1段階とのいずれかのプルダウン回路を始動する。

(もっと読む)

映像表示装置およびその制御方法

【課題】映像表示装置において、制御手段に誤動作があった場合でも、誤って照明手段に電力が供給されることを確実に回避できるようにする。

【解決手段】CPU110が出力するバラスト制御信号は、ランプバラストユニット400には直接入力されず、AND回路153に入力される(監視結果C)。また、AND回路153には、NAND回路151から、第1および第2検出スイッチ201,202の検出結果に基づく、ミラーの状態の検出結果(監視結果A)が、そして、NAND回路152から、CPU110がリレーユニット300に出力する第1リレー301と第2リレー302の開閉制御用信号の内容(監視結果B)が、入力される。AND回路153は、入力される監視結果A〜監視結果Cの全てがリレーユニット300への電力供給に適切なものである場合にのみ、ランプバラストユニット400に対し当該電力供給を指示する。

(もっと読む)

シフトレジスタ回路

【課題】クロック信号の周波数が高くなった場合における駆動能力の低下を抑制可能なシフトレジスタ回路を提供する。

【解決手段】単位シフトレジスタSRは、クロック信号CLKを出力端子OUTに供給するトランジスタQ1およびそれを駆動するプルアップ駆動回路21と、出力端子OUTを放電するトランジスタQ2およびそれを駆動するプルダウン駆動回路22とを備える。プルアップ駆動回路21において、トランジスタQ1のゲートを充電するトランジスタQ3のゲートは、前段の出力信号Gk-1の活性化に応じて充電され、さらに容量素子C2によって昇圧される。その結果トランジスタQ3は非飽和領域で動作する。

(もっと読む)

集積回路装置、電気光学装置、及び電子機器

【課題】駆動時間を十分に確保した上で高精度な電圧を出力する。

【解決手段】複数の階調電圧を出力する階調電圧生成回路110とデータ電圧を供給するデータドライバ50のデータ線駆動回路54−1〜54−mに設けられる増幅回路は、入力ノードNI、第1のノードN1間に設けられる第1のスイッチ素子SW1と、第1のノードN1、サミングノードNEG間に設けられる第1のキャパシタC1と、第1のノードN1、アナログ基準電源AGND間に設けられる第2のスイッチ素子SW2と、第2のノードN2、サミングノードNEG間に設けられる第2のキャパシタC2と、第2のノードN2、出力ノードNQ間に設けられる第3のスイッチ素子SW3と、第2のノードN2、アナログ基準電源AGND間に設けられる第4のスイッチ素子SW4と、出力ノードNQ、サミングノードNEG間に設けられる第5のスイッチ素子SW5と、を含む。

(もっと読む)

401 - 420 / 1,554

[ Back to top ]