Fターム[5C094EA10]の内容

要素組合せによる可変情報用表示装置 (81,180) | 導電部材 (4,625) | その他の導電部材 (1,842)

Fターム[5C094EA10]に分類される特許

201 - 220 / 1,842

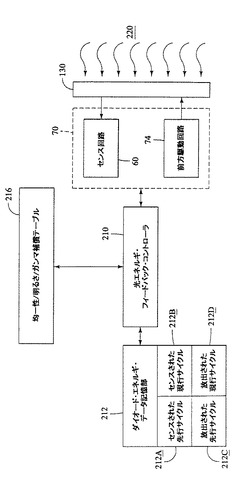

エネルギをセンスする発光ダイオード・ディスプレイ

【課題】ディスプレイ自体内部にエネルギ・センサを含むディスプレイを開示する。

【解決手段】有機発光ダイオード(OLED)は発光器とエネルギ検出器との両方として動作させ得る。適切な駆動信号によって前方バイアスされた場合、OLEDは電界発光によって光を放出し、ディスプレイ上で画像の一部分を構成するのに用い得る。別の態様では、OLEDは光電効果によって入射光子又はエネルギを電気信号に変換することによってエネルギを検出し得る。ディスプレイにおけるOLEDを放出モードとセンス・モードとの両方にて動作することによって、外部ソースからのような、ディスプレイ上に照射するエネルギを、画像が表示されるのと同時に検出し得る。更に、OLEDを含むディスプレイはディスプレイ自体によって生成された光エネルギを検出し得る。

(もっと読む)

発光装置および電子機器

【課題】発光装置の各部に寄生する容量の影響を低減する。

【解決手段】単位素子Pは、第1電極21と第2電極22との間に発光層23が介在する発光素子Eと、発光素子Eに供給される電流量を制御する駆動トランジスタTdrと、駆動トランジスタTdrのゲート電極に電気的に接続された容量素子C1と、駆動トランジスタTdrのゲート電極の電位をデータ信号に応じて設定するための選択トランジスタTslと、駆動トランジスタTdrのゲート電極とドレイン電極との接続を制御するための初期化トランジスタTintとを含む。第1電極21は、容量素子C1と重なり合う一方、選択トランジスタTslや初期化トランジスタTintとは重なり合わない。

(もっと読む)

表示装置

【課題】複数の画素に電源を供給する電源線による開口率の減少を最小化し、電源線の電圧降下によるクロストークの発生を低減できる表示装置を提供する。

【解決手段】複数の画素が行列状に配列される画素領域を含む表示装置は、前記画素領域の一側及び前記一側に対向する他側に設けられる複数の主電源線、前記画素領域の一側に設けられる第1主電源線に接続して、前記画素領域に延長される複数の第1副電源線、及び前記画素領域の他側に設けられる第2主電源線に接続して、前記画素領域に延長される複数の第2副電源線を含み、前記複数の第1副電源線及び前記複数の第2副電源線は、互いに異なる画素列に沿って延長され、一つの画素列に含まれる複数の画素は、隣接した第1副電源線及び隣接した第2副電源線に交互に接続される。

(もっと読む)

電気装置

【課題】封止材料を均一に加熱溶融することが可能な構成の電気装置を提供する。

【解決手段】支持基板と、前記支持基板上に設定される封止領域内に設けられる電気回路と、前記支持基板上において、前記封止領域内から封止領域外に延在して設けられ、外部の電気信号入出力源と前記電気回路とを電気的に接続する電気配線と、前記封止領域を取囲んで前記支持基板上に設けられる封止部材と、前記封止部材を介して、前記支持基板に貼合される封止基板とを有する電気装置であって、前記電気回路は、有機層を有する電子素子を備え、平面視において前記電気配線と前記封止部材とが交差する交差領域では、前記電気配線が透光性電気配線によって構成されている、電気装置。

(もっと読む)

表示装置の作製方法

【課題】鮮明な多階調カラー表示の可能なEL表示装置及びそれを具備する電気器具を提供する。

【解決手段】画素104に設けられたEL素子109の発光、非発光を時間で制御する時分割駆動方式により階調表示を行い、電流制御用TFT108の特性バラツキによる影響を防ぐ。また、時分割駆動方式を用いる際、データ信号側駆動回路102及びゲート信号側駆動回路103を、特異な結晶構造を有するシリコン膜を用いた極めて動作速度の速いTFTで形成する。

(もっと読む)

発光装置および電子機器

【課題】データ信号を伝送する信号線の寄生容量を低減する。

【解決手段】発光装置100は、複数の発光素子Pを含む有効領域Aと、各発光素子Pに供給されるデータ信号を伝送する複数の信号バス配線30と、信号バス配線30から分岐して各発光素子Pにデータ信号を供給するための信号供給線301と、各発光素子Pに電源電圧を供給するための電源配線20とを有する。信号バス配線30は有効領域Aの一辺と同じ方向に配設される。電源配線20は主電源配線20Aと副電源配線20Bとを有し、主電源配線20Aは信号供給線301を挟んで有効領域Aの反対側に配設される。これにより、信号供給線301と主電源配線20Aとは交差しない。

(もっと読む)

液晶表示装置

【課題】 表示品位の良好な液晶表示装置を提供する。

【解決手段】 各画素PXに配置された画素電極EPと、半導体層12の一部を含み画素電極EPへの映像信号Vsの書き込みを切替えるスイッチWと、半導体層12と対向して補助容量Csを形成する補助容量線CsLと、を備えた第1基板ARと、アクティブエリアDSPから遮光エリアSLDの少なくとも一部のエリアにわたって延在する対向電極ETと、を備えた第2基板CTと、第1基板ARと第2基板CTとの間に保持された液晶層LQと、を備え、アクティブエリアDSPの両端部に配置された端部画素PX(E)の画素電極EPは、他の画素電極EPよりも大きくなるようにアクティブエリアDSPから遮光エリアSLD側へ延びて配置され、前記端部画素において形成される前記補助容量は他の前記画素において形成される前記補助容量よりも大きい液晶表示装置。

(もっと読む)

半導体装置及びトランジスタの駆動方法

【課題】光照射されてトランジスタの電気特性が変動した場合でも、その電気特性をほぼ光照射前の状態にする手法を提供する。

【解決手段】酸化物半導体を用いたトランジスタのゲート電極に、正のバイアス電圧を10msec以上印加することにより、光照射されて変動した当該トランジスタの電気特性をほぼ光照射前の状態にすることが可能になる。なお、当該トランジスタのゲート電極に対する正のバイアス電圧印加は、当該トランジスタが受光する光量を参照して適切なタイミングで行う。これより光照射されても表示品位の低下が抑制された表示装置を実現することができる。

(もっと読む)

薄膜トランジスタ表示板、これを含む表示装置及び液晶表示装置の製造方法

【課題】光硬化性結合部材を用いた共通電極表示板との結合が容易である薄膜トランジスタ表示板を提供する。

【解決手段】ゲート線、データ線、画素電極及び薄膜トランジスタが設けられている基板、及び前記基板上に設けられ、外部からの信号を受信する配線部と前記配線部からの信号に応答してゲート信号を前記ゲート線に出力する回路部とを備えるゲート駆動部、を含み、前記配線部は、前記配線部に重畳する光硬化性の結合部材に光を透過させるための開口部が設けられている信号線を含み、前記配線部は開口部が設けられていない信号線をさらに含む。

(もっと読む)

薄膜トランジスタおよび表示装置用電極基板の製造方法

【課題】ボトムコンタクト構造で、かつセルフアラインのTAOS TFTにおいて、TAOS層のソース領域およびドレイン領域に相当する領域を十分に低抵抗化できる製造方法、およびこのTAOS TFTを用いた表示装置用電極基板の製造方法を得る。

【解決手段】ゲート電極12、ソース電極14およびドレイン電極15上に、ゲート電極12を跨いでソース電極14とドレイン電極15とを繋ぐように第1、第2TAOS層16、17を形成するステップと、第1、第2TAOS層16、17上に、ゲート電極12をマスクとしたガラス基板11側からの露光により島状絶縁膜18を形成するステップと、ガラス基板11の全面に、島状絶縁膜18をマスクとして、島状絶縁膜18側からプラズマを照射するステップと、島状絶縁膜18の周囲に露出した第1、第2TAOS層16、17をアルカリ溶液に浸すステップとを備える。

(もっと読む)

情報表示システム、情報表示器、駆動装置

【課題】薄型でコンパクトな駆動装置と、薄型の情報表示器を用いて情報を表示できる情報表示システムを提供する。

【解決手段】 情報表示器1Aは、第1基板11及び第2基板12の間において電界で駆動する表示媒体を備え、画素電極34が配置されたTFT基板31を備える駆動装置30を用いて第1基板11と画素電極34との間に形成させた電界によって、表示媒体が駆動されて情報表示画面領域に情報を表示するように構成されており、情報表示システムは、第1基板11側の外側に、弾性変形する弾性体層61が配置される。

(もっと読む)

電気光学装置及び電子機器

【課題】液晶装置等の電気光学装置において、例えばウェット処理工程における電蝕の発生を防止する。

【解決手段】電気光学装置は、基板(10)と、基板上の画素領域(10a)に設けられた走査線(11)及びデータ線(6)と、走査線及びデータ線よりも上層側に、走査線とデータ線との交差に対応して設けられ、透明導電材料からなる画素電極(9)と、画素電極と、前記走査線及び前記データ線との間の層に、画素電極に容量絶縁膜(72)を介して対向するように設けられた蓄積容量電極(71)と、画素電極と同一層からなる第1容量電極(610)と、蓄積容量電極と同一層からなり、データ線と電気的に接続された第2容量電極(620)とを有し、画素領域の外周と基板の外周の間の領域に設けられた付加容量(600)と、前記領域に設けられるとともに第1容量電極と電気的に接続されており、画素電極と同一層からなる端子(106)とを備える。

(もっと読む)

半導体装置

【課題】薄膜トランジスタの電流駆動能力を増大するとともに負荷である配線容量を低減することが可能な半導体装置を提供する。

【解決手段】 絶縁基板と、前記絶縁基板上に形成されたゲート電極及び第1信号配線と、前記ゲート電極及び前記第1信号配線を覆う第1絶縁膜と、前記ゲート電極の直上の位置を含む前記第1絶縁膜上に形成された酸化物半導体層と、前記酸化物半導体層の一部を覆うとともにその領域を挟んだ両側で前記酸化物半導体層を露出し、且つ、前記第1信号配線の直上の位置を含む前記第1絶縁膜上に形成された第2絶縁膜と、前記第2絶縁膜から露出した前記酸化物半導体層にそれぞれ電気的に接続されたソース電極及びドレイン電極と、前記第2絶縁膜上に形成されるとともに前記第1信号配線と交差する第2信号配線と、を備えたことを特徴とする半導体装置。

(もっと読む)

発光装置

【課題】複雑な構造とすることなく、従来よりも密閉性に優れた空間に発光素子を備え、

かつ作業性に優れた封止技術を提供することにより、発光素子の劣化を防ぎ、信頼性の向

上を図ることを目的とする.

【解決手段】本発明では、密閉性に優れた封止構造を形成するために二重構造の封止を行

う。なお、この場合において、素子が形成される素子基板(以下、第1の基板ともいう)

と、封止に用いる封止基板(以下、第2の基板ともいう)にそれぞれサイズの異なる基板

を用いて、両基板が重ならない領域(以下、オフセット領域という)を設けることにより

、二重構造における外側のシールパターンを形成する場合における作業性を良くすること

を特徴とする。

(もっと読む)

表示装置

【課題】 指先等の接触位置の検出感度を向上させ、動作正確性の高い表示装置を提供する。

【解決手段】 マトリクス状に配置された表示画素PXを含む表示部DYPと、表示画素PXに配置された画素電極PEと、画素電極PEが配列する行に沿って延びる走査線GLおよびセンサ用電極CsLと、画素電極PEが配列する列に沿って延びる信号線SLと、アレイ基板10と、複数の画素電極PEと対向するように配置された対向電極CEを備えた対向基板20と、センサ用電極CsLおよび信号線SLを駆動する駆動回路XD、YDと、駆動回路XD、YDへセンサ用信号を出力するとともに、センサ用電極CsLおよび信号線SLからの信号を受信してセンサデータを出力するセンサ用回路30と、を備え、表示部DYPの周囲の領域において、信号線SLが延びる方向に並ぶ複数のセンサ用電極が電気的に接続されている表示装置。

(もっと読む)

表示装置

【課題】簡易な構成で配線間の静電破壊を防ぐこと。

【解決手段】表示装置は、絶縁基板と、前記絶縁基板の上に第1の信号線と第2の信号線とが形成された第1の導電層と、前記第1の導電層の上層に設けられた絶縁層と、前記絶縁層の上層に設けられ、前記第1の信号線および第2の信号線と平面的に重なる半導体膜が形成された半導体層と、を含む。

(もっと読む)

表示装置用金属配線膜

【課題】Si半導体層および/または透明導電膜との間のバリアメタル層を省略しても、低抵抗のオーミック特性を有する電気的接触を確保でき、更に十分な耐熱性を有する表示装置用金属配線膜を提供する。

【解決手段】Moを20原子%以上含有しており、且つ、Si、Nd、Ni、Mn、Mg、Fe、及びZnよりなる群から選択される少なくとも一種を5原子%以上含有しているAl合金膜53と、純CuまたはCu合金膜28,29とからなる積層膜であって、前記Al合金膜が、半導体層33と直接接続していると共に、前記CuまたはCu合金膜が透明導電膜55と直接接続している表示装置用金属配線膜。

(もっと読む)

半導体装置、発光装置、モジュール、及び電子機器

【課題】電気光学装置において、新規の構成を有する画素回路を用いることにより、従来の構成の画素よりも高い開口率を実現することを目的とする。

【解決手段】i行目を除くゲート信号線の電位は、i行目のゲート信号線106が選択されている以外の期間においては定電位となっていることを利用し、i−1行目のゲート信号線111をi行目のゲート信号線106によって制御されるEL素子103への電流供給線として兼用することで配線数を減らし、高開口率を実現する。

(もっと読む)

薄膜トランジスタ回路基板及びその製造方法

【課題】製造コストの削減が可能な薄膜トランジスタ回路基板及びその製造方法を提供する。

【解決手段】 チャネル領域、前記チャネル領域を挟んだ両側にソース領域及びドレイン領域を有する酸化物半導体薄膜と、前記酸化物半導体薄膜と同一材料によって形成され、第1低抵抗部及び第2低抵抗部を有する第1容量形成部と、前記酸化物半導体薄膜の前記チャネル領域上及び前記第1容量形成部の前記第1低抵抗部上に形成されるとともに、前記酸化物半導体薄膜の前記ソース領域及び前記ドレイン領域及び前記第1容量形成部の前記第2低抵抗部を露出するゲート絶縁膜と、を備え、前記酸化物半導体薄膜のうち、前記ソース領域と前記ドレイン領域との間の前記チャネル領域の長さL1は、前記第1容量形成部のうち、前記ゲート絶縁膜が積層された端部から前記第2低抵抗部に至るまでの長さL2よりも短い。

(もっと読む)

半導体装置

【課題】画素部に形成される画素電極やゲート配線及びソース配線の配置を適したものとして、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表示装置を提供することを目的とする。

【解決手段】絶縁表面上のゲート電極及びソース配線と、前記ゲート電極及びソース配線上の第1の絶縁層と、前記第1の絶縁膜上の半導体層と、前記半導体膜上の第2の絶縁層と、前記第2の絶縁層上の前記ゲート電極と接続するゲート配線と、前記ソース電極と前記半導体層とを接続する接続電極と、前記半導体層と接続する画素電極とを有することを特徴としている。

(もっと読む)

201 - 220 / 1,842

[ Back to top ]