Fターム[5E082DD11]の内容

固定コンデンサ及びコンデンサ製造装置 (37,594) | コンデンサを含む複合部品 (479) | IC、LSIを含むもの (68)

Fターム[5E082DD11]に分類される特許

1 - 20 / 68

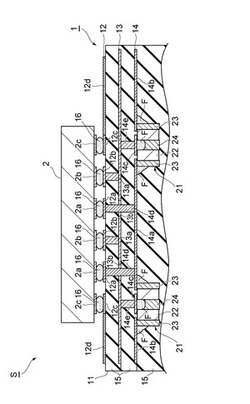

貫通コンデンサ内蔵多層基板及び貫通コンデンサ内蔵多層基板の実装構造

【課題】貫通コンデンサの接続不良の発生を低減できる貫通コンデンサ内蔵多層基板及び貫通コンデンサ内蔵多層基板の実装構造を提供する。

【解決手段】貫通コンデンサ内蔵多層基板1では、基板11の内部に貫通コンデンサ21を配置することにより、ノイズ成分を貫通コンデンサ21の接地用端子電極24から接地導体層13に流して除去することができる。また、貫通コンデンサ内蔵多層基板1では、貫通コンデンサ21の接地用端子電極24に接続される接地プレーン14cが、貫通コンデンサ21の信号用端子電極23に接続される電源プレーン14a及び電源用配線14bと同一段の導体層として配置されている。これにより、貫通コンデンサ21と電源導体層14及び接地導体層13との接続が同一段で実現されるので、貫通コンデンサ21の寸法に多少のばらつきが生じたとしても接続不良の発生を低減できる。

(もっと読む)

キャパシタ内蔵光電気混載パッケージ

【課題】電源電圧の安定化を図り、高速の信号伝達が可能なキャパシタ内蔵光電気混載パッケージを提供すること。

【解決手段】キャパシタ内蔵光電気混載パッケージ1において、コア基板13の収容穴部90にセラミックキャパシタ101が収容されている。コア基板13のコア主面14側に、樹脂層間絶縁層33,35,37及び導体層42を交互に積層してなる第1ビルドアップ層31が形成されている。第1ビルドアップ層31上において、CPU21とドライバIC23とが配線パターン58を介して接続される。CPU21は、第1電源安定用配線経路78を介してセラミックキャパシタ101に接続される。ドライバIC23は、第2電源安定用配線経路79を介してセラミックキャパシタ101に接続される。

(もっと読む)

容量素子及びその製造方法並びに半導体集積回路

【課題】高い周波数帯での導体損失の増加を抑え、幅広い周波数範囲で低損失な動作を実現することが可能な容量素子及びその製造方法並びに半導体集積回路を提供すること。

【解決手段】本発明の容量素子10は、第1電極11と、第1電極11上に設けられた誘電体層12と、誘電体層12上に設けられた第2電極13とから構成されている。容量素子10は、誘電体層12を第1電極11と第2電極13とにより挟むようにしたサンドイッチ構造になっており、第2電極13の外表面に凹凸が設けられている。

(もっと読む)

半導体装置およびバイパスキャパシタモジュール

【課題】バイパスキャパシタは、半導体基板上に形成される半導体装置と一体化されて形成されているが、半導体装置の製造工程が複雑になると言う欠点がある。

【解決手段】バイパスキャパシタをシート状にモジュール化して、半導体装置に対して外付けできるように構成されたバイパスキャパシタモジュールが得られる。

(もっと読む)

配線基板内蔵用コンデンサ及び配線基板

【課題】配線基板における樹脂材との密着性を確保するとともに、樹脂材でのクラックの発生を確実に防止することができる配線基板内蔵用コンデンサを提供すること。

【解決手段】セラミックコンデンサ101のコンデンサ本体104における側面106a〜106cには、セラミック誘電体層105を構成するセラミックが露出するとともに、コンデンサ本体104の厚さ方向に延びる凹部107が複数形成されている。コンデンサ本体104の側面106a〜106cにおける凹部未形成部109と凹部107との境界部分が丸みを帯びた形状を呈している。

(もっと読む)

電子複合部品

【課題】 本発明は、電源回路のDC−DCコンバータなどを構成することが可能で、かつ、小型でワンパッケージの電子複合部品を提供すること。

【解決手段】 インダクタ素子1および半導体素子2を実装した第二のプリント基板5と、2つの固体電解コンデンサ素子3を実装した第一のプリント基板7を接続して、ワンパッケージに樹脂モールドしたことを特徴とする電子複合部品。

(もっと読む)

DRAMセル

【課題】DRAMセルの密度を向上させ、製造工程を簡素化し、リフレッシュレートを下げることができるDRAMセルを提供する。

【解決手段】DRAMセルは、半導体材料からなり、主表面102を有する基板100と、主表面102に形成されたトランジスタ120と、トランジスタ120の上方に設けた金属層に形成した磁器コンデンサ140とを備える。磁器コンデンサ140は、第1の磁性層142と、第1の磁性層142上に形成した誘電体層144と、誘電体層144上に形成した第2の磁性層146とを有する。誘電体層144が非導電性材料からなり、第1の磁性層142及び第2の磁性層146がCoNiFe合金からなる。

(もっと読む)

チップ部品実装配線基板

【課題】表面実装されたチップ部品を実装用基板に接続する際にその接続を確実に行うことができるチップ部品実装配線基板を提供すること。

【解決手段】配線基板10は、実装用基板に実装されて用いられ、該実装用基板に対向する側の面にチップ部品20が実装されている。このチップ部品20は、その部品本体25の両端部にそれぞれ端子電極21を備え、各端子電極21は、その表面に形成されためっき膜(Sn)が配線基板10側と実装用基板側とに二分される形態で設けられている。一形態において、チップ部品20の各端子電極21は、配線基板10側と実装用基板側とに分割され、その分割された各々の端子電極21a,21bの表面にめっき膜(Sn)が形成されている。

(もっと読む)

エネルギ蓄積装置として用いる磁器コンデンサを有する電源を備える電気デバイス

【課題】従来技術の問題点を解決するとともに、エネルギ輸送コストが低く、電池を代替することができる電気デバイスを提供する。

【解決手段】電気デバイスは、正端子および負端子を有し、エネルギ管理機能を備えた集積回路チップ401と、集積回路チップ401に接続され、電力を蓄積し、集積回路チップ401へ電力を供給する磁器コンデンサ100とを備える。磁器コンデンサ100は、正端子に接続された第1の磁器セクションと、負端子に接続された第2の磁器セクションと、第1の磁器セクションと第2の磁器セクションとの間に配置された誘電体セクションとを有する。誘電体セクションは、電力を蓄積するために用いる。

(もっと読む)

交差部のアレイを有する集積キャパシタ

集積回路(「IC」)のキャパシタ(100)は、ICの層に形成され、キャパシタの第1のノードに電気的に接続され、かつ第1のノードの一部分を形成する第1の複数の導電性交差部(102,104)と、ICの金属層に形成された第2の複数の導電性交差部(108,110)とを有する。第2の複数の導電性交差部の導電性交差部は、キャパシタの第2のノードに電気的に接続され、かつ第2のノードの一部分を形成し、第1のノードに容量結合する。  (もっと読む)

(もっと読む)

電池

【課題】コンデンサの数を削減することができる電池を提供する。

【解決手段】発電要素111と、前記発電要素に接続され、前記発電要素を外部と電気的に接続する電極112と、前記発電要素を内包する外装部材114,115と、を備える電池11において、前記外装部材は、前記発電要素を内包する絶縁層1142と、前記絶縁層に接する導電層1141とを有し、前記導電層は、外部と電気的に接続する接続部1144を有する。

(もっと読む)

積層型半導体パッケージおよびそれに用いられるコンデンサ、並びに積層型半導体装置

【課題】 実装面積を大きくすることなく、電源バウンスを減少させ、安定した信号品質を供給する積層型半導体パッケージを提供する。

【解決手段】 積層型半導体パッケージは、第1半導体パッケージと、該第1半導体パッケージに積層された第2半導体パッケージと、第1半導体パッケージと前記第2半導体パッケージとの間に設けられ、第1半導体パッケージおよび前記第2半導体パッケージに接続されるコンデンサとを有する。

(もっと読む)

コンデンサ

【課題】コンデンサのケースの内部に充填される樹脂の量を低減する。

【解決手段】ケース12の底面28に交差するケース12の一側面に、ケース12の開口30が形成されている。コンデンサ10の製造過程において、この開口30からケース12内に樹脂20が注入されモールドされる。開口30が形成されるケース12の一側面の面積は、ケース12の上部の面及び底面28の面積より小さい。このため、従来のようにケースの上部に形成された開口より注入される樹脂量に比べ、ケース12の一側面である開口30より注入される樹脂量のほうが少なくすることができる。

(もっと読む)

ICパッケージの実装構造、その製造方法およびそのためのシートキャパシタ

【課題】汎用のプリント基板やICパッケージを用いた場合であっても、高周波ノイズの軽減やICの高速動作の安定化といったバイパスコンデンサの作用を充分に発揮させることができるICパッケージの実装構造を提供すること。

【解決手段】ICチップがパッケージされてなるICパッケージと、該ICパッケージが実装されているプリント基板と、ICチップとプリント基板とを電気的に接続するリードと、シートキャパシタとを備え、シートキャパシタはICパッケージの外側表面に配置され、シートキャパシタの電極端子は上記リードまたはICチップの接続端子と電気的に接続されている、ICパッケージの実装構造。

(もっと読む)

キャパシタ部品およびその製造方法ならびに半導体パッケージ

【課題】薄型に形成され、大きな電気容量を得ることができて配線基板に内蔵するキャパシタとして好適に使用できるキャパシタ部品およびこのキャパシタ部品を搭載した半導体パッケージを提供する。

【解決手段】平板状に形成された上部電極18および下部電極20と、前記上部電極18と下部電極20とによって挟まれて配置された誘電体層14と、前記上部電極18および下部電極20の少なくとも一方の外面を被覆する絶縁樹脂からなる被覆部24とを備える。前記上部電極18と下部電極20の少なくとも一方に、基板にキャパシタ部品を内蔵する際に、配線パターンに接続して形成されるビアよりも大径に形成された開口穴18b、20bが、少なくとも一つ設けられている。

(もっと読む)

キャパシタ内蔵プリント配線板

【課題】 従来のプリント配線板内蔵キャパシタの幾つかの問題を解決し得る新規なキャパシタ内蔵プリント配線板を提供すること

【解決手段】 キャパシタ内蔵プリント配線板であって、該キャパシタは、誘電体と、前記誘電体に比較して、相対的に小さい面積の一方の電極と、前記誘電体に比較して、相対的に大きい面積の他方の電極とを備えている。

(もっと読む)

ビアアレイ型積層セラミックコンデンサ及びその製造方法、コンデンサ内蔵配線基板

【課題】高容量化、高信頼化、低インダクタンス化、低電気抵抗化を達成でき、デカップリング用途に好適なビアアレイ型積層セラミックコンデンサの提供。

【解決手段】本発明のビアアレイ型積層セラミックコンデンサ10は、コンデンサ本体104、複数のビア導体131,132、複数の内層電極141,142、複数の外部電極111,112等を備える。コンデンサ本体104は、チタン酸バリウムを主成分とする誘電体105を介してニッケルを主体とする複数の内層電極141,142が積層配置されてなる。複数のビア導体131,132は、銅以外の金属であって銅よりも融点が高い金属を主体とするフィラーと銅との混合相からなる。複数の外部電極111,112は、複数のビア導体131,132における主面102側の端部に接続するように配置される。複数のビア導体131,132は全体としてアレイ状に配置される。

(もっと読む)

セラミック部品の製造方法

【課題】セラミック部品の外部電極上に突起状の導体を位置ズレがなく正確に形成することができるセラミック部品の製造方法を提供する。

【解決手段】フィルム設置工程において、感光性を有する厚さ200μmのフォトレジストフィルムをセラミック焼結体104上に設ける。直接露光工程において、直描露光機を用いてレーザ光を走査しながら照射してフォトレジストフィルムの露光を行う。現像工程において、露光されたフォトレジストフィルムを現像して、プレーン状電極111,112,121,122を露出させる開口部を有しためっきレジストを形成する。導体形成工程において、開口部を介して露出するプレーン状電極111,112,121,122に対してめっきを施すことにより、突起状導体50を形成する。

(もっと読む)

可変キャパシタ

【課題】 簡易な構造でかつ簡易な制御により静電容量を制御することが可能な可変キャパシタを得る。

【解決手段】 固定キャパシタC1〜C5は基板3上に実装され、並列に接続されている。FET1〜FET4は、2つの固定キャパシタの間に配置されている。固定キャパシタC1〜C5の各々の一方の電極は、FET1〜FET4の各々のゲート端子と接続されている。固定キャパシタC1の他方の電極は各FETのソース端子またはドレイン端子と接続されている。一対の引出端子2a、2bのうち一方の引出端子2aは固定キャパシタC1の一方の電極に接続され、他方の引出端子2bは固定キャパシタC1の他方の電極に接続されている。

(もっと読む)

混成集積回路装置

【課題】 セラミックコンデンサに駆動パルスが加えられると振動することを利用して音を発生させる。

【解決手段】 絶縁処理した金属基板5上の導電路6に駆動パルスにて駆動されるスイッチングトランジスタQ1、Q2と該スイッチングトランジスタに接続されるセラミックセラミックコンデンサCとを組み込んだ混成集積回路装置において、セラミックコンデンサは高歪率セラミックコンデンサで構成し、セラミックコンデンサを硬質性樹脂7で覆い、スイッチングトランジスタがスイッチングする度にセラミックコンデンサが振動する振動にて硬質性樹脂と金属基板を共鳴させ音声を発生させる。

(もっと読む)

1 - 20 / 68

[ Back to top ]