Fターム[5E336AA11]の内容

プリント板への電気部品等の実装構造 (16,219) | 電気部品等の実装構造 (3,097) | 複数部品の実装 (532)

Fターム[5E336AA11]の下位に属するFターム

部品間の配置関係を特定したもの (404)

Fターム[5E336AA11]に分類される特許

61 - 80 / 128

遅延回路および遅延時間調整方法

【課題】実装基板や半導体パッケージなどの配線基板の各配線の信号伝播の遅延時間を容易に調整および変更することができ、なおかつ配線基板の小型化および高密度実装にも対応可能な遅延回路および遅延時間調整方法を実現する。

【解決手段】遅延回路1は、遅延時間の設定を指示するインタフェース11と、任意の遅延時間にプログラム可能な遅延素子12と、を備え、遅延素子12の遅延時間が、インタフェース11から指示により設定される。

(もっと読む)

回路板

【課題】高抗張力銅箔を用いてデバイスホール内に長いフライングリードを有し、複数のデバイスホールを有する配線板にそれぞれ電子部品が安定に実装された回路板を提供する。

【解決手段】絶縁フィルム10からなる一のキャリアに形成された複数のデバイスホール12に電子部品20が実装された回路板において、該配線15が、常態における引張り強さが70kgf/mm2以上の高抗張力銅箔から形成され、該配線15の端部がデバイスホール縁に片持ち状態で複数延設されてインナーリードを形成しており、該デバイスホール12内に延設されたインナーリードの延設長さ(L)が、該インナーリードの線幅(W)に対して、40以上(L/W)であり、電子部品20がデバイスホール12内に収納されてインナーリードと電気的に接続されている。

(もっと読む)

部品内蔵モジュール及びその製造方法

【課題】接続部分の品質がより良好な部品内蔵モジュールを提供すること。

【解決手段】無機フィラ及び熱硬化性樹脂を含む混合物によって形成され、半導体素子12及びチップ部品13が内蔵された内蔵層11と、内蔵層11の少なくとも一方の面に設けられた回路基板15とを備え、内蔵層11は導電性樹脂161を有するインナービア16を有し、内蔵層11の25℃における熱膨張係数は、回路基板15の25℃における熱膨張係数以下である、部品内蔵モジュールである。

(もっと読む)

部品内蔵多層配線板

【課題】複数の電子部品が実装された回路板を多数積層して安定な部品内蔵多層配線板を得ることができるようにする。

【解決手段】配線板のデバイスホールに電子部品が実装された部品内蔵多層配線板において、配線は引張り強さが70kgf/mm以上の高抗張力銅箔から形成され、配線端部がデバイスホール縁に片持ち状態で複数延設されてインナーリードを形成し、該デバイスホール内に延設されたインナーリードの延設長さ(L)が、インナーリードの線幅(W)に対して、40以上(L/W)であり、電子部品がデバイスホール内に収納されてインナーリードと電気的に接続され、かつ積層された各回路板の絶縁フィルムの表面に形成された配線が、絶縁フィルムを貫通する貫通配線により絶縁フィルムの裏面側に積層される配線板に形成された配線回路に電気的に接続している。

(もっと読む)

発光装置、表示装置

【課題】対象物に対する取り付けが容易な発光装置等を提供する。

【解決手段】発光モジュール12は、ガラス布基材エポキシ樹脂をベースとする配線基板20、配線基板20の表面20aに実装される複数のLEDチップ21、各LEDチップ21を覆うレンズ30、レンズ30同士を連結する連結部31を備える。レンズ30および連結部31は一体成形されたシリコーン樹脂からなり、レンズ30および連結部31の形成部位以外には、配線基板20の表面20aが露出する。これにより、配線基板20の表面20aの全面をシリコーン樹脂で覆う場合と比較して、シリコーン樹脂によって配線基板20に与えられる収縮力を低減することができ、その結果、発光モジュール12に生じる反りを抑制することができる。したがって、ネジによるバックライトフレームへの発光モジュール12の取り付けを、容易に行うことが可能になる。

(もっと読む)

部品内蔵実装基板

【課題】高速・高密度電子機器で特に信号品質の確保が必要なCPU−メモリ間のアドレス線において、小型化と高周波特性確保の両立が実現できる部品内蔵実装基板を提供する。

【解決手段】絶縁基板100の表面上に、CPU101と、チップ部品としての並列終端抵抗105と、メモリ102とが搭載されている。絶縁基板100の内部には、CPU101の直下に第1のデカップリングキャパシタ106aが内蔵され、メモリ102の直下に第2のデカップリングキャパシタ106bが内蔵されている。並列終端抵抗105の直下には、膜部品としての直列終端抵抗103b及び信号品質補償用キャパシタ104bがその面を絶縁基板100の表面に平行にして内蔵されており、両者間に第3のデカップリングキャパシタ106cが内蔵されている。

(もっと読む)

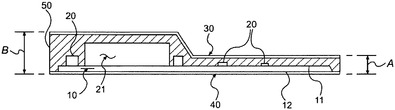

ステップカードおよびステップカードの製造方法

電子カードおよび同電子カードを製造する方法であって、電子カードは、上面および下面を有するプリント回路板、電子カードの第一の部分に配置された回路コンポーネントが電子カードの第二の部分に配置された回路コンポーネントよりも高さが大きい、プリント回路板の上面に取り付けられた複数の回路コンポーネント、プリント回路板の下面に取り付けられた下オーバーレイ、プリント回路板の上面の上方に配置された上オーバーレイおよびプリント回路板の上面と上オーバーレイとの間に配置されたコア層で構成され、電子カードの第一の部分が電子カードの第二の部分よりも大きな厚さを有する。

(もっと読む)

(もっと読む)

部品内蔵基板と、これを用いた電子機器、ならびにこれらに用いる製造方法

【課題】高さの低い電子機器の実現を目的とするものである。

【解決手段】本発明は、樹脂基材入り樹脂層21から流れだした樹脂分で電子部品6を埋設させる工程において、電子部品3が装着される部品搭載ランド16と電子部品3の部品装着領域との上に形成される空隙部23への樹脂分の流れ込みを阻止するために、配線基板22に対し部品装着孔24を塞ぐように樹脂流入阻止部15が搭載される。そして空隙部23は部品搭載ランド17と第2の電子部品3が装着される部品装着領域を覆う大きさとするとともに、部品装着孔24は部品装着領域の大きさより大きくすることにより、部品装着領域の上方を開放とし、部品搭載ランド17に電子部品3を装着可能とするものである。これによって、部品内蔵基板11には空隙部23の内部底面に形成された部品搭載ランド17へ電子部品3を装着可能にでき、高さの低い電子機器12を実現できる。

(もっと読む)

保護回路モジュール

【課題】 小型でかつ耐衝撃性や耐曲げ強度特性などの機械的強度特性に優れた保護回路モジュールを提供すること。

【解決手段】 2次電池に接続され、その2次電池の充電回路または放電回路の少なくとも1つを遮断する機能を有する保護回路モジュールであって、その上面に凹部11を有し凹部11の底部に単層または多層の配線2を有する絶縁支持基板1と、絶縁支持基板1の凹部11の内部に実装された半導体素子7,8とパッシブ素子9などの電子部品とにより構成されている。上記電子部品は絶縁物である樹脂16によって埋め込まれている。

(もっと読む)

フレキシブル回路基板及びこれを有する液晶表示装置

【課題】光源からの光が導電パターン及び受動素子などの所望しない領域に伝達されないようにするフレキシブル回路基板を提供する。

【解決手段】第1絶縁フィルム110と、第1絶縁フィルム110に形成された複数の導電パターン120と、第1絶縁フィルム110に形成され、複数の導電パターン120を覆う第2絶縁フィルム130と、導電パターン120に電気的に接続された少なくとも一つの光源140と、光源140の外周縁に形成され、光源140からの光が不要な領域に放出されることを防止する光吸収層160と、を含む。

(もっと読む)

光電複合配線モジュールおよび情報処理装置

【課題】狭小領域における配線が可能で、屈曲性および電磁ノイズ特性に優れる光電複合配線モジュールおよび情報処理装置を提供する。

【解決手段】この光電複合配線モジュール1は、配線部10と、配線部10の両端に設けられた一対の端子部11A,11Bとから構成され、配線部10の部分では、フレキシブルプリント配線基板2上に光導波路3を積層し、端子部11A,11Bの部分では、第2の電気配線23bを光回路部4A,4Bとは積層されない分離された領域に配置している。

(もっと読む)

配線基板及びその製造方法

【課題】配線基板の各層と電子部品との位置精度を向上させることにより、小型化を可能とし、さらに、一括で半導体素子、キャパシタ、抵抗体、及びインダクタ等の電子部品を配線基板内に内蔵させることより、製造時間及びコストを低減させる。

【解決手段】半導体素子、キャパシタ、抵抗、及びインダクタ等の電子部品が内蔵される配線基板において、各層の積層の際に、電子部品が実装されているフィルムキャリアのスプロケットホール等により位置合せを行うことで、配線基板の各層と電子部品との位置精度を向上させることにより、また、技術的に確立されたILB接続技術を用いることにより、半導体素子の狭ピッチ化への対応、接続の信頼性確保、さらには、上層に最短距離で配線を引き出しが可能となり、小型化を実現する。

(もっと読む)

プリント回路板及び電子機器

【課題】ピン挿入型電子部品の接続ピンをスルーホールに貫通させ、基板の表面に密着させて実装するプリント回路板において、半田ボールの発生を防止し、高い信頼性を実現することができるプリント回路板を提供する。

【解決手段】本発明に係るプリント回路板は、基板と、基板を貫通するスルーホールと、接続ピンを具備し接続ピンがスルーホールに貫通されると共に基板の部品実装面に密着して実装される電子部品と、を備え、スルーホールには電子部品の実装面側にざぐり部が設けられ、電子部品は、ざぐり部の一部、及びスルーホールの内部に充填された半田ペーストにより、リフロー処理によって基板に実装される、ことを特徴とする。

(もっと読む)

ヒューズ収容部付きプリント基板および自動車用電気接続箱

【課題】ヒューズ収容部付きプリント基板を改良して簡単な構造とする。

【解決手段】自動車用電気接続箱に組みつけるヒューズ収容部付きプリント基板であって、並列したヒューズ収容部を複数段備えているヒューズケースと、プリント基板の印刷導体と接続して突出するL字型の端子からなり、前記各段の前記ヒューズ収容部内に突出させる出力端子と、バスバーから分岐させたL字型の端子からなり、少なくとも1段の前記ヒューズ収容部内に突出させる入力端子と、前記ヒューズケースの裏面側に組みつけると共に、前記入力端子と出力端子を貫通させて保持している台座を備えている。

(もっと読む)

実装構造

【課題】複雑な治具を用いず電子部品を実装可能な実装構造を提供する。

【解決手段】ハウジング5aと、ハウジング5aに取り付けられた電子部品12,14と、電子部品12,14から立設されたピン状端子12a,14aを挿通させる貫通孔を備えた配線基板18とを備えると共に、ハウジング5aと配線基板18との間に配線基板18と共にハウジング5aに固定される実装補助部材20を備え、実装補助部材20には、ピン状端子12a,14aの向きを規制する貫通孔20a,20bが、ピン状端子12a,14aの先端を貫通孔20a,20bに案内するための傾斜案内面22a,22bと共に設けられている実装構造とした。

(もっと読む)

非常に強い電流がその中を流れることが可能なプリント基板及びそれに対応する製造方法

電子的コンポーネントを受けるようにデザインされ且つ上にプリントされた導電性トラック(12)を有するプリント回路または基板ボード(10)の上に、一つまたはそれ以上の導電性バー(18)が設けられ、これらの導電性バーは、導電性の接続面(140,142,144)の間に、順に取り付けられている。これらの導電性バー(18)は、後続のハンダ付けプロセスの間に電気的に相互に接続され、そのハンダ付けプロセスは、流動ハンダ付けプロセス、またはリフロー炉の中でのハンダ付けプロセスのいずれかである。 (もっと読む)

電子回路基板

【課題】電子回路基板や実装部品の設計上の品質を損なうことなく、端子の形状及び/又は位置が異なる実装部品を択一的に実装することが可能な電子回路基板を提供する。

【解決手段】実装部品の端子を接続する2組のランド(A1,A2,A3,A4,及び,B1,B2,B3,B4)を備える電子回路基板1であって、2組のランド間において、実装部品の各端子に対応するランド同士(A1とB1,A2とB2,A3とB3,及び,A4とB4)を互いに接続し、2組のランドを、一の組に含まれる各ランドの表面の重心を直線で結ぶことによって形成される領域の少なくとも一部が互いに重複する位置に設ける。

(もっと読む)

チップ部品の実装方法および電子モジュール

【課題】 基板面積を広げることなく、実装部品点数を増やすこと。

【解決手段】 電子モジュール(10A)は、表面(11a)と裏面(11b)と側面(11c)とを持つ実質的に直方体形状をしている。基板(11)は、表面(11a)上に形成された表面導体パターン(12)だけでなく、側面(11c)上に形成された側面導体パターン(22,23)をも持つ。表面実装用チップ部品(14)は、表面導体パターン(12)と電気的に接続されて、基板(11)の表面(11a)上に実装される。側面実装用チップ部品(24,25)は、側面導体パターン(22,23)と電気的に接続されて、基板(11)の側面(11c)上に実装される。

(もっと読む)

配線基板の製造方法、多層配線基板の製造方法

【課題】液滴吐出法を用いて電子部品の周囲に絶縁膜を形成する場合に、該絶縁膜上に形成される配線と前記電子部品との間で良好な導通を得ることを可能とした、配線基板の製造方法、多層配線基板の製造方法を提供する。

【解決手段】導電部20a,21aを有する電子部品20,21を、導電部20a,21aを上方に向けて基体10上に配置するとともに、導電部20a,21a上に導電性を有した突起12を設ける。そして、液滴吐出法を用いて電子部品20,21の周囲に、電子部品20,21と略同じ高さとなるように絶縁材料を塗布し、絶縁材料を硬化させて絶縁膜13を形成する。そして、絶縁膜13上に、突起12に接続する配線15を形成する。

(もっと読む)

プリント回路基板

【課題】 高速DRAMとメモリコントローラとを搭載したプリント回路基板における高速DRAMの安定動作を実現する。

【解決手段】 高速DRAM42とメモリコントローラ41とを搭載したプリント回路基板1において、メモリバス配線43の並列終端抵抗44の接続先であるVTT電源パターン20と、GNDパターン30との間に、コンデンサ45と、VTT電源パターンの特性インピーダンスとほぼ同じ抵抗値を持つ抵抗46との直列接続回路が設けられる。これにより、高速DRAMとメモリコントローラ41との動作に伴いVTT電源パターンに発生あるいは伝搬する高周波ノイズを当該直列接続回路で消費するようにした。

(もっと読む)

61 - 80 / 128

[ Back to top ]