Fターム[5E346BB06]の内容

多層プリント配線板の製造 (97,916) | 配線パターンの形状、構造 (5,951) | 信号層・電源層・グランド層の配置 (621)

Fターム[5E346BB06]の下位に属するFターム

電源層・グランド層を内層に設けるもの (283)

Fターム[5E346BB06]に分類される特許

201 - 220 / 338

共通結合領域を持つ埋め込みキャパシタデバイス

【課題】ICと外部キャパシタとの間に長い配線経路を持つ。

【解決手段】

上に集積回路を持つ回路基板内の埋め込みキャパシタデバイスが提供される。回路基板は、集積回路下に共通結合領域を持つ。埋め込みキャパシタデバイスは、少なくとも1つのキャパシタを集積回路の第1の組みの端子に与える第1のキャパシタセクションと、少なくとも1つのキャパシタを集積回路の第2の組みの端子に与える第2のキャパシタセクションとを含む。第1のキャパシタセクションの一部は、共通結合領域内にあり、そして、共通結合領域内に位置する第1の組みの端子への結合を持つ。同様に、第2のキャパシタセクションの一部は、共通結合領域内にあり、そして、共通結合領域内に位置する第2の組みの端子への結合を持つ。

(もっと読む)

配線基板および電子装置

【課題】ますます周波数の高くなる高周波信号を高速に伝送することが容易な配線基板を提供することにある。

【解決手段】接地導体層6と電源供給用導体層10とが絶縁層2を介して対向するように形成された配線基板において、接地導体層6および電源供給用導体層10の少なくとも一方の絶縁層側の主面に絶縁層に埋入した複数の突起12を形成している。

(もっと読む)

フレックスリジッド基板、光送受信モジュール及び光送受信装置

【課題】フレキシブル基板の配線をリジッド基板の最外層に引き出す際の、高周波信号の伝送特性を良好にすることを可能とするフレックスリジッド基板を提供する。

【解決手段】フレックスリジッド基板1は、フレキシブル基板のみにより構成されるフレキシブル基板部3と、フレキシブル基板の一部の上下にリジッド基板が積層されたリジッド基板部4とを備える。第一配線層及び第三配線層にマイクロストリップラインとして信号線路15が設けられ、これらは信号ビア17により接続される。第二配線層に形成されたグランド層16においては、各信号ビア17の周囲において所定の形状にグランド層が非形成となるグランド層開口部35を備える。グランド層開口部35は、第一配線層の信号線路15の配線方向の反対側となる領域において、グランド層が非形成となるように設けられる。

(もっと読む)

回路基板

【課題】信号配線上における特性インピーダンスの変動を小さく抑えることができる回路基板を提供すること。

【解決手段】グランド層6と、このグランド層に対して絶縁体層を介して信号配線3a,3bを配設したストリップ構造またはマイクロストリップ構造の回路基板において、前記グランド層を形成する導電部には、信号配線部に対峙する位置に多数の抜き孔bが形成される。前記各抜き孔間のピッチpが信号配線部の幅Lよりも小さくなされ、且つ抜き孔の形成領域6dが、前記信号配線部の幅Lを超える両外側の各幅Qを含む範囲になされる。前記両外側の各幅Qは、Q≧L/2の範囲に設定される。

(もっと読む)

フレキシブルプリント配線板、フレキシブルプリント回路板、およびそれらの製造方法

【課題】搭載する半導体チップの熱を有効に発散することができ、しかも電磁波のシールド性に優れ、屈曲性に富んで使用時の組み付け作業性のよいフレキシブルプリント回路板を作成すべく、材料コストが安く、製造工程数が少なく製作が容易で、しかも高価な装置を必要とせず、多層や両面に配線パターンを設けることができるフレキシブルプリント配線板の製造方法を提供する。

【解決手段】銅やアルミニウムなどよりなる金属基材50上に、例えば熱硬化性樹脂であるエポキシ系樹脂シートを熱と圧力とを加えることによりラミネートして接着剤である絶縁材52を設け、その絶縁材を介してその上に配線パターン53aを形成して後、その配線パターンのグランド配線部分に、ボンディングツール56を押し当てるなどによって熱と圧力とを加え、グランド配線部分を変形することにより、熱により軟化した絶縁材52中に埋没して金属基材50と接続する。

(もっと読む)

電子回路

【課題】電源回路と集積回路間を、伝送線路型ノイズフィルタを用いて良好にデカップリングする。

【解決手段】電源回路20は、集積回路であるマイクロプロセッサ30に供給すべき電源電圧を生成する。伝送線路型ノイズフィルタ10は、信号入力端子12、信号出力端子14および、それぞれに対応した2つの接地端子16、18を備え、信号入力端子12に印加された直流電圧の高周波成分を除去して信号出力端子14から出力する。プリント基板40に形成される第1電源ラインパターン42は、電源回路20の出力端子22を、伝送線路型ノイズフィルタ10の信号入力端子12に接続する。第2電源ラインパターン44は、伝送線路型ノイズフィルタ10の信号出力端子14をマイクロプロセッサ30の電源端子32に接続する。接地ランドパターン46は、ビアホールを介して外部の接地電位に接続され、かつ2つの接地端子16、18間を接続する。

(もっと読む)

配線基板内蔵用コンデンサ及び配線基板

【課題】配線基板に内蔵させた場合における導通不良を低減させることが可能な配線基板内蔵用コンデンサ、及びこれを備えた配線基板を提供する。

【解決手段】配線基板内蔵用コンデンサ1は、積層された複数のセラミック層3と、互いに異なるセラミック層3間に配置された複数の内部電極層4,5と、セラミック層3間にかつ内部電極層4,5よりセラミック層3の外周側に、内部電極層4,5と所定の間隔をおいて配置されたダミー電極層12,13とを備えている。

(もっと読む)

多層プリント配線板

【課題】 通常材料に比べて低誘電体損失材料は高価であるため、この材料を使用した多層プリント配線板が高価なものになるという課題がある。一方、目的に合わせて基板材料を使い分け、多層プリント配線基板内で低損失の信号伝送路を形成する為に必要な層のみを低誘電体損失材料を用いて形成し、価格上昇を最小限に抑える技術では、積層時の加熱圧着温度が各材料により異なるため一括積層ができない。

【解決手段】 そこで、多層プリント配線板を組み立てる材料として、絶縁材料に導体を貼り付けた基板材料と接着層に用いるプリプレグがあることに着目し、特性の異なる材料を組み合わせる場合は、先の基板材料とプリプレグの間で特性を変えることにより、課題である積層加熱圧着の温度を単一化する。

(もっと読む)

多層構造を持つ埋め込みキャパシタコア

【課題】ICと外部キャパシタとの間に長い配線経路を持つ。

【解決手段】

埋め込みキャパシタコアは、第1の組みのキャパシタ、第2の組みのキャパシタ、および第1の組みのキャパシタと第2の組みのキャパシタとの間の中間層誘電性フィルムを含む。第1の組みのキャパシタは、少なくとも2つの導電性電極を備える第1の導電性パターンと、第1の導電性パターンの2つの電極に対応する少なくとも2つの導電性電極を備える第2の導電性パターンと、および第1、第2の導電性パターンの間の第1の誘電性フィルムとを含む。第2の組みのキャパシタは、少なくとも2つの導電性電極を備える第3の導電性パターンと、第3の導電性パターンの2つの電極に対応する少なくとも2つの導電性電極を備える第4の導電性パターンと、および第3、第4の導電性パターンの間の第2の誘電性フィルムとを含む。

(もっと読む)

ストリップ線路とその製造方法

【課題】特殊な装置を用いずに簡単かつ短時間に製造でき、薄型で耐熱性にも優れたストリップ線路を提供する。

【解決手段】第1の基板1と第2の基板2とを両面接着テープ4を用いて線路3を挟持するように接着固定することでストリップ線路を形成する。この両面接着テープ4は、アクリル系の粘着剤と、剥離紙とから構成され、基材が無いため薄型であり、耐熱性に優れている。これにより、従来のストリップ線路の製造工程である高温度・高圧力の環境での接着が不要となり、常温の下で、手で抑える程度の圧力を加えることにより、短時間で両基板を接着することができる。

(もっと読む)

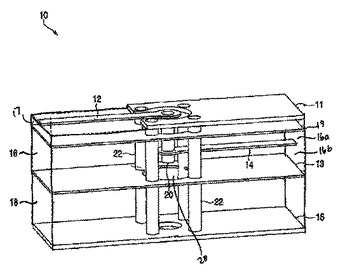

コンパクトな多層回路

コンパクトな多層信号処理システム10である。実施形態ではシステム10はマイクロ波信号で使用するように構成されている。システム10は入力信号を受信し、その入力信号を選択的に第1の信号パスへ導く第1の機構24を含む。第2の機構50-56、34、36、58-64は入力信号を第1の信号パスに沿って、1以上の層16-22を通る第1の回路コンポーネント96へ経路を指定する。第1の回路コンポーネント96は入力信号の受信に応答して調節された信号を出力する。第3の機構26、80-86、72、74、88-94は調節された信号をシステム10の出力78へ導く。特定の実施形態では、1以上の層16-22は1以上の接地平面層18、20を含んでいる。第1の機構24は制御装置40と通信する入力スイッチングネットワーク24を含む。スイッチングネットワーク24はスイッチング層14に位置され、入力信号を複数の入力信号パスのうちの1つへ選択的に切換えることを促すために1以上の制御装置40、44と通信する。第2の機構50-56、34、36、58-64は少なくとも1つの接地平面層18を通り垂直に入力スイッチングネットワーク24から第1の回路コンポーネント96の入力端部まで延在する第1の入力導波体50、54、34、58、62を含む。第3の機構26、80-86、72、74、88-94は1以上の水平な接地平面層18を通して垂直に第1の回路コンポーネント96の出力端部からスイッチング層14上に配置される出力スイッチングネットワーク26まで延在する第1の出力導波体80、84、72、88、92を含む。 (もっと読む)

時計IC用印刷配線基板及び時計IC用印刷配線基板の製造方法

【課題】製造工程の削減を図ることができ、しかも基準信号の発振周波数の調整を高精度に行なえるようにした時計IC用印刷配線基板を提供する。

【解決手段】電源層15のグランドベタパターン151のうち配線層16の発振回路パターン161と基板垂直方向に投射したときに重なる部分について当該発振回路パターン161と同一幅またはそれよりも広範囲の部分を除去したパターン抜き部152を形成するようにして、浮遊容量を無視できる値に低減するようにしている。また、グランド層12についても、グランドベタパターン121のうち配線層16の発振回路パターン161と基板垂直方向に投射したときに重なる部分について当該発振回路パターン161と同一幅またはそれよりも広範囲の部分を除去したパターン抜き部122を形成するようにしている。

(もっと読む)

回路基板

【課題】 信号配線上における特性インピーダンスの変動を小さく抑えることができる回路基板を提供すること。

【解決手段】 グランド層6と、このグランド層に対して絶縁体層を介して信号配線3a,3bを配設したストリップ構造またはマイクロストリップ構造の回路基板において、前記グランド層には、これを構成する導電部に多数の同一径による円形状の抜き孔bが形成されると共に、前記円形状の抜き孔bが互いに最密充填配置になされている。加えて、前記円形状の抜き孔bの中心点cを結ぶ線上における前記導電部の幅dが、前記信号配線3a,3bの幅eに等しいかもしくは狭く形成されている。

(もっと読む)

スループレーン・トランジションの最適化

基板は、第1のトレースを含む第1の金属層と、第2のトレースを含む第2の金属層と、第1及び第2の金属層の間に配置される誘電体層と、を有する。基板は、信号経路を形成するために誘電体層を横断する第1及び第2のトレースに電気的に結合される導電信号ビアをさらに有し、ビアの物理的特性は、ビアの信号経路特性が第1及び第2のトレースの信号経路特性と整合するように制御される。  (もっと読む)

(もっと読む)

多層回路基板およびその製造方法

【課題】伝送線路の高周波伝送特性を改善するとともに、設計の自由度を向上させた多層回路基板およびその製造方法を提供することを目的とする。

【解決手段】信号電極13とその信号電極13の左右に平行に設けられた1対の第1の接地電極14aとを有する第1の基板10aと、第1の接地電極14aと対向する位置に設けられた1対の第2の接地電極14bを有する第2の基板10bとを備え、第1の基板10aと第2の基板10bとの間に、第1の基板10aの第1の接地電極14aと第2の基板10bの第2の接地電極14bとを接続する導電体15と、少なくとも信号電極13の周囲に導電体15により設けた空間部12とを有することにより、高速データ伝送特性に優れた多層回路基板を得る。

(もっと読む)

アナログデジタル混在実装回路基板及び核医学診断装置

【課題】

アナログ信号配線とデジタル信号配線のスルーホール部分で発生するノイズ混入を防ぐアナログデジタル混在実装回路基板並びに該複数の回路基板を収納した観測ユニット部を有するPET装置またはSPECT装置等の核医学診断装置を提供する。

【解決手段】

基板の異なる面にアナログ信号系回路とデジタル信号系回路を搭載し、内層に遮蔽用電源層を配置した基板で、アナログ信号配線とデジタル信号配線を遮蔽用電源層から各信号系回路の側の内層に非貫通スルーホールを用いて接続し、アナログ信号系およびデジタル信号系の相互の回路間を接続する信号は、接続先の回路に入る部分のみスルーホール又は貫通スルーホールで接続を行うアナログデジタル混在実装回路基板。

(もっと読む)

多層配線基板及びその製造方法

【課題】 ゲインの微調整が可能で、歪み特性の優れた多層配線基板及びその製造方法を得る。

【解決手段】 実装状態で開口部が下向きとなるダウンキャビティ17を有するセラミック積層基板7と、ダウンキャビティ17内に搭載された二つの低ノイズ増幅器2と、セラミック積層基板7の上面7aに搭載された弾性表面波フィルタ3などを備えた多層配線基板。二つの低ノイズ増幅器2のそれぞれのエミッタ−グランド間に、低ノイズ増幅器2のそれぞれの周波数に対応する微小な整合用インダクタSL1,SL2が挿入されている。整合用インダクタSL1,SL2は同一層に形成され、セラミック積層基板7のキャビティ17を囲む壁部に配置されている。

(もっと読む)

回路基板、回路基板の製造方法および半導体装置

【課題】 実装される回路素子との接続信頼性が確保され、更に、寄生容量の低減およびノイズ対策が施された多層の回路基板およびその製造方法を提供する。

【解決手段】 本発明の回路基板10は、絶縁層11Cを介して積層された第1半導体基板11Aおよび第2半導体基板11Bから成る積層基板11を有する。積層基板11の上面には、第1導電パターン14が形成され、裏面には第2導電パターン15が形成される。接続電極16を介して、第1導電パターン14と第1半導体基板11Aとを電気的に接続することが出来る。更に、接続電極17を介して、第2導電パターン15と第2半導体基板11Bとを電気的に接続することが出来る。

(もっと読む)

配線基板

【課題】特別な防湿対策を施すことを不要にしながら、外部サージの放電のし易さが変動することを防止し、また、基板を小型化する。

【解決手段】本発明の配線基板は、基板1に少なくとも2層の配線層6〜10を設けて成るものにおいて、1つの配線層6に外部入力端子用パターン11を設け、上記1つの配線層6と異なる配線層10にグランドパターン12を設け、基板1にその板面に対して垂直方向にビアホール13を設け、このビアホール13に抵抗体14を充填し、そして、抵抗体14の上下端部を外部入力端子用パターン11及びグランドパターン12に接続したものである。

(もっと読む)

モニタ回路

【目的】 動作中の高周波回路特性に別段の影響を与えることなく、高周波信号を確実・安定にモニタ可能なことを課題とする。

【構成】 誘電体多層基板3A,3Bを挟んで表面の主線路1と背面の接地板2とを備えるストリップ線路のモニタ回路であって、主線路1直下の内層に該主線路と平行に設けた電磁結合部11Aと、該結合部と異なる方向に延展した導波部11Bとを有する内層パターン11を設け、前記導波部の端部と基板表面に設けた表面パターン12とをスルーホール13で接続することにより、主線路1との電磁結合により内層パターン11に抽出したモニタ信号を基板表面に取り出す。

(もっと読む)

201 - 220 / 338

[ Back to top ]