Fターム[5F003BB02]の内容

バイポーラトランジスタ (11,930) | ベース (1,440) | 付加領域(PN接合、絶縁物、溝、キラー) (83)

Fターム[5F003BB02]に分類される特許

1 - 20 / 83

半導体装置

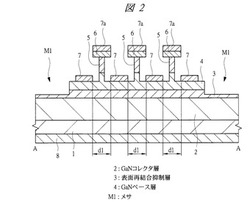

【課題】窒化物半導体を用いたメサ型の半導体装置のp型層の抵抗を低減する。また、窒化物半導体を用いたメサ型の半導体装置に高い値でばらつくオン抵抗が生じることを防ぐ。

【解決手段】窒化物半導体からなり、所定のベース電極間隔を有するヘテロ接合バイポーラトランジスタにおいて、GaNベース層4およびGaNコレクタ層2の間に表面再結合抑制層3を設け、GaNベース層4を貫通して表面再結合抑制層3の途中深さまで開口するメサM1を形成することでGaNベース層4を分離する。

(もっと読む)

バイポーラ半導体素子

【課題】高温や電流密度が高い条件下でも基板へ少数キャリアが到達するのを防いで、順方向電圧の増大を防ぐことができるバイポーラ半導体素子を提供する。

【解決手段】このSiC pinダイオード20では、n型SiC基板21とn型バッファ層22との間に形成したn型少数キャリア消滅層31は、n型バッファ層22よりも炭素空孔欠陥の濃度が高く、少数キャリア消滅層31の炭素空孔欠陥はp型のアノード層24,25からの正孔のトラップとして働く。よって、小数キャリア消滅層31に達した正孔(少数キャリア)がトラップされ、小数キャリア消滅層31において正孔密度K2が急激に減衰する。これにより、正孔(少数キャリア)が基板21へ到達することを防いで、基板21から積層欠陥が拡大するのを防いで、順方向電圧の増大を防止できる。

(もっと読む)

半導体装置

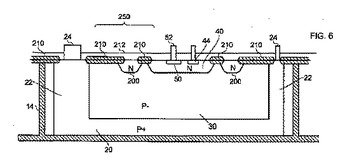

【課題】電力破壊を抑制できる半導体装置を提供すること。

【解決手段】ベース領域12の表面に設定されたベースコンタクト領域14において、ベース電極15がベース領域12に接合されている。ベースコンタクト領域14の境界部の下方には、エミッタ領域13と同じ導電型を有するN型領域21がベースコンタクト領域14を包囲するように形成されている。言い換えれば、ベースコンタクト領域14の境界部の下方において、P型のベース領域12およびN型領域21によりPN型の寄生ダイオードが形成されている。

(もっと読む)

バイポーラトランジスタ

エミッタ領域(50)と、ベース領域(40)と、コレクタ領域(20)と、ベース領域(40)から離間し、それを囲む、保護領域(200)とを備える、バイポーラトランジスタ。保護領域(200)は、ベース領域(40)を形成するために使用される同一ドーピングマスクを使用して形成することができ、動作中には、空乏層を展開する役割を果たすことができる。また、本発明は、上記バイポーラトランジスタを製造する方法であって、エミッタ領域と、ベース領域と、コレクタ領域とを形成することと、該ベース領域を囲む保護領域を形成することとを含む、方法も提供する。  (もっと読む)

(もっと読む)

有機トランジスタ、回路素子及びそれらの製造方法

【課題】低電圧で作動するとともに大きなベース電圧を印加した場合でも耐電圧が高く、各種の回路素子への応用が容易で、製造コストを抑えた有機トランジスタ及び回路素子を提供する。

【解決手段】コレクタ電極1とエミッタ電極2と両電極間に設けられた有機半導体層3と有機半導体層3内に設けられたベース電極4とを有する縦型トランジスタ部、及び、ベース電極4とベース電圧電源端子7との間に設けられた抵抗部6、を有する。抵抗部6は、コレクタ電極1と同じ材料からなりベース電圧電源端子7に接続する第1電極21と、エミッタ電極2と同じ材料からなりベース電極4に接続する第2電極22と、有機半導体層3と同じ材料からなり第1電極21及び第2電極22間に挟まれた抵抗層24とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バイポーラトランジスタが動作する際に、ベース領域のうちコレクタ側の端部が破壊されることを抑制する。

【解決手段】ベース領域150は、ウェル110内に形成されている。エミッタ領域170はベース領域150の中に形成され、ベース領域150より浅い。コレクタ領域140はウェル110内に形成され、ベース領域150の外側に位置している。第1埋込領域180は、少なくとも一部がベース領域150の中に位置しており、ベース領域150よりも不純物濃度が高い。そして第1埋込領域180は、平面視において、エミッタ領域170とコレクタ領域140の間に少なくとも一部が位置している。また第1埋込領域180は、エミッタ領域170の縁のうち少なくとも一辺と重なっており、かつエミッタ領域170の全面には重なっていない。

(もっと読む)

バイポーラ・トランジスタ構造およびその製造方法

【課題】エミツタ・ベース間の接合界面特性の最適化により、性能が改善されたバイポーラ・トランジスタ構造そのおよび製造方法を提供する。

【解決手段】バイポーラ・トランジスタは、(1)半導体基板内に少なくとも部分的に位置決めされたコレクタ領域15と、(2)コレクタ領域に接触するベース領域16と、(3)ベース領域に接触するエミッタ領域16Aとを含む。エミッタ領域とベース領域の界面は、酸素不純物と、フッ素不純物および炭素不純物から成るグループから選ばれた少なくとも1つの不純物とを含む損傷領域16Aをエミツタ開口のベースを含む層16に形成することにより、バイポーラ・トランジスタの性能を改善する。それらの不純物は、ベース領域を構成するベース材料のプラズマ・エッチング処理または代わりに無水アンモニアおよびフッ化水素処理が後に続く熱処理によって界面に導入することができる。

(もっと読む)

バイポーラトランジスタ

【課題】表面酸化膜下の界面近傍で発生する降伏を防ぎ、ツェナー降伏によるブレークダウン電圧の経時変動を防ぐバイポーラトランジスタを提供することを目的としている。

【解決手段】第一導電型半導体基体3内に不純物濃度が第一導電型半導体基体3より高い第一導電型の電流経路領域4と、電流経路領域4内に第二導電型の表面降伏防止領域5と、第一導電型半導体基体3表面に電流経路領域4と表面降伏防止領域5に接し不純物濃度が表面降伏防止領域5より高い第二導電型のベース領域6と、第一導電型半導体基体3表面に電流経路領域4と表面降伏防止領域5に接する第一導電型コレクタ領域7と、第一導電型半導体基体3表面かつ表面降伏防止領域5内に不純物濃度が電流経路領域4より高い第一導電型のエミッタ領域8と、表面降伏防止領域5内かつエミッタ領域8に接する不純物濃度が表面降伏防止領域5より高い第一導電型内部降伏誘導領域9を備える。

(もっと読む)

静電破壊保護回路

【課題】静電破壊保護回路の大きさを変えることなく、保持電圧を向上させることができ、保持電圧の制御を可能とする静電破壊保護回路を提供する。

【解決手段】ベース領域12の表面に、エミッタ領域6近傍からコレクタ端子側1へベース領域より不純物濃度が高いP型拡散領域20を備える構造とすることで、保持電圧を増加させることができ、P型拡散領域の長さにより保持電圧の値を設定することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】SOA(安全動作領域)拡大と良好な静特性とを同時に達成するトランジスタを提供する。

【解決手段】第1導電型のコレクタ層(2)と、前記コレクタ層上に形成される第2導電型のベース層(3)と、前記ベース層上に島状に形成される第1導電型のエミッタ層(4)と、前記ベース層とベース電極(11)とが電気的に接続されるとベースコンタクト(11’)と、前記エミッタ層とエミッタ電極(12)とが電気的に接続されるエミッタコンタクト(12’)と、を有する半導体装置であって、

平面的に見て前記ベースコンタクトと前記エミッタコンタクトとの間に形成されるトレンチ(6)を備えることを特徴とする半導体装置。

(もっと読む)

接合の作製方法

【課題】バイポーラトランジスタのエミッタ−ベース界面において、ドーパント濃度プロファイルを制御する方法を提供する。

【解決手段】第1濃度を有する第1ドーパントを含む第1半導体材料を形成する工程と、その上に、第2濃度を有し、これにより接合を形成する、第2ドーパントを含む第2半導体材料を形成する工程と、第2半導体材料を形成する前に、原子層エピタキシまたは気相ドーピングにより、第1半導体材料の上に、第2ドーパントを形成するのに適した、単分子層の少なくとも一部分の前駆体を堆積し、これにより接合における第2ドーパントの第2濃度を増加させる工程と、を含む(またはこれらの工程からなる)。

(もっと読む)

静電破壊保護回路

【課題】 静電破壊保護回路の動作開始電圧を下げるためトリガ素子を接続した場合であっても、静電破壊保護回路の静電破壊耐量を向上させることができる静電破壊保護回路を提供する。

【解決手段】 トリガ素子が接続される別のベース電極部拡散領域の周囲に、ベース領域より不純物濃度が低く、かつベース領域より深く形成されたP型拡散領域11を備える構造とすることで、別のベース電極部拡散領域近傍で生じる高電界を緩和し、またコレクタの一部を構成する埋め込み領域近傍で、ベース電流供給に必要な高電界を生じさせることができ、静電破壊耐量を向上させている。

(もっと読む)

半導体装置、光ディスク装置

【課題】電流利得のばらつきを低減することができる半導体装置を提供する。

【解決手段】第1導電型の半導体基体1と、この半導体基体1の表面の一部に形成された、バイポーラトランジスタの第2導電型のコレクタ層2と、このコレクタ層2の一部に形成された、バイポーラトランジスタの第1導電型のベース層6と、このベース層6の一部に形成された、バイポーラトランジスタの第2導電型のエミッタ層7と、このエミッタ層7の直下の領域を除いた部分の半導体基体1に形成された、第1導電型の半導体層9とを含む半導体装置を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の特性を向上できると共に、製造コストを低減できる。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1上に順次積層されたコレクタ層2A、ベース層3A及びエミッタ層4Aと、コレクタ層2Aの側面上に設けられ、コレクタ層に対して歪み応力を与える第1ストレスソース膜15Aと、ベース層3Aの側面上に設けられ、ベース層3Aに対して歪み応力を与える第2ストレスソース膜17と、を具備し、第1ストレスソース膜15A上端及び前記ベース層上端は、半導体基板表面から同じ高さに位置し、第2ストレスソース膜17は、ベース層3Aの側面と第1ストレスソース膜15Aの側面との間に設けられる。

(もっと読む)

新構造半導体集積回路

【課題】現在、半導体集積回路で使用されているバイポーラトランジスタとMOSトランジスタは最初に発明された時よりその構造は変わっておりません。構造と原理を根本的に見直し、高速化・低消費電力化・微細化を進展させる。

【解決手段】サブミクロンスケールの微細加工技術を用い、新しい原理と構造のトランジスタによる半導体集積回路を形成する。

(もっと読む)

電流シフト領域を有する半導体デバイスおよび関連方法

半導体デバイスは、第1の伝導形を有する半導体バッファ層と、バッファ層の表面上にあって第1の伝導形を有する半導体メサとを含む。さらに第2の伝導形を有する電流シフト領域が半導体メサと半導体バッファ層との間の隅に隣接して設けられ、第1と第2の伝導形が互いに異なる伝導形である。関連する方法も開示される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、半導体装置及びその製造方法等に関し、バイポーラトランジスタの面積を縮小してトランジスタの高集積化が可能な半導体装置及びその製造方法等提供する。

【解決手段】本発明に係る半導体装置及びその製造方法は、第1導電型半導体にベース領域6を形成後、第1のシリコン窒化膜8及びシリコン酸化膜9を形成する。シリコン酸化膜に溝を形成し、第2のシリコン窒化膜10を形成する。第1及び第2のシリコン窒化膜をエッチバックすることでカバー膜10aを形成する。溝の底面上及びカバー膜の内側にポリシリコンエミッタを形成し、第3のシリコン窒化膜13を形成する。第3のシリコン窒化膜及びカバー膜をマスクとして自己整合的にシリコン酸化膜をエッチングすることで、カバー膜の周囲に位置し且つ前記ベース領域上に位置する開口部を形成し、ベース領域を露出させ、導電膜17aを形成する工程とを具備することを特徴とする。

(もっと読む)

半導体装置

【課題】耐圧の異なるトランジスタを容易に形成することができる半導体装置を提供すること。

【解決手段】本発明にかかる半導体装置は、ボディシリコン層23、低耐圧のトランジスタ40、及び高耐圧のトランジスタ30を有する。トランジスタ40では、高濃度コレクタ領域42及びベース領域43が、半導体層23に設けられた低濃度コレクタ領域41に接する。また、トランジスタ30では、ボディシリコン層23に設けられた低濃度コレクタ領域31に接する、高濃度コレクタ領域32及びベース領域33において、ボディシリコン層23の主表面に対して平行方向の距離が、高濃度コレクタ領域32及びベース領域33よりも離れて設けられている。

(もっと読む)

バイポーラトランジスタ及びその製造方法

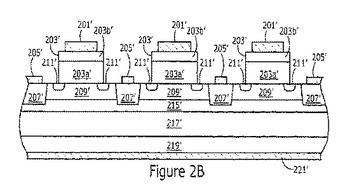

【課題】バイポーラトランジスタの高周波特性の向上を図る。

【解決手段】p型シリコン基板10上に形成されたn型導電型の第1コレクタ層14と、第1コレクタ層14上に形成された、第1コレクタ層14より幅の狭い、n型導電型の第2コレクタ層21と、第1コレクタ層14上に、第2コレクタ層21側面に接して形成された絶縁膜層20と、第2コレクタ層21上に形成された、p型導電型のベース層22と、ベース層22側面に接してに形成された、p型導電型のベース引き出し層25と、ベース層22上に形成された、n型導電型のエミッタ領域32とを備える。第1コレクタ層14とベース層22の間、又は第1コレクタ層14とベース引き出し層25の間に、絶縁膜層20が形成されていることにより、ベース・コレクタ間の接合容量を低減させる。

(もっと読む)

ポリエミッタ型バイポーラトランジスタ、BCD素子、ポリエミッタ型バイポーラトランジスタの製造方法及びBCD素子の製造方法

【課題】複合高電圧素子工程を用いたポリエミッタ型バイポーラトランジスタ及びその製造方法、BCD(複合高圧)素子及びその製造方法を提供する。

【解決手段】実施の形態に係るポリエミッタ型バイポーラトランジスタは、半導体基板100の上側の一部に形成された埋込層110と、上記半導体基板の上に形成されたエピ層120と、上記エピ層に形成され、上記埋込層と連結されるコレクタ領域130と、上記エピ層の上側の一部に形成されたベース領域140と、上記ベース領域の基板の表面に形成され、ポリシリコン材質からなるポリエミッタ領域170と、を含む。実施の形態に係るBCD素子は、ポリシリコン材質からなるポリエミッタ領域を含むポリエミッタ型バイポーラトランジスタを含み、上記バイポーラトランジスタと同一な単一ウエハ上に形成されたCMOSとDMOSのうちの1つ以上のMOSを含む。

(もっと読む)

1 - 20 / 83

[ Back to top ]