Fターム[5F003BC01]の内容

バイポーラトランジスタ (11,930) | コレクタ (1,152) | 不純物濃度分布 (218)

Fターム[5F003BC01]に分類される特許

1 - 20 / 218

半導体装置

【課題】ホールド電圧が高いエミッタ・ベース短絡型の保護素子が設けられた半導体装置を提供する。

【解決手段】半導体装置1は、基板10と、前記基板上に形成された第1導電形の半導体層11と、前記基板と前記半導体層との間に形成された第1導電形の埋込層13と、前記半導体層上に形成された第2導電形のウェル14と、前記半導体層上であって、前記ウェルから離隔し、前記埋込層の直上域に形成された第1導電形の第1コンタクト層15と、前記ウェル上に形成された第2導電形の第2コンタクト層16と、前記ウェル上であって、前記第1コンタクト層と前記第2コンタクト層との間に形成された第1導電形の第3コンタクト層17と、前記埋込層と前記第1コンタクト層との間に形成され、前記第1コンタクト層に接した第1導電形のディープ層18と、を備える。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタの形成領域において半導体層の下部に絶縁層を有する基板が用いられた半導体装置において、バイポーラトランジスタの電流増幅率を向上させる。

【解決手段】バイポーラトランジスタは、半導体層1cに形成されたコレクタ5、ベース7、エミッタ9、ベース用高濃度オーミック拡散層11及びコレクタ用高濃度オーミック拡散層13、並びに半導体層1c上に形成されたゲート絶縁膜15及びゲート電極17を備えている。ベース7は、絶縁層1bに達する深さで形成され、上方から見てゲート電極17と一部重複して形成され、ゲート電極17下でコレクタ5に隣接して形成されている。ベース7は、ベース7側のゲート電極17の端部からコレクタ5側に向かってP型不純物濃度が低くなる濃度傾斜をもっている。

(もっと読む)

III−V族化合物半導体エピタキシャルウエハ

【課題】充分な選択比を備え、また、除去が比較的容易なエッチングストッパ層を得る。

【解決手段】GaAs基板10上に設けられた高電子移動度トランジスタ構造20と、高電子移動度トランジスタ構造20の上に設けられたヘテロ接合バイポーラトランジスタ構造40と、を備え、高電子移動度トランジスタ構造20とヘテロ接合バイポーラトランジスタ構造40との間には、As濃度が1.0×1016atoms/cc以上1.0×1021atoms/cc以下のInGaAsP層からなるエッチングストッパ層30を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】InP系の微細構造デバイスをより効果的に冷却できるようにする。

【解決手段】主表面を(001)面としたInPからなる基板101の上にInGaAsからなるバッファ層102を形成し、バッファ層102の上に接して配置されたInPの層を含んでバッファ層102の上に形成されたデバイス103を形成し、デバイス103の周囲のバッファ層102を露出させた状態でデバイス103を覆う保護層104を形成し、露出したバッファ層102の上に金を堆積して金層105を形成し、次に、バッファ層102の表面に接触している金層105よりデバイス103の下部のバッファ層102に金を拡散させる。

(もっと読む)

半導体装置及びその製造方法

【課題】異なる不純物濃度の埋め込み層を有する半導体装置を短時間かつ低コストで製造する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の表面に第1の酸化膜11を形成する第1の酸化膜形成ステップと、フォトダイオードが形成される第1の領域に形成された前記酸化膜の一部を除去して第1の間隔で第1の開口部を形成すると共に、トランジスタが形成される第2の領域に形成された前記酸化膜を除去して前記半導体基板の表面を露出させる第1の開口部12を形成ステップと、前記第1の酸化膜をマスクとして利用して前記第1の開口部及び前記第2の領域に対して第1の不純物を注入する第1の不純物注入ステップと、前記第1の不純物を熱拡散させる第1の熱拡散ステップと、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】埋め込み絶縁層により活性層と支持基板とが電気的に絶縁された半導体基板において、支持基板の電位を活性層の表面から取り出すための基板コンタクトの低抵抗化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】活性層16に素子領域4およびコンタクト領域5が形成された厚膜SOI基板2において、CMOSトランジスタ7のB/L層29およびL/I層37、npnバイポーラトランジスタ8のコレクタ層49と同一層に、n型基板コンタクト12の貫通コンタクト58を取り囲むn型コンタクト埋め込み層57を形成する。

(もっと読む)

半導体装置

【課題】デバイスサイズの縮小、シリーズ抵抗の低減、及びリーク電流の抑制を可能とする半導体装置を提供することを目的とする。

【解決手段】本発明は、デバイス動作にとって、本来は不要な電位段差を発生させる層をデバイスの構造内にあえて挿入したものである。この電位段差は、バンドギャップの小さな半導体がメサ側面に露出しても、その部分の電位降下量を抑制し、デバイス動作に不都合なリーク電流を低減できる、という機能をもたらす。この効果は、ヘテロ構造バイポーラトランジスタ、フォトダイオード、及び電界吸収形光変調器などに共通して得られる。また、フォトダイオードにおいては、リーク電流が緩和されるのでデバイスのサイズを縮小することが可能となり、シリーズ抵抗の低減による動作速度の改善のみならず、デバイスを高密度にアレイ状に配置できるという利点も生まれる。

(もっと読む)

バイポーラ半導体素子

【課題】表面欠陥を低減でき、オン電圧ドリフトを抑制できるバイポーラ半導体素子を提供する。

【解決手段】このSiC GTOによれば、メサ状のp型アノードエミッタ層5の長側面5Bが延在している方向を、〈11−20〉方向としたオフ方向から角度φ=60°だけ傾斜させた方向とした。これにより、長側面5Bは、{01−10}面となり、{11−20}面である短側面5Cに比べて、表面欠陥が入りにくくなる。また、長側面5Bの延在方向を、上記オフ方向から角度φ=60°だけ傾斜させたことで、長側面5Bの延在方向とオフ方向とが一致している場合(φ=0°)に比べて、メサ状のp型アノードエミッタ層5の長側面5Bに現れる{0001}面の層の数を減らすことができて、{0001}面の層内に入る表面欠陥を減少できる。

(もっと読む)

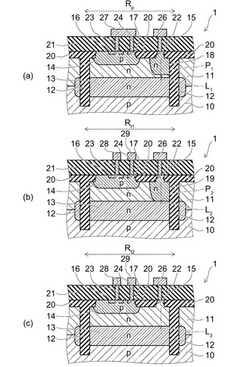

半導体装置

【課題】 放熱性を改善したバイポーラトランジスタを有する半導体装置を提供することにある。

【解決手段】 複数のバイポーラトランジスタQuが配列される半導体装置であって、エミッタ配線L3は幅広部と細長部とを有し、細長部におけるバイポーラトランジスタ素子数が、幅広部が配置された配列の外縁に沿う方向に配列されたバイポーラトランジスタ素子数よりも少なくなるように配置する。

【効果】エミッタ配線の寄生抵抗によるエミッタ−ベース間電圧ばらつきを低減する。

(もっと読む)

半導体素子

【課題】 GaN基板上に結晶成長する各半導体層の平坦性向上した半導体基板を実現し、この半導体基板を基礎として、特性の高性能化された半導体素子を提供する。

【解決手段】n型基板11と、n型基板11上に積層された窒化物系III−V族化合物半導体単結晶からなるn型ドリフト層24と、n型ドリフト層24上に設けられた窒化物系III−V族化合物からなるp型ベース層25と、p型ベース層25上に設けられた窒化物系III−V族化合物からなるn型エミッタ層26と、n型基板11とn型ドリフト層24との間に設けられた、Siを5x1017cm-3以上2x1019cm-3以下含有する層とを備える。

(もっと読む)

バイポーラ接合トランジスタ

【課題】アナログアプリケーションの性能向上と共に、DCゲインおよび効率の増加を提供する。

【解決手段】バイポーラ接合トランジスタは、絶縁基板上の島状半導体と、島状半導体内に、第1伝導性型であるエミッタ、並びに第1伝導性型であるコレクタおよび/またはサブコレクタと、島状半導体内に、エミッタと、コレクタおよび/またはサブコレクタとを分離する、第2伝導性型であるベースと、島状半導体内に、第2伝導性型であるベース接触領域と、島状半導体内に、ベースに隣接するとともに、ベースをベース接触領域に接続する一方で、エミッタとは直接接触していない接続ベース領域と、を備え、接続ベース領域は、第2伝導性型であり、ベース接触領域のドーピング濃度未満のドーピング濃度を有する。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタにおいてオフ耐圧及び破壊電流量の双方を高くする。

【解決手段】第2のベース領域116は、ディープウェル112の表層に形成されており、平面視において第1のベース領域114とシンカー110との間に位置している。そして第2のベース領域116は、第1のベース領域114に接続しており、第1のベース領域116よりも不純物濃度が高く、かつ第1のベース領域116よりも深さが浅い。埋込層108は、半導体層106に形成され、上面がディープウェル112及びシンカー110に接しており、ディープウェル112よりも不純物濃度が高い。

(もっと読む)

バイポーラ半導体素子

【課題】ドリフト層とドリフト層に隣接する層との界面の応力を低減して、順方向電圧を低く抑えることができるバイポーラ半導体素子を提供する。

【解決手段】このpinダイオード20は、n型SiCドリフト層23の膜厚の各範囲(300μm以下200μm超),(200μm以下100μm超),(100μm以下50μm超)に対応して、n型SiCバッファ層22の不純物濃度の各上限値(5×1017cm−3),(7×1017cm−3),(10×1017cm−3)が設定されている。これにより、n型SiCドリフト層23とn型SiCバッファ層22との界面の応力を低減でき、順方向電圧を低減できる。

(もっと読む)

半導体装置

【課題】同一基板上にヘテロ接合バイポーラトランジスタ(HBT)と電界効果トランジスタ(FET)とが形成され、HBTのコレクタ抵抗が低減されてHBTの特性が向上され、かつFETのゲートリセスのエッチング精度が良好で、FETのオン抵抗が低い半導体装置を安定的に提供する。

【解決手段】HBT101Aにおいては、サブコレクタ層が複数の半導体層13〜15の積層構造からなり、かつ、サブコレクタ層においてコレクタ層17より張り出した部分上にコレクタ電極28が形成されている。FET101B、101Cにおいては、HBT101Aのサブコレクタ層をなす複数の半導体層のうち半導体基板1側の少なくとも1層の半導体層13が、キャップ層の少なくとも一部の層を兼ねている。HBTサブコレクタ層の総膜厚が500nm以上であり、FETキャップ層の総膜厚が50nm以上300nm以下である。

(もっと読む)

バイポーラ半導体素子

【課題】高温や電流密度が高い条件下でも基板へ少数キャリアが到達するのを防いで、順方向電圧の増大を防ぐことができるバイポーラ半導体素子を提供する。

【解決手段】このSiC pinダイオード20では、n型SiC基板21とn型のドリフト層23との間に形成されている厚さを20μmとしたn型のバッファ層22が、p型のアノード層24,25からの正孔のトラップとして働いて、正孔(少数キャリア)がn型SiC基板21へ到達することを防ぐ。これにより、正孔(少数キャリア)がn型SiC基板21へ到達することを防いで、n型SiC基板21から積層欠陥が拡大するのを防いで、順方向電圧の増大を防止できる。

(もっと読む)

半導体装置

【課題】III-V族窒化物半導体に設けるオーミック電極のコンタクト抵抗を低減しながらデバイスの特性を向上できるようにする。

【解決手段】半導体装置(HFET)は、SiC基板11上にバッファ層12を介在させて形成された第1の窒化物半導体層13と、該第1の窒化物半導体層13の上に形成され、該第1の窒化物半導体層13の上部に2次元電子ガス層を生成する第2の窒化物半導体層14と、該第2の窒化物半導体層14の上に選択的に形成されたオーム性を持つ電極16、17とを有している。第2の窒化物半導体層14は、底面又は壁面が基板面に対して傾斜した傾斜部を持つ断面凹状のコンタクト部14aを有し、オーム性を持つ電極16、17はコンタクト部14aに形成されている。

(もっと読む)

電流増幅素子

【課題】なだれ増倍を利用して電流を直接増幅することが可能であると共に、リニアモード動作において、高感度と応答速度の速さとを両立させることができる電流増幅素子を提供する。

【解決手段】電流増幅素子は、半導体基板の表面に平面視が円形となるように中心軸の周りに対称に形成されたn型半導体ウエル(n−ウエル)104、n−ウエル内に同心円状に形成されたp型半導体領域112、p型半導体領域内に同心円状に形成されたn型半導体領域112、及び順バイアス電圧と逆バイアス電圧とを印加するための複数の電極を備えている。n−ウエルの内側の面は、中心軸から予め定めた距離の範囲内では基板裏面に向って半径が小さくなると共に、範囲より外側では基板裏面に向って半径が大きくなるように形成されている。

(もっと読む)

ヘテロ接合バイポーラトランジスタの製造方法、及びヘテロ接合バイポーラトランジスタを用いた電力増幅器

【課題】InGaPをエミッタ層として有し、熱的安定性と通電に対する信頼性を両立することの出来るHBTを用いた電力増幅器を提供する。

【解決手段】InGaPエミッタ層を有するHBTにおいて、InGaPエミッタ層5とAlGaAsバラスト抵抗層7の間にGaAs層6を挿入し、ベース層4から逆注入された正孔がAlGaAsバラスト抵抗層7まで拡散、到達することを抑制する。

(もっと読む)

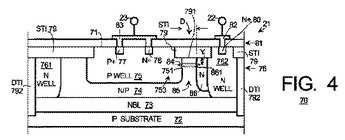

ESD保護デバイスおよび方法

関連するデバイスまたは回路24を保護する静電気放電(ESD)保護クランプ21、21’、70、700は、バイポーラ21、21’、70、700を備える。アバランシェ降伏が、上にある誘電体・半導体界面791から離れ、デバイス70、700のベース領域74、75の部分84,84以内に望ましく起こるように向かうベース75およびコレクタ86領域のドーパントを構成される。例えば、半導体ダイまたはウェハのトランジスタ21、21’、70、700の異なる方位配向のおかげで、ESDトリガ電圧の最大変化(△Vt1)MAXはベース・コレクタ間隔寸法Dの関数である。トリガ電圧一貫性および製造歩留まりが改良される。  (もっと読む)

(もっと読む)

半導体デバイスおよびその製造方法

【課題】CMOS回路側の仕様で不純物領域の深さや濃度が制約を受けるような場合でもhFEの向上を可能とする。

【解決手段】1つのバイポーラトランジスタが、横型の主トランジスタ部と、縦型の補助トランジスタ部とから形成されている。横型の主トランジスタ部は、エミッタ領域31と、ベース領域14Bの表面側部分とコレクタ側部領域13Bとを電流チャネルとして動作する。縦型の補助トランジスタ部は、エミッタ領域31と、その底面に接するベース領域14Bの深部側部と、コレクタ深部領域12Bとを電流チャネルとして動作する。

(もっと読む)

1 - 20 / 218

[ Back to top ]