Fターム[5F003BH08]の内容

バイポーラトランジスタ (11,930) | 電極、配線 (1,046) | 電極材料 (587) | 多層構造 (155)

Fターム[5F003BH08]に分類される特許

121 - 140 / 155

SiC半導体素子

【課題】 逆方向電圧が印加された場合の素子破壊の発生を低減することができるSiC半導体素子を提供する。

【解決手段】 高濃度のn型SiCからなる高濃度層101の一方の表面上には、低濃度のn型SiCからなる低濃度層102が形成されている。低濃度層102内には、高濃度層101と接するように、n型SiCからなる埋め込み層103が形成されている。低濃度層102の表面領域には、p型SiCからなるガードリング領域104が形成されている。低濃度層102およびガードリング領域104上にはショットキー電極120が形成されている。高濃度層101の他方の表面上にはオーミック電極121が形成されている。

(もっと読む)

化合物半導体デバイスの製造方法

【課題】 半導体層表面の凝集In粒子に起因する電気的特性の低下を防止することが可能な化合物半導体デバイスの製造方法を提供する。

【解決手段】 表面に凝集In粒子103が点在するInGaAsエピタキシャル層上にプラズマSiO2膜102を形成し、所定の領域のプラズマSiO2膜102を除去し、除去により露出したInGaAsエピタキシャル層101に酸素プラズマによるアッシングを施して表面の凝集In粒子103を強制的に酸化させ、アッシングが施されたInGaAsエピタキシャル層101に例えば1分間以上の期間HCL溶液によるウェットエッチングを施して表面の酸化した凝集In粒子103を除去し、下部電極となるTi/Pt/Au層105を形成する。

(もっと読む)

半導体素子および電界効果トランジスタ

【課題】 良好なショットキー特性を有する電極を備えた半導体素子を提供する。また、良好なショットキー特性を有するゲート電極を備えた電界効果トランジスタを提供する。

【解決手段】 n型GaN層3の上に形成されたショットキー電極6は、WNx層4を有し、n型GaN層3とWNx層4とが接触する面において、n型GaN層3の結晶面は六方晶の(0001)面であり、WNx層4の結晶面は(111)面に配向している。WNx層4は、Zr、Ha、Nb、Ta、MoおよびWよりなる群から選ばれる少なくとも1種の元素と、窒素および炭素の少なくとも一方の元素とからなる塩化ナトリウム型構造の電極層であればよい。また、電極層の格子定数は、n型GaN層3におけるa軸格子定数を2(1/2)倍した値の0.95倍〜1.05倍であることが好ましい。

(もっと読む)

SiC半導体素子

【課題】 逆方向電圧が印加された場合の素子破壊の発生を低減することができるSiC半導体素子を提供する。

【解決手段】 高濃度層11は、高濃度のn型SiCからなる層であり、SiC基板を構成している。高濃度層11の表面には、低濃度のn型SiCからなる低濃度層12が形成され、低濃度層12の表面には、p型SiCからなるガードリング領域13が形成されている。低濃度層12およびガードリング領域13の上には、低濃度層12とショットキー接合を形成しているバリアメタル膜14、パッド電極15、および絶縁膜16が形成されている。高濃度層11の他方の面には、高濃度層11とオーミック接合を形成しているオーミックメタル膜17および裏面電極18が形成されている。低濃度層12において、ガードリング領域13の近傍には、低濃度層12の表面に露出するように結晶欠陥領域19aが形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 本願発明は、コレクタトップ型HBTにおいて、外部ベース直下のエミッタ層の狭窄化とベース・エミッタ接合容量の低減化を微量なサイドエッチ量で実現し、エミッタトップ型HBTにおいては、ベース・コレクタ接合容量の低減化を実現することの出来るHBTを提供することにある。

【解決手段】 コレクタトップ型HBTの場合、コレクタ側壁周辺の窓構造を利用して外部ベース層直下エミッタ層あるいはエミッタコンタクト層のエッチングを行い、エミッタトップ型のHBTの場合、エミッタ側壁周辺の窓構造を利用して外部ベース直下コレクタ層あるいはコレクタコンタクト層のエッチングを行なう。両HBT共に、外部ベース層は柱構造で支持され機械的強度が確保されている。

(もっと読む)

半導体装置およびその製造方法ならびに電子装置

【課題】 熱的安定性と信頼性を両立し、さらに静電破壊耐量を向上したHBTを備えた半導体装置を提供する。

【解決手段】 化合物半導体からなる基板の主面上に、順に形成されたサブコレクタ層、コレクタ層、ベース層4およびエミッタ層5、ならびにコレクタ層4と電気的に接続されたコレクタ電極、ベース層4と電気的に接続されたベース電極、エミッタ層5上に形成され、エミッタ層5と電気的に接続されたエミッタメサ層6M、およびエミッタメサ層6Mと電気的に接続されたエミッタ電極13を備えたHBTであって、このエミッタメサ層6Mが、n型GaAs層からなる半導体層6と、半導体層6上のn+型GaAs層からなる高濃度半導体層6Bと、高濃度半導体層6B上のn型InGaAs層からなるバラスト抵抗層7とを有する。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】 半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】 複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。

(もっと読む)

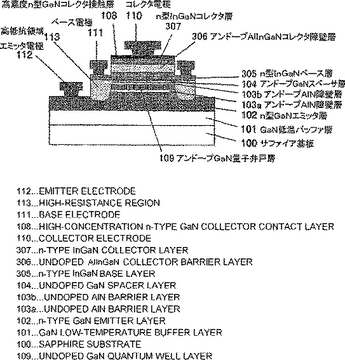

バリスティック半導体素子

本発明のバリスティック半導体素子は、n型のエミッタ層(102)と、n型のInGaNで構成されたベース層(305)と、n型のコレクタ層(307)と、前記エミッタ層(102)及び前記ベース層(305)の間に挟まれ、前記ベース層(305)のバンドギャップより大きいバンドギャップを有するエミッタ障壁層(103)、前記ベース層(305)及び前記コレクタ層(307)の間に挟まれ、前記ベース層(305)のバンドギャップより大きいバンドギャップを有するコレクタ障壁層(306)とを備え、10GHz以上で動作する。  (もっと読む)

(もっと読む)

バイポーラトランジスタとバイポーラトランジスタの製造方法

【課題】 従来のHBTの製造時に、外因性ベース上へのコンタクトホール形成の際の突き抜けを防ぎ、コンタクトホール形成の歩留まりを向上することを目的とする。

【解決手段】 エピタキシャル成長ベース層を有するバイポーラトランジスタであって、外因性ベース層を、化学的に極めて安定なシリコンカーバイド層を含む積層構造とすることにより、ドライエッチングによるコンタクトホール形成時にシリサイドの不完全な部分があったとしても、シリコンカーバイド層によってエッチングの突き抜けを防ぐことができるために、コンタクトホール形成の歩留まりを向上することが可能となる。

(もっと読む)

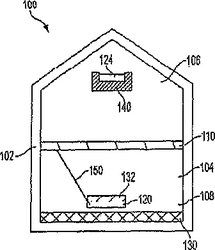

半導体装置及び半導体装置の製造方法

【課題】 バイポーラトランジスタを必要とするプロセスに容易に適合することができる半導体装置の製造方法を用いながら、電極となる半導体膜自体に発生する寄生抵抗の影響を低減し、かつ半導体基板とコンタクト部を形成しない、つまり寄生容量を抑えた半導体装置を提供することを目的とする。

【解決手段】 下部引き出し電極としての半導体膜を開口し、開口窓の底部と側壁に容量膜を形成し、容量膜とシリサイド層126からなるコンタクト部を近接させる構造とすることで、下部引き出し電極になる半導体膜自体の寄生抵抗の影響を低減することができ、かつ、半導体基板とコンタクト部を形成しないので、半導体基板に対する寄生容量を抑えた容量素子を得ることができる。

(もっと読む)

バイポーラトランジスタ及びこのバイポーラトランジスタを有する半導体装置及びこの半導体装置の製造方法

【課題】金属シリサイド層を設けることなくベース抵抗の低減を可能としたバイポーラトランジスタ、及びこのバイポーラトランジスタを有する半導体装置、及びこの半導体装置の製造方法を提供する。

【解決手段】ベース領域の上面にエミッタ領域を設け、絶縁膜で被覆したバイポーラトランジスタ、及びこのバイポーラトランジスタを有する半導体装置、及びこの半導体装置の製造方法において、絶縁膜には、エミッタ領域を囲繞してベース領域に接続した筒状のベース取出電極を設けるようにする。ベース取出電極に接続するベース電極は、エミッタ電極を挟んでコレクタ電極の反対側に設ける。

(もっと読む)

高周波電力増幅用電子部品およびそれを用いた移動体通信システム

【課題】 小型化および低消費電力化を図りつつ負荷変動時のHBTの破壊を有効に防止することのできる高周波電力増幅用電子部品(RFパワーモジュール)および移動体通信システムを提供する。

【解決手段】 高周波電力増幅回路の少なくとも最終段の増幅素子(Q1)がHBT(ヘテロ接合バイポーラ・トランジスタ)で構成されている高周波電力増幅用電子部品おいて、上記HBTとしてそのコレクタ電流−コレクタ電圧特性の非破壊領域と破壊領域との境界が逆S字カーブを有し、該逆S字カーブの極小値が当該高周波電力増幅用電子部品(RFパワーモジュール100)に接続される電源(200)の実使用時に想定される電圧の最大値の4倍以上の領域に存在するHBTを用いるようにした。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】バイポーラトランジスタにおいてベース抵抗の増大を伴うことなく寄生容量を低減し、もって高周波特性を改善する。

【解決手段】n型GaN層2上にSiO2マスク3がストライプ状に開口部を有する形で形成され、前記n型GaN層2上に選択的にn型AlGaNエミッタ層4が形成され、前記n型AlGaNエミッタ層4上にp型GaNベース層5が形成され、同時に横方向成長により前記SiO2マスク3上にもp型GaNベース層5が形成されている。このような構成とすることにより、ベース・コレクタ接合容量CBCおよびベース・エミッタ接合容量CBEが大幅に低減され、バイポーラトランジスタの高周波特性を向上させることが可能となる。

(もっと読む)

ヘテロ接合半導体装置及びその製造方法

【課題】 積層方向における電極位置の高低差を緩和或いは解消し、かつ、製造工程の増加や生産性の低下を抑え、また、電気的特性の悪化を招くことのない構造を有するヘテロ接合半導体装置及びその製造方法を提供すること。

【解決手段】 半絶縁性基板1の上にエピタキシャル成長法によって、サブコレクタ構成材料層2、コレクタ構成材料層3、ベース構成材料層4、エミッタ構成材料層5、そしてエミッタキャップ構成材料層6を形成する。次に、イオン注入法によって、n+型の導電領域21を形成する。この後、エミッタキャップ構成材料層6、エミッタ構成材料層5、ベース構成材料層4およびコレクタ構成材料層3をメサ構造にパターニングして活性層を形成し、エミッタキャップ層16に接してエミッタ電極9を設け、ベース層14に接してベース電極8を設け、活性層以外に残存させた構成材料層のエミッタキャップ構成材料層6の上にコレクタ電極7を設ける。

(もっと読む)

p型窒化物半導体構造及びバイポーラトランジスタ

本発明は、加工ダメージのあるp型窒化物半導体上にInを含むp型窒化物半導体を再成長することにより、加工ダメージが修復され、オーミック特性が大幅に改善されたp型窒化物半導体構造を提供すること、また、電流利得および立ち上がり電圧を大幅に改善することができるp型窒化物半導体バイポーラトランジスタを提供することである。エッチングによる加工を施したp型窒化物半導体(2)上に、Inを含むp型窒化物半導体層(8)を設ける。また、ベース層がp型窒化物半導体であるバイポーラトランジスタにおいて、エミッタ層(1)をエッチングすることにより露出されたp型InGaNベース層(2)の表面に、再成長させたInを含むp型InGaNベース層(8)を設ける。  (もっと読む)

(もっと読む)

ヘテロ接合型バイポーラ半導体装置及びその製造方法

【課題】 ベースコンタクトを安定して形成し、高周波特性等の特性の向上を図ることができる、ヘテロ接合型バイポーラ半導体装置及びその製造方法を提供すること。

【解決手段】 コレクタ層3、ベース層4及びエミッタ層5をこの順に積層してなるヘテロ接合型バイポーラ半導体装置20aにおいて、ベース層4を外部と接続するためのベースオーミックコンタクト部13が拡散係数の小さい炭素等のイオン注入によって形成され、このイオン注入領域がベース層4の設定された途中深さまで高濃度に形成され、RTA処理で低抵抗化されている、ヘテロ接合型バイポーラ半導体装置(HBT)20a。

(もっと読む)

ヘテロ接合バイポーラトランジスタ及びその製造方法

【課題】 本発明は、上述の点に鑑み、断面T字型エミッタ電極の微細化を可能にし、且つ高精度の製造を可能にしたヘテロ接合バイポーラトランジスタ及びその製造方法を提供するものである。

【解決手段】 本発明のヘテロ接合バイポーラトランジスタ1は、コレクタ層2、ベース層3、エミッタ層4及びエミッタキャップ層5を積層し、エミッタキャップ層5のメサ7端部にほぼ一致する断面T字型のエミッタ電極12bを有することを特徴とする。

(もっと読む)

ダイオードとその製造方法、半導体装置

【課題】 少ない工数で耐圧を任意に調整できるダイオード、特に保護ダイオードを提供する。また、この保護ダイオードとバイポーラトランジスタを備えた半導体装置を提供する。

【解決手段】 ダイオードは、接合を形成する一方の半導体層となるエピタキシャル成長された第1導電型の第1半導体層に、第1導電型の不純物が追加して導入されて成る。

このダイオードをバイポーラトランジスタの保護ダイオードに用いて半導体装置を構成する。

(もっと読む)

半導体装置及びその製造方法、並びに半導体モジュール

【課題】 能動素子、受動素子、配線、及び電極からなる半導体装置において、機械的強度の確保、小型化、及び熱的安定性を満たすことの出来る半導体装置を提供することにある。

【解決手段】 半導体装置において、能動素子直下の開口の位置に開口を充填するための導体層を有し、開口のない位置にも導体層を形成する。

(もっと読む)

窒化ガリウム結晶、ホモエピタキシャル窒化ガリウムを基材とするデバイス、及びその製造方法

約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板上に配設された1以上のエピタキシャル半導体層を含むデバイス。かかる電子デバイスは、発光ダイオード(LED)及びレーザーダイオード(LD)用途のような照明用途、並びにGaNを基材とするトランジスター、整流器、サイリスター及びカスコードスイッチなどのデバイスの形態を有し得る。また、約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板を形成し、該基板上に1以上の半導体層をホモエピタキシャルに形成する方法及び電子デバイスも提供される。  (もっと読む)

(もっと読む)

121 - 140 / 155

[ Back to top ]