Fターム[5F003BH08]の内容

バイポーラトランジスタ (11,930) | 電極、配線 (1,046) | 電極材料 (587) | 多層構造 (155)

Fターム[5F003BH08]に分類される特許

21 - 40 / 155

半導体装置及び半導体装置の製造方法

【課題】エミッタ電極の膜厚が均一であり、このために素子特性のばらつきが少ない特性が良好な半導体装置を提供する。

【解決手段】Si基板1上のN−hill層11と、N−hill層11を囲む素子分離領域であるシャロートレンチアイソレーション6に開口されたオープン領域21と、を備えたHCBT100を含む半導体装置において、オープン領域21上に面方位のないアモルファスSi膜30,31を形成する。アモルファスシリコン膜30、31を、N−hill層11がアモルファスシリコン膜30、31から露出する厚みにまでエッチングして電極とする。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波帯域で動作する半導体装置の特性の低下を抑制しつつ、製造コストを低減できる半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置100は、電界効果型トランジスタと、ヘテロ接合バイポーラトランジスタと、ヘテロ接合バイポーラトランジスタのGaAsベース層7を用いて形成されたベースエピ抵抗素子28と、電界効果型トランジスタのInGaAsチャネル層4を用いて形成された配線部26と、配線部26とベースエピ抵抗素子28とを絶縁する高抵抗化領域27と、配線部26の水平方向の周囲を囲う絶縁性の素子分離領域24とを含む。また、ベースエピ抵抗素子28は、半絶縁性GaAs基板1の主面に垂直な方向から見て、配線部26と交差しているベースエピ抵抗素子領域29を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】電力増幅モジュールの放熱特性を向上させる。

【解決手段】電力増幅モジュールに用いられる電力増幅回路用のLDMOSFET素子が形成された半導体チップにおいて、LDMOSFET素子用の複数のソース領域、複数のドレイン領域および複数のゲート電極39が形成されたLDMOSFET形成領域上に、ソース用バンプ電極BPSを配置する。ソース用バンプ電極BPSは、アルミニウムを主体とするソース用パッドM3S上に、ソース用パッドM3Sよりも厚くかつ銅を主体とするソース用導体層CNDSを介して形成する。ソース用バンプ電極BPSとソース用導体層CNDSの間には樹脂膜は介在していない。

(もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】エミッタ接地直流増幅率のばらつきを低減し、かつ抵抗の増大を防止できる、信頼性に優れるバイポーラトランジスタを得ること。

【解決手段】本発明は、N−型エピ層3aやP−型シリコン基板1aを含む半導体基板、N+型ポリシリコン層21a、タングステン層25、シリサイド層27a、シリサイド層39a、ベース電極36a、エミッタ電極36b及びコレクタ電極36cを少なくとも備える。半導体基板上に形成されたN+型ポリシリコン層21aはシリサイド層27aに覆われる。シリサイド層27a上の形成されたタングステン層25はシリサイド層39aに覆われる。

(もっと読む)

ヘテロ接合バイポーラトランジスタ及びその製造方法

【課題】耐破壊性に優れたヘテロ接合バイポーラトランジスタを提供する。

【解決手段】サブコレクタ層と、第1コレクタ層、第2コレクタ層、第3コレクタ層及び第4コレクタ層を有しサブコレクタ層上に形成されたコレクタ層と、コレクタ層上に形成されたベース層と、ベース層上に形成され、ベース層を構成する半導体よりも大きなバンドギャップを有する半導体から構成されるエミッタ層とを備え、第1コレクタ層は、第2コレクタ層、第3コレクタ層及び第4コレクタ層を構成する半導体と異なる半導体から構成されてサブコレクタ層上に形成され、第4コレクタ層は、第2コレクタ層の不純物濃度よりも低い不純物濃度で第1コレクタ層上に形成され、第2コレクタ層は、サブコレクタ層の不純物濃度よりも低く第3コレクタ層の不純物濃度よりも高い不純物濃度で第4コレクタ層上に形成され、第3コレクタ層は、第2コレクタ層とベース層との間に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】ボンディングパッドの剥がれを防止し、かつボンディングパッド間におけるリーク電流の発生を防止することができる半導体装置及びその製造方法を提供すること。

【解決手段】HBT(ヘテロ構造バイポーラトランジスタ)が構成要素の1つとして集積された半導体装置110は、半絶縁性InP基板11上に、順次、エッチングストップ層12、コレクタコンタクト層13、コレクタ層14、傾斜コレクタ層15、セットバック層16、ベース層17が形成された構成を有し、ベース層17はInGaAsで構成された薄膜であってPを含まず、このベース層17上にSiN23が形成され、SiN23上にボンディングパッド25が形成された構成を有する。

(もっと読む)

トランジスタ素子及びその製造方法並びに発光素子及びディスプレイ

【課題】エミッタ電極−コレクタ電極間において、低電圧で大電流変調を可能とするトランジスタ素子を提供する。また、そうしたトランジスタ素子の製造方法、また、そのトランジスタ素子有する発光素子及びディスプレイを提供する。

【解決手段】エミッタ電極3とコレクタ電極2との間に、半導体層5(5A,5B)とシート状のベース電極4が設けられているトランジスタ素子により、上記課題を解決する。半導体層5は、エミッタ電極3とベース電極4との間及びコレクタ電極2とベース電極4との間に設けられて、それぞれ第2半導体層5B及び第1半導体層5Aを構成し、さらに、ベース電極の厚さが80nm以下であることが好ましい。また、少なくともエミッタ電極とベース電極との間又はコレクタ電極とベース電極との間には、暗電流抑制層が設けられていてもよい。

(もっと読む)

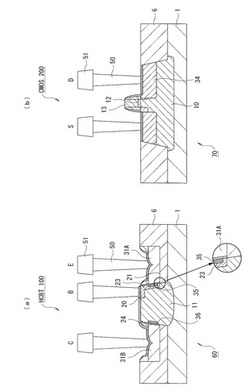

CMOSデバイスの製造方法

【課題】 CMOSデバイスのプロセスで、副産物的に作成できる縦型PNPトランジスタ等のバイポーラトランジスタに有効利用する。

【解決手段】 N―MOSトランジスタは、P型ウエル32−1にドレイン領域37、ソース領域38、及びチャネルストッパー39として形成される。P−MOSトランジスタは、半導体基板31−1の表面に、ドレイン領域40、ソース領域41、及びチャネルストッパー42として形成される。チャネルストッパー42と同時に、すなわち同じ工程で、p型ウェル32−2にはバイポーラトランジスタを形成するベース領域43が形成される。また、P−MOSトランジスタのドレイン/ソース領域40,41と同時に、バイポーラトランジスタのエミッタ領域49及びコレクタ領域の電極取り出し部48が形成される。

(もっと読む)

半導体装置

【課題】 2層の電極構造を有するディスクリート型バイポーラトランジスタでは、2層目のベース電極下方に1層目のエミッタ電極が配置され、2層目のエミッタ電極下方に1層目のベース電極が配置される。このため電極の引き回しによる水平方向の配線抵抗がチップ内で不均一となり、電流容量が大きくできない問題があった。

【解決手段】 1層目の第1エミッタ電極を島状に設け、第1ベース電極をこれらの周りを囲む平板状とする。2層目の第2エミッタ電極は、全ての第1エミッタ電極を覆う平板状に設け、第2ベース電極は第2エミッタ電極の周囲に枠状に設ける。第1エミッタ電極はその直下に設けた第2コンタクトホールを介してエミッタ領域とコンタクトし、直上に設けた第2スルーホールを介して第2エミッタ電極とコンタクトする。これにより電極の引き回しによる水平方向の配線抵抗を均一にできる。

(もっと読む)

半導体装置

【課題】 2層の電極構造を有するディスクリート型バイポーラトランジスタでは、2層目のベース電極下方に1層目のエミッタ電極が配置され、2層目のエミッタ電極下方に1層目のベース電極が配置される。このため電極の引き回しによる水平方向の配線抵抗がチップ内で不均一となり、電流容量が大きくできない問題があった。

【解決手段】 ベース領域を第1コンタクトホールを介して1層目の第1ベース電極と接続させ、第1ベース電極を第1スルーホールまたは第2スルーホールを介して2層目の第2ベース電極16と接続させる。エミッタ領域を第2コンタクトホールを介して1層目の第1エミッタ電極と接続させ、第1エミッタ電極を、第2ベース電極の第2開口部、第3スルーホールを介して、3層目の第2エミッタ電極と接続させる構成とする。これにより各セルの配線抵抗のばらつきを略均一軽減できる。

(もっと読む)

半導体装置

【課題】 2層の電極構造を有するディスクリート型バイポーラトランジスタでは、2層目のベース電極下方に1層目のエミッタ電極およびベース電極が配置される。1層目の電極は2層目の電極よりその厚みが薄く、第2ベース電極下方の動作領域(エミッタ領域)から1層目のエミッタ電極を経由して、2層目のエミッタ電極へ流れる電流経路は、ほぼ真上に電流が引き上げられる第2エミッタ電極下方の電流経路と比べて抵抗が高くなり、チップ内の電流密度が不均一になる問題があった。

【解決手段】 第1ベース電極および第1エミッタ電極を全て短冊状に形成し、交互に平行して配置し、第2エミッタ電極の面積を第2ベース電極の面積より拡張する。これにより、エミッタ領域から第1エミッタ電極を介して第2エミッタ電極まで略真上に引き上げられる電流経路が増加するので、チップ全体の電流密度が不均一になることを回避できる。

(もっと読む)

半導体装置

【課題】2層の電極構造の絶縁膜の厚み分の段差に基づく固着不良を回避したディスクリート型バイポーラトランジスタを提供する。

【解決手段】1層目のエミッタ電極7の上下に設けられるエミッタコンタクトホールCH2とエミッタスルーホールTH2を非重畳とし、1つのエミッタ電極7についてエミッタコンタクトホールCH2とエミッタスルーホールTH2互いに離間して複数配置する。これにより、2層目のエミッタ電極17表面では、最大でも、膜厚が厚い絶縁膜に設けられたエミッタスルーホールTH2の段差の影響しか及ばず、2層目の電極表面の平坦性が向上する。これにより金属プレートの固着不良を回避できる。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】自己発熱および高電流密度動作下においても劣化を生じにくく、高電流密度まで安定して通電可能な高信頼電極を有し、より高い信頼度を達成可能なヘテロ接合バイポーラトランジスタを提供すること。

【解決手段】半導体基板1上に、サブコレクタ層2、コレクタ層3、ベース層4、エミッタ層5およびエミッタコンタクト層6が順次積層されたヘテロ接合バイポーラトランジスタにおいて、エミッタコンタクト層6とエミッタ電極7との間に、Moの融点以上の融点を有する単体金属または合金からなるバリア金属層13−2(図2に示す)を有するバリア複合層13が介在することを特徴とするヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

半導体装置

【課題】SiGe混晶層を有する半導体装置において、高い高周波特性と安定した低いベースコンタクト抵抗とを得られるようにする。

【解決手段】半導体装置は、N型のコレクタ層1aと、コレクタ層1aの上に形成され、P型SiGe層3bを含む真性ベース層となるSiGeエピ膜3と、SiGeエピ膜3の周囲に形成され、P型の多結晶シリコン層及びP型の多結晶シリコンゲルマニウム層を含むベース引き出し電極4と、SiGeエピ膜3の上部に形成されたN型のエミッタ層8とを有している。真性ベース層の上部には、Si−Cap層3cが形成されており、エミッタ層8は、Si−Cap層3cの上部に形成された上部エミッタ領域8bと、該上部エミッタ領域8bの下側に該上部エミッタ領域8bと接して形成された下部エミッタ領域8aとにより構成されている。

(もっと読む)

バイポーラ・トランジスタの浅いベース領域を形成する方法

【課題】バイポーラ・トランジスタの、浅いベース接合形成する方法を提供する。

【解決手段】第1の型のドーパントでドープされた第1の材料層の上に第1の絶縁層205を形成し、第一の絶縁膜205の厚さを、目標ドーパント・プロファイルに基づいて修正し、ベース不純物を、第1の絶縁層205の修正された厚さ、および目標ドーパント・プロフィルに基づいて選択されるエネルギーで注入する。パッド酸化物205内での衝突により、注入されたドーパント種をランダム化し、ドーパント・プロファイルの勾配を増大させ、ベース領域240のチヤネル効果を低減することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高周波帯域で動作する半導体装置の特性向上と製造コストの低減とを両立した半導体装置およびその製造方法を提供する。

【解決手段】同一の半絶縁性GaAs基板1上に積層された複数の半導体層を用いて複数の半導体素子が形成された半導体装置100であって、FET領域23を用いて形成されたFETと、FET領域23と隣接するHBT領域22を用いて形成されたHBTと、FET領域23とHBT領域22との間である素子分離領域24に設けられ、FET領域23とHBT領域22とを分離する分離溝25とを備え、分離溝25は、内壁面と該内壁面の端部とに接地電位を有する導電性金属層が形成されることにより、素子分離領域24を通過する素子間リーク電流を抑制する。

(もっと読む)

半導体装置の製造方法

【課題】工程数を増加させることなく高速バイポーラトランジスタと高耐圧バイポーラトランジスタを同一半導体基板上に形成し、高耐圧バイポーラトランジスタを使用する回路の歪特性を低減できる半導体装置の製造方法の提供。

【解決手段】半導体基板101上に、コレクタの一部となる埋込み領域102を、第1、第2のバイポーラトランジスタの形成領域に同一工程で形成し、エピタキシャル層104を形成し、第1の縦型バイポーラトランジスタの形成領域においては、埋込み領域102をベース形成領域の全体に形成し、第2の縦型バイポーラトランジスタの形成領域においては、埋込み領域102をベース形成領域の1箇所に埋込み領域を形成しない領域を有して形成する。第2の縦型バイポーラトランジスタの埋込み領域を形成しない領域では、周囲からの不純物の拡散により、縦方向の拡散拡がり量が連続的に狭くなり、埋込み領域を形成しない領域が形成される。

(もっと読む)

グラフェントランジスタ及び電子機器

【課題】グラフェントランジスタ及び電子機器に関し、グラフェン膜を用いたチャネル層の特性を各場所で最適化することにより、グラフェントランジスタの性能を向上する。

【解決手段】一層以上のグラフェンからなる炭素膜12をキャリアが走行する能動領域とするとともに、前記能動領域を構成する前記炭素膜のキャリアの走行方向に垂直な方向の幅を場所によって変化させる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の消費電力が増加してしまうのを抑制することが可能な半導体装置を提供する。

【解決手段】このパワーMOSFET100(半導体装置)は、シリコン基板1に形成され、不純物が導入された埋込ドレイン層2と、埋込ドレイン層2に到達するようにシリコン基板1に形成されるとともに、その内側面に絶縁膜12が形成された溝部11と、溝部11の下端部からさらに下方に突出するように形成された溝部13と、溝部11および溝部13に埋め込まれた導電性部材14とを備えている。また、埋込ドレイン層2と導電性部材14とが接している。

(もっと読む)

半導体プロセスおよび集積回路

【課題】バイポーラおよびMOS、受動素子を含む集積回路の製造方法において、MOS、受動素子を絶縁膜で覆った後に、バイポーラのベース以降の工程を行うことを特徴とする半導体装置を提供する。

【解決手段】基板にバイポーラ・トランジスタの能動領域及びMOS素子の能動領域41を形成し、能動領域の周りに水平面において絶縁領域81を形成し、MOS素子の能動領域上にMOSゲート領域111、112を形成し、MOSゲート領域及びトランジスタの能動領域41上に絶縁材料層141を形成し、絶縁層141の残りの部分がバイポーラ・トランジスタの能動領域を部分的に覆うように、絶縁層141に開口143を形成することにより、トランジスタの能動領域内にベース領域を画定する。絶縁層141は、MOSゲート領域上に残り、後続の製造工程の間MOSゲート領域を密閉及び保護する。

(もっと読む)

21 - 40 / 155

[ Back to top ]