Fターム[5F003BJ03]の内容

バイポーラトランジスタ (11,930) | 複合 (843) | バイポーラトランジスタの組合せ (219) | PnP相補 (71)

Fターム[5F003BJ03]に分類される特許

1 - 20 / 71

積層電池および積層電池システム

【課題】従来の捲回電池は、電池内部の温度の上昇を抑制することが困難であった。電池内部に冷媒を流したパイプ等を設ければ、電池寸法が大きくなる。更には、従来の電池は電池価格に大きな影響を及ぼす負極の量が多く、電池価格の低減を図ることが困難であった。

【解決手段】正極および負極を筒状外装体の軸方向に積層して、正極もしくは負極の一方の電極の外径を外装体の内径より大きくすることにより、正極もしくは負極を外装体に密に接触させることにより、電極の熱伝達の向上を図り、電池の温度上昇を抑制する。更には、負極規制とすることにより高価な水素吸蔵合金の使用量を減らして、電池価格の低減を図る。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧が確保でき、大きな放電電流を流すことが可能なESD保護特性のすぐれたESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3でPN接合ダイオード35を形成する。P+型埋め込み層3はP+型引き出し層5と一体となりN−型エピタキシャル層4を貫通させアノード電極10と接続される。P+型埋め込み層3等で囲まれたN−型エピタキシャル層4にN+型拡散層7と該N+型拡散層7と接続され、これを取り囲むP+型拡散層6を形成する。N+型拡散層7、P+型拡散層6はカソード電極9に接続される。P+型拡散層6をエミッタ、N−型エピタキシャル層4をベース、P+型引き出し層5等をコレクタとする寄生PNPバイポーラトランジスタ38とPN接合ダイオード35でESD保護素子を構成する。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3で形成するPN接合ダイオード35と、P型拡散層6と接続するP+型埋め込み層3aをエミッタ、N−型エピタキシャル層4をベース、P+型埋め込み層3をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構築する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それを取り囲むN+型拡散層7はカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、その放電電流I1によりP+型埋め込み層3よりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし大きな放電電流I2が流れる。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3からなるPN接合ダイオード35と、P+型拡散層6と繋がるP+型引き出し層5aをエミッタ、N−型エピタキシャル層4をベース、P型半導体基板1をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構成する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それと接続され、取り囲むN+型拡散層7とはカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、そのときの放電電流I1によりP+型引き出し層5aよりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし、大きな放電電流I2が流れる。

(もっと読む)

半導体装置

【課題】保護素子の異なるクランプ電圧を容易に設定して形成できる構造の保護素子を含む半導体装置を提供すること。

【解決手段】回路内部のMOS型半導体装置のゲート酸化膜を保護するための保護素子を含む半導体装置であって、該保護素子は、該MOS型半導体装置とその前段回路との間に接続される横型バイポーラトランジスタであり、該横型バイポーラトランジスタのパンチスルー耐圧をクランプ電圧として利用することを特徴とする、半導体装置。

(もっと読む)

SiCバイポーラ型半導体素子

【課題】キャリア捕獲中心の少ないSiC半導体素子を提供する。

【解決手段】n型またはp型のSiC基板11と、n型またはp型の少なくとも1つのSiCエピタキシャル層12、あるいはn型またはp型の少なくとも1つのイオン注入層14と、を有し、pn接合界面付近および伝導度変調層(ベース層)内を除いた、SiC基板表面付近、SiC基板とSiCエピタキシャル層との界面付近、およびSiCエピタキシャル層の表面付近のうち少なくとも1つの領域100に、炭素注入層、珪素注入層、水素注入層、またはヘリウム注入層を有し、かつ、炭素原子、珪素原子、水素原子、またはヘリウム原子をイオン注入することで導入した格子間炭素原子をアニーリングにより伝導度変調層内へ拡散させるとともに格子間炭素原子と点欠陥とを結合させることで、電気的に活性な点欠陥が低減された領域を伝導度変調層内に有するSiCバイポーラ型半導体素子。

(もっと読む)

半導体集積回路のESD保護回路およびそのESD保護素子

【課題】従来構造に比べて、レイアウト面積の増加を抑え、保護能力の大幅な低下を招くことなく、保持電圧Vhを電源電圧以上の適正な電圧に制御する。

【解決手段】ESD保護素子21は、スナップバック特性を有するスナップバック特性素子としてのSCR素子と、このSCR素子に接続されて、スナップバック開始電圧Vt1を素子電圧分だけ加算すると共に保持電圧Vhを該素子電圧の2倍高くするための電圧加算素子としてのダイオード13とを有して、ダイオード13の素子電圧を調整して、保持電圧Vhを電源電圧Vcc以上で被保護素子の耐電圧以下に調整する。

(もっと読む)

高電圧バイポーラベースESD保護構造

【課題】面積効率の良い高電圧の単極性ESD保護デバイスを提供する。

【解決手段】ESD保護デバイス300は、p型基板303と、基板内に形成され、カソード端子に接続されるn+及びp+コンタクト領域310、312を包含し、第1のpウェル308−1と、基板内に形成され、アノード端子に接続されるp+コンタクト領域311のみを包含する第2の別個のpウェル308−2と、第1及び第2半導体領域を取り囲み且つこれら半導体領域を分離するように基板内に形成された、電気的にフローティングのアイソレーション構造304、306、307−2とを含む。カソード及びアノードの端子に、トリガー電圧レベルを上回る正電圧が印加されると、ESD保護デバイスは、構造を通り抜ける低インピーダンス経路を提供してESD電流を放電するよう、内在サイリスタをスナップバックモードに入らせる。

(もっと読む)

半導体装置

【課題】ホールド電圧を変化させずに、トリガー電圧のみを調節することができるようにする。

【解決手段】本実施形態における保護素子10は、低濃度コレクタ層102、シンカー層110、高濃度コレクタ層112、エミッタ層130、高濃度ベース層122、ベース層120、第1導電型層140、及び第2導電型層150を有している。第2導電型層150は低濃度コレクタ層102に形成されており、ベース層120と第1導電型層140の間に位置している。第2導電型層150は低濃度コレクタ層102よりも不純物濃度が高い。

(もっと読む)

エピレス基板における分離型の相補型MOS装置

【課題】高い実装密度を得ることが可能な半導体装置の製造プロセスを提供する。

【解決手段】半導体装置を電気的に分離するための構造は、エピタキシャル層を含まない半導体基板240内にドーパントを打込むことにより形成される。この打込みに続き、極めて限られた熱収支に上記構造を晒すことでドーパントが顕著に拡散しないようにする。その結果として、上記分離構造の寸法が制限かつ規定され、こうして、エピタキシャル層を成長させる工程とドーパントを拡散させる工程とを含む従来のプロセスを用いて得られるよりも高い実装密度を得ることができる。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】室温(300K)以上において正孔濃度が1.0×1015cm‐3以上で、かつ、ドーパント原子濃度が1.0×1021cm‐3以下である実用的なp型ダイヤモンド半導体デバイスとその製造方法を提供すること。

【解決手段】単結晶ダイヤモンド基板1−1の上に形成された単結晶ダイヤモンド薄膜1−2の中には、二次元の正孔または電子チャンネル1−3が形成される。基板1−1の面方位と基板1−1の結晶軸「001」方向との成す角度をαs、ダイヤモンド薄膜1−2の面方位と単結晶ダイヤモンド薄膜1−2の結晶軸「001」方向との成す角度をαd、チャンネル1−3の面方位とダイヤモンド薄膜1−2の結晶軸「001」方向との成す角度をαcとする。単結晶ダイヤモンド薄膜1−2の表面上には、ソース電極1−4、ゲート電極1−5、ドレイン電極1−6が形成される。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】最大発振周波数fmaxを高くしてダイヤモンド電界効果トランジスタの特性を大きく向上させ、かつ電圧降下を小さく抑えることにより実用レベルに到達させること。

【解決手段】「ソース・ゲート電極間隔dSG、ゲート・ドレイン電極間隔dGDを狭くすること」と「ソース電極の厚さtS、ドレイン電極の厚さtDを厚くすること」とを両立させるために、ソース電極およびドレイン電極を、エッチング溶液を用いてエッチングする層とレジストを用いてリフトオフする層とに分けて形成する。これにより電極の逆メサ部を小さくすることができるため、ソース電極とゲート電極との間隔を小さくして最大発振周波数fmaxを上げ、かつソース電極およびドレイン電極の厚みを厚くして電圧降下を小さく抑えることができる。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】ダイヤモンド薄膜内に存在する結晶欠陥、不純物等を減少させ、高品質なダイヤモンド薄膜を作製可能なダイヤモンド薄膜作製方法を提供すること。

【解決手段】ダイヤモンドが安定な高圧力下でアニールを行う。これにより、結晶中に含まれる格子欠陥等が回復、除去され、ダイヤモンド結晶薄膜を高品質化する事ができる。「(ダイヤモンドが)安定な、安定に」とは、ダイヤモンドがグラファイト化せずにダイヤモンドの状態を保つ状態を指す。ダイヤモンドが安定にアニール出来る領域内でアニールを行う温度(アニール温度、とも呼ぶ)Tおよびアニールを行う圧力(アニール圧力、とも呼ぶ)Pが決定される。この領域は、図21に示される、P>0.71+0.0027TまたはP=0.71+0.0027Tを満たし、なおかつP≧1.5GPaの領域である。このような領域は、図21中の斜線部分である。

(もっと読む)

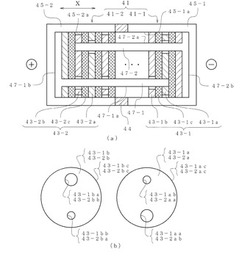

トレンチにより制限された分離拡散領域を備えた相補型アナログバイポーラトランジスタ

【課題】表面上に素子をより高密度に実装する。

【解決手段】第1のトレンチと第2のトレンチとの間の位置において、エピタキシャル層の表面から基板へと下方に延在するドーパントのウェルは、エピタキシャル層の背景ドーピング濃度とは異なるドーピング濃度を有し、エピタキシャル層の残りの部分と第1および第2の接合を形成する。第1の接合は、第1のトレンチの底部から基板に延在し、第2の接合は、第2のトレンチの底部から前記基板に延在する。ウェルおよび第1および第2のトレンチは分離構造を構成し、分離構造は、分離構造の一方側のエピタキシャル層に形成された第1の素子と分離構造の他方側のエピタキシャル層に形成された第2の素子とを電気的に分離する。分離構造による電気的分離は第1および第2のトレンチとPN接合とによってもたらされ、ウェルは第1の導電型の材料でドープされ、基板およびエピタキシャル層は、第1の導電型とは反対の第2の導電型の材料でドープされ、第1および第2の接合はPN接合である。

(もっと読む)

静電気保護用半導体装置

【課題】 半導体集積回路をESDの過電流ノイズ及びラッチアップ試験の過電流ノイズから保護する保護回路であって、電源端子から保護素子への配線の配置の自由度を高めることができ、チップ面積の増大とはならない、保護回路を提供する。

【解決手段】 ラッチアップ試験の過電流ノイズから保護するバイポーラトランジスタ12のベース接地電流増幅率を0.5〜1.0になるような構造とすることで、I/O端子10から入ったラッチアップ試験の過電流ノイズは、バイポーラトランジスタ12を通り接地端子11へ流れるので、電源端子9からバイポーラトランジスタ12のベースへの配線を細くすることが可能となり、配線配置の自由度が高まる。

(もっと読む)

半導体基板、半導体基板の製造方法、および電子デバイス

【課題】単一半導体基板上にHBTおよびFETのような異なる種類の複数デバイスを形成するに適した化合物半導体基板を提供する。

【解決手段】第1半導体110と、第1半導体上に形成された、電子捕獲中心または正孔捕獲中心を有するキャリアトラップ層130と、キャリアトラップ層上にエピタキシャル成長され、自由電子または自由正孔が移動するチャネルとして機能する第2半導体144と、第2半導体上にエピタキシャル成長したN型半導体/P型半導体/N型半導体で表される積層体、または前記第2半導体上にエピタキシャル成長したP型半導体/N型半導体/P型半導体で表される積層体を含む第3半導体160とを備える半導体基板。

(もっと読む)

パワー半導体素子

【課題】小電流領域から大電流領域までの広範な負荷電流の電流値において、従来例に比較して、電力の変換効率を向上させることが可能なパワー半導体装置を提供する。

【解決手段】本発明のパワー半導体素子は、第1ゲート電極によりスイッチングの制御が行われるパワー半導体素子であり、IGBT動作とMOSトランジスタ動作との切替を行う第2ゲートを有し、第1ゲート電極により、スイッチング動作をさせる際、負荷に流れる負荷電流の電流値に応じて、第2ゲート電極に対して制御信号を印加し、MOSトランジスタにて動作させるか、またはバイポーラトランジスタとして動作させるかのいずれかを選択する。

(もっと読む)

半導体デバイス、半導体基板に分離されたポケットを形成する方法、半導体構成、PNPトランジスタ、横型NチャネルDMOSトランジスタ、横型トレンチDMOSトランジスタ

【課題】モジュール化された、相互作用しないやり方で、単一の半導体ウェハにともに接近して実装され、十分に分離された、最適化されたトランジスタまたは他のデバイスの任意の集合の作製を可能にする。

【解決手段】

一群の半導体デバイスが、エピタキシャル層を含まない基板に形成される。一実施例では、この一群は、5VのCMOSペア、12VのCMOSペア、5VのNPN、5VのPNP、いくつかの形状の横型トレンチMOSFET、および30V横型N−チャネルDMOSを含む。これらのデバイスの各々は、横方向かつ縦方向の双方において極めて小型であり、基板の他のすべてのデバイスから十分に分離され得る。

(もっと読む)

半導体装置

【課題】製造後に電流増幅率hFE特性を変化させることができるバイポーラトランジスタを備えた半導体装置を提供する。

【解決手段】P型半導体層1に、N型拡散層からなるコレクタ3、P型拡散層からなるベース5、N電型拡散層からなるエミッタ7が形成されてバイポーラトランジスタが形成されている。そのバイポーラトランジスタはベース5上及びコレクタ3にゲート絶縁膜9を介してゲート電極11を備えている。コレクタ3にはコレクタ配線13が接続されている。ベース5にはベース配線15が接続されている。エミッタ7にはエミッタ配線17が接続されている。ゲート電極11にはゲート電極配線19が接続されている。配線13,15,17,19は互いに電気的に絶縁されている。

(もっと読む)

半導体装置及びその製造方法

【課題】バイポーラトランジスタの高速化に伴うMOSトランジスタの分離特性の低下を抑制する半導体装置を提供する。

【解決手段】半導体装置1000aは、第一導電型のバイポーラトランジスタ100及びMOSトランジスタ200を備え、MOSトランジスタ200は、第二導電型の半導体基板1と半導体基板1上に形成された第一導電型のエピタキシャル層2との界面付近に形成された、半導体基板1上面から第一の深さに不純物濃度のピークを持つ第一導電型埋込層16と、第一導電型埋込層16上に形成された第二導電型埋込層17及びウェル層18と、第二導電型ウェル層18に形成された第一導電型のソース層19及びドレイン層20と、第一の深さより浅い第二の深さに不純物濃度のピークを持つ第一導電型埋込層27とを有し、第一導電型埋込層27は、第一導電型埋込層16と接し、かつ、第二導電型埋込層17の外縁部を囲むように形成されている。

(もっと読む)

1 - 20 / 71

[ Back to top ]