Fターム[5F003BM03]の内容

バイポーラトランジスタ (11,930) | 構成材料 (828) | 3−5族 (514) | 三元以上 (275)

Fターム[5F003BM03]に分類される特許

261 - 275 / 275

高オン耐圧ヘテロ接合バイポーラトランジスタ

【課題】HBTのオン耐圧を高めることで、HBTの出力特性及び大きなインピーダンス不整合(高VSWR)に耐えるHBTの能力を向上させた、優れたオン耐圧VCEを備えたヘテロ接合バイポーラトランジスタ(HBT)を提供する。

【解決手段】HBTのコレクタ領域を構成するコレクタ層とサブコレクタ層との接合部近辺における高電界を抑制することによって、オン耐圧を向上させる。

(もっと読む)

(もっと読む)

メタモルフィック半導体装置

【課題】 非格子整合半導体素子を有する半導体装置において、半導体素子におけるメタモルフィックバッファ層による大きな段差の発生による段切れ等の改善を図る。

【解決手段】 基体1上のメタモルフィックバッファ層20を、素子間分離溝41を挟んで半導体素子の形成部の外側に、メタモルフィックバッファ層20の延在領域20Rを形成して、半導体素子部と、これに隣接する他部との実質的段差の緩和を図って、この段差に基づく絶縁層、配線等の信頼性の向上を図るものである。

(もっと読む)

バイポーラトランジスタとその製造方法

【課題】 ベース電極がエアブリッジ構造を有するバイポーラトランジスタにおいて、構造の簡潔化、ベース電極に対する外部配線としてのベース配線のコンタクト位置の自由度を高めることができるようにする。

【解決手段】 ベース層13の少なくとも一部が上面に臨んで形成された半導体メサ部BMを有し、そのベース層13にコンタクトされたベース電極15が、半導体メサ部BMより外側の空間に浮上延長する浮上延長部15Fを有し、この延長浮上部15Fをベース電極13に対するベース配線42のコンタクト部15Cとする。このようにして、コンタクト部を固定部に設ける場合におけるこの固定部を形成するための構造、製造の煩雑さを回避でき、かつベース電極に対するベース配線のコンタクト部の選定の自由度をたかめ、レイアウト等の設計の自由度を高めるものである。

(もっと読む)

半導体素子

【課題】 作製が容易で広い温度範囲で高速動作するホットエレクトロントランジスタを提供すること

【解決手段】 窒化物系半導体から構成されたコレクタ層107、コレクタ障壁層106、ベース層105、アンドープ第1エミッタ障壁層115およびエミッタ層102を順に備えた半導体素子であって、コレクタ層107、ベース層105およびエミッタ層102は、それぞれ、n型半導体から構成されており、第1エミッタ障壁層115は、エミッタ層102とベース層105との間に配置されており、第1エミッタ障壁層115のバンドギャップは、エミッタ層102のバンドギャップよりも大きく、第1エミッタ障壁層115に接してベース電極111が形成されている半導体素子。

(もっと読む)

ヘテロ接合バイポーラトランジスタの製造方法

【課題】GaAsベース/InGaPエミッタ界面において、遷移層(InGaPAsからなる層)の形成を防止するために流すH2ガスフローがベース層の表面を傷めるのを防止して、HBT特性である電流利得βを向上させるヘテロ接合バイポーラトランジスタの製造方法を提供すること。

【解決手段】ヘテロ接合バイポーラトランジスタを製造するに際し、GaAsからなるベース層4を成長した後、AsH3ガスをフローし、次にH2ガスをフローし、その後にInGaPからなるエミッタ層5をエピタキシャル成長することを特徴とする。

(もっと読む)

半導体複合基板及びそれを用いた化合物半導体素子

【課題】 4H−SiC基板上に高品質のGaN系化合物半導体がエピタキシャル成長された半導体複合基板を提供する。

【解決手段】 半導体複合基板1は、SiC単結晶基板101の主表面上にAl1−xGaxN(0≦x≦1)エピタキシャル成長層100が直接形成されている。SiC単結晶基板101は4H−SiC単結晶基板であり、Al1−xGaxNエピタキシャル成長層の厚さが少なくとも4μmである。

(もっと読む)

半導体構造(調整可能半導体デバイス)

【課題】下方に配置された基板とは異なる極性を有する不連続な非平面状サブコレクタを含む半導体構造を形成する方法を提供する。

【解決手段】この構造は、サブコレクタの上方の活性領域(コレクタ)、活性領域の上方のベース、およびベースの上方のエミッタを含む。不連続なサブコレクタの不連続部分間の距離は、半導体構造の動作特性を調整する。調整可能な動作特性は、絶縁破壊電圧、電流利得遮断周波数、電力利得遮断周波数、通過周波数、電流密度、静電容量範囲、ノイズ注入、少数キャリヤ注入、ならびにトリガ電圧および保持電圧を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 小型化を図ることができる半導体装置を提供する。また、放熱効率を向上させた半導体装置を提供する。

【解決手段】 配線基板10の裏面にGND用外部配線12を形成する。そして、このGND用外部配線12に接続する複数のビア18を、配線基板10を貫通するように形成し、配線基板10の主面にHBTを含む高消費電力の第1の半導体チップ19を実装する。第1の半導体チップ19のエミッタバンプ電極19bは、第1の半導体チップ19内に形成された複数のHBTのエミッタ電極に共通接続しており、HBTが並んだ方向に延在している。第1の半導体チップ19は、この延在したエミッタバンプ電極19bに複数のビア18が接続するように配線基板10に実装されている。また、第1の半導体チップ19上に第1の半導体チップ19より発熱量の少ない第2の半導体チップ21を搭載して配線基板10の小型化を図る。

(もっと読む)

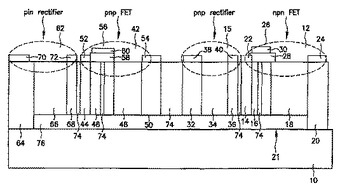

コンプリメンタリ横型窒化物トランジスタ

基板の支持表面上に形成された、横方向に隣接した導電性半導体領域により構成された横方向に延びているスタックを備える半導体デバイスおよびそのデバイスを作製する方法。  (もっと読む)

(もっと読む)

バイポーラ接合トランジスタジオメトリ

【課題】

【解決手段】 バイポーラ接合トランジスタ(100)に関連する方法、装置、デバイスの実施例が記載されている。

(もっと読む)

ひずみ印加半導体デバイス

多数キャリアが正孔であるトランジスタにおいて、少なくとも1つの狭いバンドギャップの領域または層が、p型にドーピングされるかまたは過剰の正孔を含み、かつ機械的圧縮ひずみを受け、これによって、正孔の移動度がかなり増大し得る。pチャネル量子井戸FETでは、量子井戸のInSb井戸のp型層5(変調ドーピングまたは直接ドーピングされている)が、In1−xAlxSb層4と、In1−xAlxSb層6との間にあるが、ここで、xは、軽い正孔および重い正孔が、kTをはるかに超える量だけ分離されるような範囲にまで、層5中にひずみを導入するに十分な値である。pnpバイポーラデバイスを含む、本発明の範囲内にあるトランジスタは、相補型論理回路における電子が多数キャリアである従来の等価物と一緒に用いられ得る。  (もっと読む)

(もっと読む)

増大した線形性および製造可能性を有するFETを含むBiFET

例示的一実施例によれば、基板上に位置するBiFETは、基板の上に位置するエミッタ層部分を含み、エミッタ層部分は第1のタイプの半導体を含む。HBTはエッチストップ層の第1の部分をさらに含み、エッチストップ層の第1の部分はInGaPを含む。BiFETは基板の上に位置するFETをさらに含み、FETはソース領域およびドレイン領域を含み、エッチストップ層の第2の部分はソース領域およびドレイン領域の下に位置し、エッチストップ層の第2の部分はInGaPを含む。FETはエッチストップ層の第2の部分の下に位置する第2のタイプの半導体層をさらに含む。エッチストップ層はFETの線形性を増大させ、HBTの電子の流れを低下させない。  (もっと読む)

(もっと読む)

半導体部品および半導体部品の製造方法

半導体部品は、半導体基板(110)と、半導体基板の上方のエピタキシャル半導体層(120)と、エピタキシャル半導体層内のバイポーラトランジスタ(770、870)と、エピタキシャル半導体層内の電界効果トランジスタ(780、880)とを含む。エピタキシャル半導体層の一部によって、バイポーラトランジスタのベースと電界効果トランジスタのゲートとが形成され、エピタキシャル半導体層のその一部は実質的に均一なドーピング濃度を有する。同じまたは他の実施形態においては、エピタキシャル半導体層の異なる部分によって、バイポーラトランジスタのエミッタと電界効果トランジスタのチャネルとが形成され、エピタキシャル半導体層のその異なる部分はエピタキシャル半導体層の一部の実質的に均一なドーピング濃度と同じかまたは異なる実質的に均一なドーピング濃度を有する。  (もっと読む)

(もっと読む)

半導体素子及び方法

【課題】既に達した速度を潜在的に越えることさえできる極めて高速で動作できるバイポーラトランジスタとその方法を提供することである。

【解決手段】バイポーラトランジスタから制御可能な光放射を生成する方法及び素子が開示されている。また、以下の工程、つまりエミッタ、ベース、及びコレクタ領域を有するバイポーラトランジスタを提供し、電気信号とエミッタ、ベース、及びコレクタ領域を結合する電極を提供し、及び自然放射の不利益に対して誘導放射を強化するためにベース領域を適合させ、それによりベース領域のキャリア再結合寿命を削減する工程を含むバイポーラトランジスタの速度を増大させる方法も開示されている。

(もっと読む)

HBTの製造方法

【課題】 オーバエッチングがべ一ス層まで及ぶことがなく、高速化を図ったHBTの製造方法を提供する。

【解決手段】 コレクタ層とベース層が同じエッチング液でエッチングされる材質で形成されている場合において、

を含んでいる。

(もっと読む)

261 - 275 / 275

[ Back to top ]