Fターム[5F003BP23]の内容

バイポーラトランジスタ (11,930) | 製法 (1,830) | イオン注入 (274) | ドーピング物質 (42)

Fターム[5F003BP23]に分類される特許

1 - 20 / 42

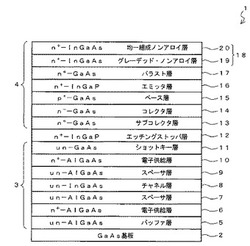

トランジスタ用エピタキシャルウェハの製造方法

【課題】成長時間を短縮してスループットを向上することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】基板2上に、電子供給層6,10及びチャネル層8を有する高電子移動度トランジスタ構造層3を形成する工程と、高電子移動度トランジスタ構造層3上に、コレクタ層14、ベース層15、エミッタ層16及びノンアロイ層18を有するヘテロバイポーラトランジスタ構造層4を形成する工程と、を有するトランジスタ用エピタキシャルウェハの製造方法において、ヘテロバイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下で、かつ、一定の成長温度で成長するようにした。

(もっと読む)

SiCバイポーラ型半導体素子

【課題】キャリア捕獲中心の少ないSiC半導体素子を提供する。

【解決手段】n型またはp型のSiC基板11と、n型またはp型の少なくとも1つのSiCエピタキシャル層12、あるいはn型またはp型の少なくとも1つのイオン注入層14と、を有し、pn接合界面付近および伝導度変調層(ベース層)内を除いた、SiC基板表面付近、SiC基板とSiCエピタキシャル層との界面付近、およびSiCエピタキシャル層の表面付近のうち少なくとも1つの領域100に、炭素注入層、珪素注入層、水素注入層、またはヘリウム注入層を有し、かつ、炭素原子、珪素原子、水素原子、またはヘリウム原子をイオン注入することで導入した格子間炭素原子をアニーリングにより伝導度変調層内へ拡散させるとともに格子間炭素原子と点欠陥とを結合させることで、電気的に活性な点欠陥が低減された領域を伝導度変調層内に有するSiCバイポーラ型半導体素子。

(もっと読む)

炭化珪素半導体装置

【課題】エミッタ層からコレクタ層を経由してベース層へ移動する電荷の移動を阻止し、エミッタ層からコレクタ層を経由してベース層に注入される電荷を無くすことで、コレクタ層における欠陥の成長を防止することが可能な炭化珪素半導体装置を提供する。

【解決手段】本発明の炭化珪素半導体装置は、炭化珪素半導体基板により構成された炭化珪素半導体装置であり、第1の導電型のコレクタ層102と、コレクタ層の上部に設けられた第2の導電型のベース層104と、ベース層の一部として設けられたベース電極105と、ベース層上に設けられベース電極と離間して設けられたエミッタ層107と、ベース電極からエミッタ層に対して移動する電荷の経路において、コレクタ層内に設けられた、コレクタ層内における電荷の経路を遮断する絶縁体層112とを有する。

(もっと読む)

バイポーラ半導体素子

【課題】高温や電流密度が高い条件下でも基板へ少数キャリアが到達するのを防いで、順方向電圧の増大を防ぐことができるバイポーラ半導体素子を提供する。

【解決手段】このSiC pinダイオード20では、n型SiC基板21とn型のドリフト層23との間に形成されている厚さを20μmとしたn型のバッファ層22が、p型のアノード層24,25からの正孔のトラップとして働いて、正孔(少数キャリア)がn型SiC基板21へ到達することを防ぐ。これにより、正孔(少数キャリア)がn型SiC基板21へ到達することを防いで、n型SiC基板21から積層欠陥が拡大するのを防いで、順方向電圧の増大を防止できる。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】イオン注入したダイヤモンドの高温高圧アニールにより起こるダイヤモンド表面のエッチングを防ぎ、従来の方法では得られない高品質P型、N型ダイヤモンド半導体を得るダイヤモンド半導体の作製方法を提供すること。

【解決手段】ダイヤモンド基板5−11を用意し、そのダイヤモンド基板5−11上にマイクロ波プラズマCVD装置を用い、メタンを反応ガスとして基板温度700℃でダイヤモンド薄膜5−12を1μm積層する。上記ダイヤモンド薄膜5−12にイオン注入装置を用い、加速電圧60kV、ドーズ量1×1014cm−2でドーパントを打ち込む。その後、イオン注入ダイヤモンド薄膜5−13上に保護層(白金)5−14を形成する。表面に保護層5−14が形成されたイオン注入ダイヤモンド薄膜5−13を、超高温高圧焼成炉内に配置し、3.5GPa以上、600℃以上の圧力、温度下でアニールする。

(もっと読む)

トレンチにより制限された分離拡散領域を備えた相補型アナログバイポーラトランジスタ

【課題】表面上に素子をより高密度に実装する。

【解決手段】第1のトレンチと第2のトレンチとの間の位置において、エピタキシャル層の表面から基板へと下方に延在するドーパントのウェルは、エピタキシャル層の背景ドーピング濃度とは異なるドーピング濃度を有し、エピタキシャル層の残りの部分と第1および第2の接合を形成する。第1の接合は、第1のトレンチの底部から基板に延在し、第2の接合は、第2のトレンチの底部から前記基板に延在する。ウェルおよび第1および第2のトレンチは分離構造を構成し、分離構造は、分離構造の一方側のエピタキシャル層に形成された第1の素子と分離構造の他方側のエピタキシャル層に形成された第2の素子とを電気的に分離する。分離構造による電気的分離は第1および第2のトレンチとPN接合とによってもたらされ、ウェルは第1の導電型の材料でドープされ、基板およびエピタキシャル層は、第1の導電型とは反対の第2の導電型の材料でドープされ、第1および第2の接合はPN接合である。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSプロセスへの導入が容易で、エミッタ−ベース間のリーク電流(電界強度)を低減し、ノイズやサージ電圧の影響を受けにくい高性能な半導体装置とその製造方法の提供。

【解決手段】導電膜をマスクとして、2回のイオン注入を行ってエミッタを形成する。第2エミッタ領域111bは、低濃度の不純物イオン注入によって形成し、第1エミッタ領域111aは、高濃度の不純物イオン注入によって形成する。その結果、エミッタの周縁部に低濃度の第2エミッタ領域が形成され、電界が緩和され、リーク電流が低減する。また、導電膜とエミッタ電極116とが接続され、ノイズの影響を受けにくくなる。

(もっと読む)

バイポーラ半導体素子

【課題】高温や電流密度が高い条件下でも基板へ少数キャリアが到達するのを防いで、順方向電圧の増大を防ぐことができるバイポーラ半導体素子を提供する。

【解決手段】このSiC pinダイオード20では、n型SiC基板21とn型バッファ層22との間に形成したn型少数キャリア消滅層31は、n型バッファ層22よりも炭素空孔欠陥の濃度が高く、少数キャリア消滅層31の炭素空孔欠陥はp型のアノード層24,25からの正孔のトラップとして働く。よって、小数キャリア消滅層31に達した正孔(少数キャリア)がトラップされ、小数キャリア消滅層31において正孔密度K2が急激に減衰する。これにより、正孔(少数キャリア)が基板21へ到達することを防いで、基板21から積層欠陥が拡大するのを防いで、順方向電圧の増大を防止できる。

(もっと読む)

SiC結晶成長層の製造方法およびバイポーラ型半導体素子

【課題】層厚さが厚くてもSiC結晶中にある炭素空孔を低減できるSiC結晶成長層の製造方法を提供する。

【解決手段】SiC結晶成長層としてのドリフト層23を成長させる工程内に、シリコン原料ガスであるシランと炭素原料ガスであるプロパンのうちのプロパンのみを結晶成長表面に供給する第2の期間を設けている。このことで、結晶成長表面の炭素の過飽和度を上げ、成長途中の表面に過剰な格子間炭素を発生させる。これにより、成長後のSiC結晶成長層としてのドリフト層23の表面から離れている比較的深い箇所での炭素空孔を減少させることができる。

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製法

【課題】高い電流増幅率を有し、高周波特性および素子寿命に優れたヘテロ接合バイポーラトランジスタおよびその製法を提供すること。

【解決手段】半絶縁性基板1上に、n型半導体より成る真性エミッタ層16と、p型ドーパントを高濃度でドーピングされ、真性エミッタ層16よりも狭いバンドギャップを有する半導体より成るベース層9と、ベース層9と同じ半導体より成るコレクタ層10とを、この順序で積層して成るへテロ接合バイポーラトランジスタにおいて、真性エミッタ層16の周囲に、高抵抗領域15が設けられ、高抵抗領域15と真性エミッタ層16との間に、真性エミッタ層16の半導体と同じ半導体から成るガードリング領域17が設けられ、真性エミッタ層16とベース層9との接合面が、ガードリング領域17の上面よりも下に位置することを特徴とするヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】線形性に優れた半導体抵抗素子を提供する。

【解決手段】本発明の半導体装置は、GaAs基板101上に形成され、3−5族化合物半導体から構成されるHBT130と、GaAs基板101上に形成され、HBT130を構成する半導体エピタキシャル層の少なくとも1層から構成される半導体抵抗素子120とを備え、半導体抵抗素子120は、ヘリウム不純物を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】良好な電流増幅率が得られる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板と、半導体基板上に設けられ、炭化ケイ素から形成される第1導電型の第1伝導層12と、第1伝導層12上に設けられ、第1伝導層12の不純物濃度より低い不純物濃度を有し、炭化ケイ素から形成される第1導電型の第2伝導層14と、第2伝導層14中に設けられ、第1導電型とは異なる導電型の第2導電型のベース領域16と、ベース領域16中に設けられ、表面がベース領域16の表面と同一平面にあると共に、5×1017cm−3以上5×1019cm−3以下の不純物濃度を有する第1導電型のエミッタ領域18とを備える。

(もっと読む)

ヘテロ接合バイポーラトランジスタ及びその製造方法

【課題】耐破壊性に優れたヘテロ接合バイポーラトランジスタを提供する。

【解決手段】サブコレクタ層と、第1コレクタ層、第2コレクタ層、第3コレクタ層及び第4コレクタ層を有しサブコレクタ層上に形成されたコレクタ層と、コレクタ層上に形成されたベース層と、ベース層上に形成され、ベース層を構成する半導体よりも大きなバンドギャップを有する半導体から構成されるエミッタ層とを備え、第1コレクタ層は、第2コレクタ層、第3コレクタ層及び第4コレクタ層を構成する半導体と異なる半導体から構成されてサブコレクタ層上に形成され、第4コレクタ層は、第2コレクタ層の不純物濃度よりも低い不純物濃度で第1コレクタ層上に形成され、第2コレクタ層は、サブコレクタ層の不純物濃度よりも低く第3コレクタ層の不純物濃度よりも高い不純物濃度で第4コレクタ層上に形成され、第3コレクタ層は、第2コレクタ層とベース層との間に形成される。

(もっと読む)

半導体装置

【課題】SiGe混晶層を有する半導体装置において、高い高周波特性と安定した低いベースコンタクト抵抗とを得られるようにする。

【解決手段】半導体装置は、N型のコレクタ層1aと、コレクタ層1aの上に形成され、P型SiGe層3bを含む真性ベース層となるSiGeエピ膜3と、SiGeエピ膜3の周囲に形成され、P型の多結晶シリコン層及びP型の多結晶シリコンゲルマニウム層を含むベース引き出し電極4と、SiGeエピ膜3の上部に形成されたN型のエミッタ層8とを有している。真性ベース層の上部には、Si−Cap層3cが形成されており、エミッタ層8は、Si−Cap層3cの上部に形成された上部エミッタ領域8bと、該上部エミッタ領域8bの下側に該上部エミッタ領域8bと接して形成された下部エミッタ領域8aとにより構成されている。

(もっと読む)

バイポーラ・トランジスタの浅いベース領域を形成する方法

【課題】バイポーラ・トランジスタの、浅いベース接合形成する方法を提供する。

【解決手段】第1の型のドーパントでドープされた第1の材料層の上に第1の絶縁層205を形成し、第一の絶縁膜205の厚さを、目標ドーパント・プロファイルに基づいて修正し、ベース不純物を、第1の絶縁層205の修正された厚さ、および目標ドーパント・プロフィルに基づいて選択されるエネルギーで注入する。パッド酸化物205内での衝突により、注入されたドーパント種をランダム化し、ドーパント・プロファイルの勾配を増大させ、ベース領域240のチヤネル効果を低減することができる。

(もっと読む)

バイポーラ・トランジスタのコレクタ領域をカウンタ・ドープする方法

【課題】バイポーラ・トランジスタのコレクタウエルを形成する方法を提供する。

【解決手段】本方法は、第1の種類のドーパントでシリコン層をドープすること、および第1の注入工程を実施して第1の種類とは反対の第2の種類のドーパントをシリコン層内に注入することを含む。注入されたドーパントは、シリコン層内で第1のドーパント・プロフィル305を有する。本方法はまた、第2の注入工程を実施して第2の種類の追加のドーパントをシリコン層内に注入することを含む。注入された追加のドーパントは、シリコン層内で第1のドーパント・プロフィル310とは異なる第2のドーパント・プロフィル320を有する。本方法は、シリコン層および第1の種類のドーパントの一部分を消費することによって、シリコン層上に形成された絶縁層を成長させることをさらに含む。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】高周波用送信パワーアンプに適用されるヘテロ接合バイポーラトランジスタには、高耐圧性が要求される。

【解決手段】GaAs基板101上から順に、n+型GaAsサブコレクタ層102と、n型GaAsコレクタ層103と、p型GaAsベース層104と、n型InGaPエミッタ層105と、n型GaAsエミッタキャップ層107よりドーピング濃度が低いn型GaAs耐圧調整層106と、n型GaAsエミッタキャップ層107と、n+型InGaAsコンタクト層108とを備える。

(もっと読む)

バイポーラ素子及びその製造方法

【課題】メサ型バイポーラトランジスタあるいはサイリスタでは、エミッタ層あるいはアノード層からベース層あるいはゲート層に注入されたキャリアが横方向に拡散し再結合する結果、小型化やスイッチング周波数の向上が困難であった。

【解決手段】エミッタ層あるいはアノード層を高濃度および低濃度からなる二層で構成し、この低濃度層と同一の不純物密度を有する同一の半導体からなる再結合抑制半導体領域をベース層またはゲート層と表面保護絶縁膜とに接して存在させるとともに、この再結合抑制半導体領域の幅をキャリアの拡散距離以上に設定する。このことにより、バイポーラトランジスタの小型化やサイリスタのスイッチング周波数向上を、性能を損なわず実現できる効果がある。また、上記バイポーラトランジスタの高濃度エミッタ層上に、正孔バリア層、伝導帯不連続緩和層、及びエミッタコンタクト層を順次積層することにより、電流増幅率を大幅に向上できる効果がある。

(もっと読む)

pn接合を有する薄膜結晶ウエハ及びその製造方法

【課題】 HBTのエミッタ層とエミッタキャップ層とのヘテロ接合界面におけるキャリアの空乏化の問題を解決すること。

【解決手段】 HBTのエミッタ層として働くn型InGaP層7とその上に形成されるGaAs層8の間に、高ドープ層である電荷補償層11を形成することでその界面におけるキャリアの空乏化の現象によるベース電流の増加を抑制し、HBTの低コレクタ電流での電流増幅率の低下を防ぐようにした。さらに、この空乏化の現象の影響を低減するために導入したn型不純物の量が多すぎてエミッタ−ベース間の逆方向の耐圧が低下することがないよう、n型不純物の量を定量的に調整し、エミッタ−ベース間の逆方向の耐圧をたもちつつ、低コレクタ電流での電流増幅率の低下を防止するようにした。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板の中に分離領域を熱拡散により形成する際に、その横方向拡散を抑制して、半導体集積回路の微細化を実現する。

【解決手段】第3のホトレジスト24をマスクとして、第3の開口部K3から、ボロン(B+)をエピタキシャル層21にイオン注入してP型の不純物領域25を形成する。そして、シリコン酸化膜23上に、P型の不純物領域25と部分的にオーバーラップする領域に第4の開口部K4(リン注入領域)を有する第4のホトレジスト26を形成する。第4のホトレジスト26をマスクとして、P型の不純物領域25が除去されたエピタキシャル層21の表面にリン(P+)をイオン注入して、P型の不純物領域25に隣接したN型の不純物領域28を形成する。その後、熱拡散を行うことにより、エピタキシャル層21の中にP型の上分離領域29が形成され、この上分離領域29と下分離領域22とは連結されて分離領域30が形成される。

(もっと読む)

1 - 20 / 42

[ Back to top ]