Fターム[5F003BP34]の内容

バイポーラトランジスタ (11,930) | 製法 (1,830) | エピタキシャル (577) | 多結晶、単結晶同時成長 (63)

Fターム[5F003BP34]に分類される特許

1 - 20 / 63

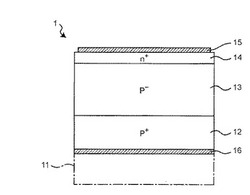

バイポーラ半導体素子およびその製造方法

【課題】SiC基板をp型とした結晶品質の良いSiCバイポーラ素子を提供する。

【解決手段】このダイオード素子1によれば、p型のSiCアノード層12,p型のSiCドリフト層13とn+型SiCカソード層14をn型SiC基板21上にエピタキシャル成長により形成してから、n型SiC基板21を除去した。つまり、p型基板に見立てるp+型4H-SiCアノード層12は、エピタキシャル成長により作製するから、バルク成長で作製されるp型基板に比べて結晶成長速度が遅く、p型ドーパントであるアルミニウムの濃度を上げても、結晶品質が良くなる。したがって、この結晶品質が良いp+型4H-SiCアノード層12を基板に見立てることができ、SiC基板をp型とした結晶品質の良いSiCダイオード素子を実現できる。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタのエミッタ窓における絶縁膜厚の変動をなくし、素子特性が安定した半導体装置を提供する。

【解決手段】バイポーラトランジスタを、コレクタ領域を含む基板1、基板1上にエピタキシャル成長で形成されたSiGe層126、SiGe層126上にポリシリコンによって形成されたエミッタ108を備え、エミッタ108とSiGe層126との界面において、ポリシリコン膜106とSiN膜127とでエミッタ窓120を形成し、SiN膜127がSiGe層126の直上に配置されるように形成する。

(もっと読む)

半導体装置の製造方法

【課題】バイポーラトランジスタの動作速度を高速化できるようにした半導体装置の製造方法を提供する。

【解決手段】単結晶Si基板1に設けられたn型のコレクタ層20と、コレクタ層20の表面の周辺部上に設けられたSiO2膜21と、SiO2膜21を覆ってコレクタ層20の表面の中央部に接合するp型のベース層30と、を有し、ベース層30は、コレクタ層20の表面の中央部上に設けられた単結晶SiGe膜31aと、SiO2膜21を覆うように単結晶SiGe膜21上に積層された単結晶Si膜35aとを含む。ベース層30とコレクタ層20との接合領域60がコレクタ層20の表面の中央部に限定されるため、接合面積を小さくすることができ、ベース層とコレクタ層との間の容量CBCを低減することができる。

(もっと読む)

不純物濃度プロファイルの測定方法、その方法に用いられるウェーハ、および、その方法を用いる半導体装置の製造方法

【課題】半導体層の不純物濃度およびプロファイルを正確に制御することを可能とする不純物濃度プロファイルの測定方法、その方法に用いられるウェーハ、および、それを用いた半導体装置の製造方法を提供する。

【解決手段】基板10と、前記基板10の主面上に設けられた半導体層12,17であって、前記主面上において互いに面積の異なる複数の第1領域17a,17bに形成された第1の部分と、前記主面上で前記第1領域17a,17bを取り囲む第2領域17cに形成され前記第1の部分とは異なる構造を有する第2の部分と、を有する半導体層12,17と、を有するウェーハを用いる。そして、前記半導体層のうちの複数の前記第1の部分の表面から深さ方向の不純物濃度プロファイルを測定し、前記第1の部分の面積に依存する前記不純物濃度プロファイルの変化を求める。

(もっと読む)

シリコンゲルマニウムトランジスタの製造方法

【課題】犠牲エミッタ膜を高い選択性で除去することにより特性のバラツキを抑制し、高精度なホトリソグラフィー技術を必要としないシリコンゲルマニウムトランジスタの製造方法を提供する。

【解決手段】SiGe膜6上のシリコン酸化膜8上にN型の犠牲エミッタポリシリコン23を形成し、その周囲にシリコン窒化膜からなるサイドウォール7を形成する。次に、ノンドープのポリシリコン膜24を形成し、サイドウォール7及び犠牲エミッタポリシリコン23をマスクにSiGe膜6にP型不純物をイオン注入して、外部ベース領域を形成する。次に、犠牲エミッタポリシリコン23をエッチングして除去し、その下のシリコン酸化膜8も除去する。その後、犠牲エミッタポリシリコン23等が除去されたエミッタ部分にエミッタポリシリコンを形成する。犠牲エミッタポリシリコン23をエッチングして除去する工程では、エッチャントとしてTMAH水溶液を使用する。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】イオン注入したダイヤモンドの高温高圧アニールにより起こるダイヤモンド表面のエッチングを防ぎ、従来の方法では得られない高品質P型、N型ダイヤモンド半導体を得るダイヤモンド半導体の作製方法を提供すること。

【解決手段】ダイヤモンド基板5−11を用意し、そのダイヤモンド基板5−11上にマイクロ波プラズマCVD装置を用い、メタンを反応ガスとして基板温度700℃でダイヤモンド薄膜5−12を1μm積層する。上記ダイヤモンド薄膜5−12にイオン注入装置を用い、加速電圧60kV、ドーズ量1×1014cm−2でドーパントを打ち込む。その後、イオン注入ダイヤモンド薄膜5−13上に保護層(白金)5−14を形成する。表面に保護層5−14が形成されたイオン注入ダイヤモンド薄膜5−13を、超高温高圧焼成炉内に配置し、3.5GPa以上、600℃以上の圧力、温度下でアニールする。

(もっと読む)

半導体装置及びその製造方法

【課題】結晶欠陥による接合リークを防止しながら、バイポーラトランジスタの面積を縮小し、コレクタ容量の低減によってトランジスタ特性を向上できるようにした半導体装置及びその製造方法を提供する。

【解決手段】活性領域1からSTI4上にかけて連続して形成したSiGe膜は、半導体基板3上ではSiGeエピ膜6となり、STI4上ではSiGeポリ膜7となる。半導体基板3とSTI4の境界はSiGe−HBT形成工程以前の洗浄工程によって段差15が生じており、SiGeエピ膜6及び半導体基板3には、上記境界を基点とした結晶欠陥が応力によって発生する可能性がある。この境界に第1のP型不純物層8及び第2のP型不純物層9を設けることで、結晶欠陥をこれらP型不純物層8、9に内包し、接合リークの発生を抑制する。

(もっと読む)

バイポーラ・トランジスタ構造およびその製造方法

【課題】エミツタ・ベース間の接合界面特性の最適化により、性能が改善されたバイポーラ・トランジスタ構造そのおよび製造方法を提供する。

【解決手段】バイポーラ・トランジスタは、(1)半導体基板内に少なくとも部分的に位置決めされたコレクタ領域15と、(2)コレクタ領域に接触するベース領域16と、(3)ベース領域に接触するエミッタ領域16Aとを含む。エミッタ領域とベース領域の界面は、酸素不純物と、フッ素不純物および炭素不純物から成るグループから選ばれた少なくとも1つの不純物とを含む損傷領域16Aをエミツタ開口のベースを含む層16に形成することにより、バイポーラ・トランジスタの性能を改善する。それらの不純物は、ベース領域を構成するベース材料のプラズマ・エッチング処理または代わりに無水アンモニアおよびフッ化水素処理が後に続く熱処理によって界面に導入することができる。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】電子デバイスのスイッチング速度等の性能を向上させる。半導体基板の結晶性を向上させる。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層とをこの順に有する半導体基板であって、SixGe1−x結晶層上に設けられる阻害層と、SixGe1−x結晶層に格子整合または擬格子整合している化合物半導体とを備え、阻害層はSixGe1−x結晶層にまで貫通する開口を有し、かつ化合物半導体の結晶成長を阻害する半導体基板を提供する。また、上記開口の内部でSixGe1−x結晶層に格子整合または擬格子整合する化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ高製造歩留まりで、BiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】シャロートレンチ3、ディープトレンチ6に囲まれた半導体層2の基板領域17に、p型の単結晶半導体からなるエピタキシャル・ベース層24が島状に形成される。当該島状領域を含む半導体層2上の全面に窒化シリコン膜42、酸化シリコン膜43が形成される。島状領域上の異なる位置の窒化シリコン膜42、酸化シリコン膜43には、少なくとも2つの開口部が形成され、開口部が形成された窒化シリコン膜42、酸化シリコン膜43上に半導体膜44が形成される。当該半導体膜44が選択的に除去され、一方の開口部において島状領域に接続するベース電極と、他方の開口部において島状領域に接続するエミッタ電極とが同時に形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】寄生容量を低減しつつ、トランジスタが形成される半導体層に歪応力を与える。

【解決手段】半導体層3に形成されたコレクタ層3aの表面および裏面にストレス印加層5を形成し、ストレス印加層5を介して埋め込み絶縁層6上に配置されたベース層9をコレクタ層3aの側壁に選択的に形成し、ベース層9の側壁を絶縁膜10から露出させる開口部12を形成し、開口部12を介してベース層9の側壁に接続されたエミッタ層13aを埋め込み絶縁層6上に形成する。

(もっと読む)

半導体装置及びその製造方法並びにその半導体装置を用いたスーパーヘテロダイン方式の通信機

【課題】バイポーラトランジスタのベース走行時間の低減とエミッタ・ベース接合容量の低減により、遮断周波数と低電流駆動性能の向上を図ったバイポーラトランジスタを提供する。

【解決手段】半導体基板上に設けられた第1導電型の第1の半導体層5と、前記第1の半導体層の上に設けられた第1導電型の第2半導体層6と、前記第2半導体層上に設けられた第2導電型の第3の半導体層7と、該第3の半導体層上に設けられ、開口部を有する第1の絶縁膜9と、前記開口部内に設けられた第1導電型の第4の半導体層11と、前記第4の半導体層上に設けられた第1導電型の第5の半導体層13とで構成され、第4の半導体層が第1の絶縁膜の側壁に接しないように形成し、少なくとも前記第4の半導体層と第1の絶縁膜で囲まれた空洞12を有して成ることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 シリコン基板上にゲルマニウムを主成分とする半導体素子を形成する際に、バッファ層を薄くすることで段差を減らし、同一基板上にシリコン系半導体素子を混載することを容易にする。

【解決手段】 具体例を述べれば、バッファ層をゲルマニウム層とシリコン層の2層とし、シリコン層のみを溶融することでゲルマニウムの面内原子間隔を安定的に保持するバッファ層を形成し、その上にゲルマニウム層を形成することで転位密度等の結晶欠陥を低減する。

(もっと読む)

半導体装置

【課題】SiGe混晶層を有する半導体装置において、高い高周波特性と安定した低いベースコンタクト抵抗とを得られるようにする。

【解決手段】半導体装置は、N型のコレクタ層1aと、コレクタ層1aの上に形成され、P型SiGe層3bを含む真性ベース層となるSiGeエピ膜3と、SiGeエピ膜3の周囲に形成され、P型の多結晶シリコン層及びP型の多結晶シリコンゲルマニウム層を含むベース引き出し電極4と、SiGeエピ膜3の上部に形成されたN型のエミッタ層8とを有している。真性ベース層の上部には、Si−Cap層3cが形成されており、エミッタ層8は、Si−Cap層3cの上部に形成された上部エミッタ領域8bと、該上部エミッタ領域8bの下側に該上部エミッタ領域8bと接して形成された下部エミッタ領域8aとにより構成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】非選択エピタキシャル法により半導体層を形成しても、エミッタとベースとを確実に接続して高い信頼性を確保することができる半導体装置及びその製造方法を提供する。

【解決手段】非選択エピタキシャル成長法により、ベース開口部8の内壁を覆うようにシリコン酸化膜7の全面にSiGe膜9を成長させる。このときの成膜条件としては、ベース開口部8内において、底部9aが単結晶からなり、側壁部9b等のその他の部位が多結晶となると共に、側壁部9bの膜厚が底部9aの膜厚の1.5倍以下になる成膜条件を選択する。このような非選択エピタキシャル成長では、原料ガスとして、モノシラン、水素、ジボラン及びゲルマンを用いる。このとき、モノシラン及び水素の各流量は、夫々20sccm、20slmとする。また、成長温度を650℃、ジボランの流量を75sccmに設定し、ゲルマンの流量を35sccmに設定する。

(もっと読む)

半導体装置の製造方法

【課題】シリサイド化の工程をMOSトランジスタ及びHBTと別けることなく、抵抗値のばらつきが小さいヒューズ素子を形成する半導体装置の製造方法を実現できるようにする。

【解決手段】半導体装置の製造方法は、MOSトランジスタ形成領域11Bにゲート電極22及びソースドレイン領域25を形成する工程と、MOSトランジスタ形成領域11Bを除いて、半導体基板11の上にシリコン及びシリコン以外のIV族元素を含む混晶膜と、シリコン膜とが順次積層された積層膜31A、31Bを形成する工程と、シリコン膜30Bの露出部分、ゲート電極22の上部及びソースドレイン領域25の上部をシリサイド化する工程とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】工程数を増加させることなく高速バイポーラトランジスタと高耐圧バイポーラトランジスタを同一半導体基板上に形成し、高耐圧バイポーラトランジスタを使用する回路の歪特性を低減できる半導体装置の製造方法の提供。

【解決手段】半導体基板101上に、コレクタの一部となる埋込み領域102を、第1、第2のバイポーラトランジスタの形成領域に同一工程で形成し、エピタキシャル層104を形成し、第1の縦型バイポーラトランジスタの形成領域においては、埋込み領域102をベース形成領域の全体に形成し、第2の縦型バイポーラトランジスタの形成領域においては、埋込み領域102をベース形成領域の1箇所に埋込み領域を形成しない領域を有して形成する。第2の縦型バイポーラトランジスタの埋込み領域を形成しない領域では、周囲からの不純物の拡散により、縦方向の拡散拡がり量が連続的に狭くなり、埋込み領域を形成しない領域が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】ベース・エミッタをエピタキシャル成長により形成するバイポーラトランジスタにおいて、真性ベースを薄くして遮断周波数を向上すると同時に、厚い外部ベースを形成することでベース抵抗を低減する。

【解決手段】具体例を述べれば、ベース層をエピタキシャル成長した後に、低温アニールを行うことで、開口部周辺部分のシリコン・ゲルマニウム層に凸部ができるように変形させ、真性ベースのキャリア走行時間を増大させずにベース抵抗を低減する。

(もっと読む)

半導体装置の製造方法

【課題】製造工程数が増加するのを抑制しながら、電極の側方に形成された異種の材料からなる複合膜の残渣の除去を容易に行うことが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、シリコン基板11の電界効果型トランジスタが形成される領域B上にゲート電極を形成する工程と、シリコン基板11のバイポーラトランジスタが形成される領域A上にバイポーラトランジスタを構成するSiGeからなるエピタキシャル層19aを形成する工程と、エピタキシャル層19aの形成時にゲート電極の側方に形成されるSiGeおよび多結晶シリコンからなるエッチング残渣19c、25bおよび43aを除去する工程と、その後、ゲート電極の側方を覆うサイドウォール絶縁膜と、エミッタ電極25の側方を覆うサイドウォール絶縁膜とを形成する工程とを備える。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタの所望の特性が出なくなるのを抑制することが可能な半導体装置を提供する。

【解決手段】この半導体装置は、バイポーラトランジスタ1と、素子分離絶縁膜17および素子分離絶縁膜16と、ベース・コレクタ間分離絶縁膜18とを備えている。また、ベース・コレクタ間分離絶縁膜18と素子分離絶縁膜16との間に埋込コレクタ領域12のリーチスルー領域12aが配置されており、ベース電極20および21は、それぞれ、ベース・コレクタ間分離絶縁膜18および素子分離絶縁膜17に乗り上げるように配置されており、素子分離絶縁膜17のベース電極20が乗り上げている部分およびベース・コレクタ間分離絶縁膜18のベース電極21が乗り上げている部分の厚みは、バイポーラトランジスタ1が形成される領域以外の領域に形成される素子分離絶縁膜16の厚みよりも大きい。

(もっと読む)

1 - 20 / 63

[ Back to top ]