Fターム[5F003BP96]の内容

バイポーラトランジスタ (11,930) | 製法 (1,830) | エッチング (502) | 多工程のエッチング方法 (270) | エッチングレートの差を利用するもの (76)

Fターム[5F003BP96]に分類される特許

21 - 40 / 76

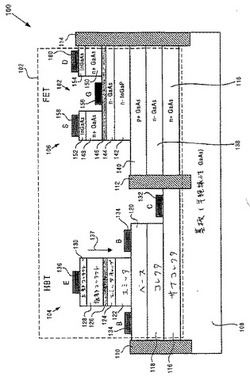

増大した直線性および製造可能性を有するFETを含むBiFET

【課題】基板上に位置するBiFETにおいて、HBT性能の低下を引起すことなくFETの製造可能性増大を達成させる。

【解決手段】基板上に位置するBiFET100は、基板の上に位置するエミッタ層部分122を含み、エミッタ層部分は第1のタイプの半導体を含む。HBTはエッチストップ層の第1の部分126をさらに含み、エッチストップ層の第1の部分はInGaPを含む。BiFETは基板の上に位置するFET106をさらに含み、FETはソース領域およびドレイン領域を含み、エッチストップ層の第2の部分146はソース領域およびドレイン領域の下に位置し、エッチストップ層の第2の部分はInGaPを含む。FETはエッチストップ層の第2の部分の下に直接接して位置する第2のタイプの半導体層をさらに含む。エッチストップ層はFETの線形性を増大させ、HBTの電子の流れを低下させない。

(もっと読む)

半導体装置およびその製造方法

【課題】形成する素子に要求される素子間耐圧や素子内部耐圧に応じたディープトレンチ膜を有する半導体装置を提供する。

【解決手段】P型のシリコン基板11上に、N+型埋め込み層12と、N型半導体層13と、が積層された基板10と、基板10にN+型埋め込み層12の形成位置よりも深く形成され、基板10内の素子形成領域内を区画するディープトレンチ20と、ディープトレンチ20の内壁に沿って形成される側壁酸化膜23,24と、ディープトレンチ20内を埋めるTEOS膜を含むディープトレンチ膜26と、ディープトレンチ膜26で区画される素子形成領域に形成されるLDMOSと、を備え、ディープトレンチ20は、N+型埋め込み層12の上面よりも浅い位置の境界深さまでの第1のディープトレンチ21と、境界深さから底部までの第1のディープトレンチ21よりも小さい開口径を有する第2のディープトレンチ22によって構成される。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】エミッタ電子輸送特性やエミッタ注入効率を劣化させることなく、レッジ部を薄層化することが容易で、微細化に適したヘテロ接合バイポーラトランジスタを提供すること。

【解決手段】エミッタ層は、第1の半導体層11と、第2の半導体層12と、第3の半導体層13との積層構造からなり、第3の半導体層13は、第2の半導体層12に対してウェット・エッチングにより選択的に除去でき、第2の半導体層12は、第1の半導体層11に対してウェット・エッチングにより選択的に除去でき、第1の半導体層11と第3の半導体層13のバンドギャップはベース層4のバンドギャップよりも大きく、第2の半導体層12は不純物添加によって縮退しており、第3の半導体層13は不純物添加によって中性領域を形成しているヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

ヘテロ接合バイポーラトランジスタの製造方法

【課題】アスペクト比の高いサブミクロンサイズのエミッタ電極パタンを線幅制御性良く形成することを可能とするヘテロ接合バイポーラトランジスタの製造方法を提供すること。

【解決手段】エミッタコンタクト層6上にTi層(図示せず)、エッチングストッパー用のW層7、Au層8、エッチングマスク用W層9、フォトレジストパタン10を形成し、フォトレジストパタン10をマスクとしてエッチングマスク用W層9を選択的に除去することによってWパタン9とし、Wパタン9をマスクとして、Au層8を、酸素ガスを含有する混合ガスを用いる反応性イオンエッチング法により選択的に除去し、Wパタン9をマスクとして、エッチングストッパー用のW層7、Ti層を選択的に除去することを特徴とするヘテロ接合バイポーラトランジスタの製造方法を構成する。

(もっと読む)

発光並びにレーザ半導体素子および方法

半導体発光素子は、エミッタとコレクタ領域の間のベース領域を有するヘテロ結合バイポーラ発光トランジスタと、エミッタ、ベース、およびコレクタ領域それぞれで、結合電気信号ためのエミッタ、ベース、およびコレクタ電極と、前記ベース領域の中に量子サイズ領域とを備え、前記ベース領域は、前記量子サイズ領域のエミッタ側上に第1のベースサブ領域と、前記量子サイズ領域のコレクタ側上に第2のベースサブ領域を備え、前記第1と第2のベースサブ領域は非対称バンド構造を有する。2端子半導体構造から光放射を生み出すための方法は、第1の伝導型のエミッタ領域と、第1の伝導型の領域と反対に第2の伝導型のベース領域の間に第1の半導体接合、および前記ベース領域とドレイン領域との間に第2の半導体接合を含む半導体構造を提供するステップと、前記ベース領域の間に量子サイズ効果を示す領域を提供するステップと、前記エミッタ領域に結合されたエミッタ電極を提供するステップと、前記ベース領域と前記ドレイン領域に結合されたベース/ドレイン電極を提供するステップとを含み、前記半導体構造から光放射を得るため、前記エミッタおよび前記ベース/ドレイン電極に信号を印加する。 (もっと読む)

半導体装置及びその製造方法並びにその半導体装置を用いたスーパーヘテロダイン方式の通信機

【課題】バイポーラトランジスタのベース走行時間の低減とエミッタ・ベース接合容量の低減により、遮断周波数と低電流駆動性能の向上を図ったバイポーラトランジスタを提供する。

【解決手段】半導体基板上に設けられた第1導電型の第1の半導体層5と、前記第1の半導体層の上に設けられた第1導電型の第2半導体層6と、前記第2半導体層上に設けられた第2導電型の第3の半導体層7と、該第3の半導体層上に設けられ、開口部を有する第1の絶縁膜9と、前記開口部内に設けられた第1導電型の第4の半導体層11と、前記第4の半導体層上に設けられた第1導電型の第5の半導体層13とで構成され、第4の半導体層が第1の絶縁膜の側壁に接しないように形成し、少なくとも前記第4の半導体層と第1の絶縁膜で囲まれた空洞12を有して成ることを特徴とする。

(もっと読む)

高周波デバイスの誘電体突出部

(例えばシリコン)バイポーラデバイス(40、100、100’)の高周波性能は、外部ベースコンタクト(46)とコレクタ(44、44’、44”)との間の容量結合(Cbc)の低減により向上される。外部ベースコンタクト(46)をコレクタ(44、44’、44”)の外周部(441)から隔てるように、製造中に誘電体突出部(453、453’)が作製される。誘電体突出部(453、453’)は、外部ベースコンタクト(46)を真性ベース(472)に結合するトランジション領域(461)の下に位置する。デバイス製造中に、多層誘電体スタック(45)が真性ベース(472)に隣接して形成され、真性ベース(472)から外部ベースコンタクト(46)へのトランジション領域(461)を形成可能なアンダーカット領域(457、457’)の同時作製が可能にされる。キャビティ(457、457’)内に形成されたトランジション領域(461)が、それをコレクタ(44、44’、44”)の外周部(441)から隔てる誘電体突出部(453、453’)の上に位置することで、ベース−コレクタ接合容量(Cbc)が低減される。デバイスのfMAXが有意に上昇される。  (もっと読む)

(もっと読む)

半導体デバイスの製造方法

【課題】犠牲層を介してInP系のデバイスを形成したときに、犠牲層としてAlAs単層を用いたときのデバイス特性よりも良好なデバイス特性を得ることができ、かつ、犠牲層をエッチングする際に、デバイス層もエッチングされてしまう虞のない半導体デバイスの製造方法を提供する。

【解決手段】保護膜35の平坦面35Aに支持基板10を接合もしくは接着したのち、InPと疑似格子整合するInAlAsからなる犠牲層42を、フッ酸を用いて選択的に除去することにより、InP基板41を、InP系のデバイス層21を含む支持基板10から剥離する。

(もっと読む)

半導体装置

【課題】 エッチング量を工程内で測定し、フィードバックをかけることにより、エッチング量のばらつきを無くすことを実現する。

【解決手段】 半導体層が選択エッチングされることにより半導体素子が形成される半導体素子領域と、前記半導体層と同じ材質からなり、前記半導体素子が選択エッチングされた量を検査するモニタ用半導体素子が設けられたモニタ領域とを有することを特徴とする。

(もっと読む)

半導体素子の製造方法

【課題】 偶発的に生成される層を異方性エッチングすることにより、エッチングを行う時間によるエッチングのばらつきを改善し、かつ任意の層を異方性エッチングで一定量エッチングすることにより、回り込みエッチングの制御性の向上を図ることを実現する。

【解決手段】 第1の層の表面に第2の層を積層したものに、前記第1の層を横方向にエッチングする半導体素子の製造方法において、前記第2の層側から前記第1の層側に向かって縦方向に異方性エッチングを行うステップと前記第1の層を横方向に等方性エッチングを行うステップとを有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】トレードオフの関係にあるHBTの特性上のメリットとHFETの特性上のメリットとを両立することが可能な半導体装置及びその製造方法を提供する。

【解決手段】Bi−HFETであって、HBTは、順次積層されたサブコレクタ層107、GaAsコレクタ層108、GaAsベース層109及びInGaPエミッタ層110を有し、サブコレクタ層107は、GaAs外部サブコレクタ領域107aと、GaAs外部サブコレクタ領域107a上に位置するGaAs内部サブコレクタ領域107bとを有し、GaAs外部サブコレクタ領域107a上には、メサ状のコレクタ部830と、コレクタ電極203とが離間して形成され、HFETは、GaAs外部サブコレクタ領域107aの一部により構成されたGaAsキャップ層105と、GaAsキャップ層105上に形成されたソース電極304及びドレイン電極305とを有する。

(もっと読む)

絶縁膜層分離IC製造

【課題】二酸化ケイ素や窒化ケイ素など非常に薄い低応力誘電体材料と半導体層とで形成された可とう性の膜で集積回路(24、26、28、...30)を製造する汎用手法を提供する。

【解決手段】膜(36)の半導体層中に半導体デバイス(24、26、28...30)を形成する。最初に、標準厚さの基板(18)から半導体膜層(36)を形成し、次いで、基板の薄い表面層をエッチングまたは研磨する。他のバージョンでは、ボンディングされた従来の集積回路ダイ用の支持および電気的相互接続として可とう性膜を使用し、膜中の複数の層に相互接続部を形成する。1つのそのような膜に複数のダイを接続することができ、膜は次いでマルチチップ・モジュールとしてパッケージされる。

(もっと読む)

半導体装置およびその製造方法

【課題】ベース・エミッタをエピタキシャル成長により形成するバイポーラトランジスタにおいて、真性ベースを薄くして遮断周波数を向上すると同時に、厚い外部ベースを形成することでベース抵抗を低減する。

【解決手段】具体例を述べれば、ベース層をエピタキシャル成長した後に、低温アニールを行うことで、開口部周辺部分のシリコン・ゲルマニウム層に凸部ができるように変形させ、真性ベースのキャリア走行時間を増大させずにベース抵抗を低減する。

(もっと読む)

半導体装置およびその製造方法

【課題】電流リーク及び寄生抵抗が抑制され、安定した電流利得を実現する半導体装置を提供する。

【解決手段】n型コレクタ層102上に、第一の半導体層110を成長させつつ、p型多結晶シリコン膜106、シリコン窒化膜108を含む積層膜からなる庇部の下面に露出したp型多結晶シリコン膜106の下方に第一の多結晶半導体層120を成長させ、その後第一の多結晶半導体層120を選択的に除去する。さらに第二の半導体層112、114、第三の半導体層116を成長させつつ、庇部の下面に露出したp型多結晶シリコン膜106の下方に第二の多結晶半導体層122、124、第三の多結晶半導体層126を、シリコン窒化膜108に接触しないように選択的に成長させ、第三の半導体層と、第三の多結晶半導体層を接触させる。

(もっと読む)

絶縁膜層分離IC製造

【課題】二酸化ケイ素や窒化ケイ素など非常に薄い低応力誘電体材料と半導体層とで

形成された可とう性の膜で集積回路(24、26、28、...30)を製造する汎用手

法を提供する。

【解決手段】膜(36)の半導体層中に半導体デバイス(24、26、28...3

0)を形成する。最初に、標準厚さの基板(18)から半導体膜層(36)を形成し、次

いで、基板の薄い表面層をエッチングまたは研磨する。他のバージョンでは、ボンディン

グされた従来の集積回路ダイ用の支持および電気的相互接続として可とう性膜を使用し、

膜中の複数の層に相互接続部を形成する。1つのそのような膜に複数のダイを接続するこ

とができ、膜は次いでマルチチップ・モジュールとしてパッケージされる。

(もっと読む)

半導体装置

【課題】エミッタ電極に対するコンタクト部を容易に形成しながら、エミッタ層の幅を小さくすることが可能な半導体装置を提供する。

【解決手段】このバイポーラトランジスタ(半導体装置)100は、シリコン層7と、シリコン層7の表面に形成された不純物領域8と、不純物領域8上に形成されたポリシリコン層からなるエミッタ電極10aと、不純物領域8とエミッタ電極10aとの間に形成され、エミッタ電極10aの幅W3よりも小さい幅W2を有するSiGe層9とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の第2素子が形成される領域にエッチングによるダメージが発生するのを抑制しながら第1素子のゲート電極の側面を覆うサイドウォール絶縁膜を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置100の製造方法は、シリコン基板11の電界効果型トランジスタ2が形成される領域にゲート電極28を形成する工程と、ゲート電極28の表面およびシリコン基板11のバイポーラトランジスタ1が形成される領域を覆うようにスペーサ絶縁膜42を形成する工程と、スペーサ絶縁膜42を表面から所定の厚み分エッチングすることにより、シリコン基板11のバイポーラトランジスタ1が形成される領域にスペーサ絶縁膜42を所定の厚み分残した状態でゲート電極28の側面を覆うサイドウォール絶縁膜30を形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】高精度のセルフアライメント構造を形成して半導体層に拡散層を形成する不純物元素のイオン注入を行うことにより、特性の向上を図る半導体装置を製造する半導体装置の製造方法を提供する。

【解決手段】各拡散層形成領域7〜9を相互に位置決めするイオン注入制御開口部13〜14を形成する工程を施した後に、各拡散層毎にイオン注入開口部29,30を形成するイオン注入マスク層形成工程と、各イオン注入開口部から不純物元素をイオン注入して各拡散層を形成する拡散層形成工程を実施する。イオン注入制御開口部が各拡散層形成工程におけるセルフアライメント構造を構成して各拡散層が形成される。

(もっと読む)

バイポーラ型トランジスタ及びバイポーラ型トランジスタの製造方法

【課題】ベース引き出し用電極とベース領域との接続抵抗を低抵抗化できる技術の提供。

【解決手段】半導体基板上に、第1導電型のコレクタ領域、第1絶縁膜、第2導電型を有するベース引き出し用電極、及び第2絶縁膜をこの順で設け、第2絶縁膜及びベース引き出し用電極の一部をエッチングして、第1絶縁膜の表面を露出させ、開口部の側壁に、成長防止用絶縁膜を形成する。露出した第1絶縁膜をエッチングして、前記コレクタ領域の表面を露出させる。露出したコレクタ領域上に、ベース領域を選択エピタキシャル成長により形成する。ベース領域形成工程の後、前記成長防止用絶縁膜を除去する。その後、開口部の側壁に、第2導電型の不純物が高濃度でドープされた低抵抗化用側壁を形成する。低抵抗化用側壁を被覆するように絶縁性の分離膜を形成し、エミッタ層を、開口部の底部でベース領域と接する様に、開口部に埋めこむエミッタ層形成工程と、を具備する。

(もっと読む)

単結晶ベースを有するヘテロ接合バイポーラ・トランジスタ及び関連する方法

【課題】 単結晶ベースを有するヘテロ構造バイポーラ・トランジスタ及びこれに関連する方法を提供すること。

【解決手段】 ヘテロ構造バイポーラ・トランジスタ(HBT)及び関連する方法が開示される。一実施形態において、HBTは、基板と、基板の上のポリシリコン・エミッタと、基板内のコレクタと、コレクタに隣接した少なくとも1つの分離領域と、各分離領域の上に延びる単結晶シリコン・ゲルマニウムを含む真性ベースと、単結晶外部ベースとを含む。1つの方法は、分離領域の形成を、後で誘電体に変換される注入された多孔質シリコンの形成と置き換えるステップを含む。結果的に、分離領域の上に横方向の寸法が拡張された単結晶シリコン・ゲルマニウム・ベース・プロファイル層を形成することができる。

(もっと読む)

21 - 40 / 76

[ Back to top ]