Fターム[5F003BP96]の内容

バイポーラトランジスタ (11,930) | 製法 (1,830) | エッチング (502) | 多工程のエッチング方法 (270) | エッチングレートの差を利用するもの (76)

Fターム[5F003BP96]に分類される特許

61 - 76 / 76

ドライエッチング方法、及び半導体装置の製造方法、半導体装置

【課題】AlもしくはInを含む化合物半導体層の上に積層されたAlもしくはInを含まない化合物半導体層を選択的に除去する工程において、アンダーカットが生じず、且つ、孤立パターン部と密集パターン部における加工形状差の生じにくい、ドライエッチング方法を提供する。

【解決手段】前記ドライエッチング工程にて、エッチング装置の下部電極温度を10℃以下に制御しドライエッチングを行うことにより、副生成物の揮発を抑制し、より安定した側壁保護効果が得られ、疎部、密部における加工形状差の少ない均一なエッチング形状が得られる。また、副生成物は温度の低い基板へ選択的に堆積するためドライエッチング装置のチャンバー内には付着せず、デポ生成ガスを使用した場合のデメリットである、雰囲気変動およびパーティクルの発生による、メンテサイクルの短命化を回避できる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 微小開口の孔の形成が容易で、断線が発生しにくく、且つオーバーエッチングによる電極等の再付着現象を発生させないようにする。

【解決手段】 有機系の第2の絶縁層22を珪素系の第1の絶縁層21と第3の絶縁層23で挟んで絶縁膜20を形成し、その絶縁膜に対して、異方性エッチングと異方性の強いエッチングを交互に繰り返すことにより、第2の絶縁層22部分に段部29を有し、基板側に向かって凸型の孔30を形成し、回路素子1の電極1aと絶縁膜表面との間を接続する配線部として蒸着される導電材が、段部29に堆積する導電材を介して一体化するようにしている。

(もっと読む)

自己整合されたレトログレード外部ベース注入プロファイル及び自己整合されたシリサイドを有するバイポーラ・トランジスタ

【課題】 外部ベース注入部、外部ベース・シリサイド及びエミッタが互いに自己整合された、自己整合型バイポーラ・トランジスタを提供すること。

【解決手段】 基板(10)内のコレクタ(12)と、コレクタの上にある内部ベース(14)と、内部ベースに隣接した外部ベースと、内部ベースの上にあるエミッタ(130)とを含むバイポーラ・トランジスタ、及びトランジスタを形成する方法が開示される。外部ベースは、断面から見たときに、内部ベースと隣接した外部ベース注入領域(82、172、192)を含む。トランジスタは、内部ベースの上の基板上に、エミッタの下部のためのエミッタ・ペデスタル(50)をパターン形成することによって形成される。エミッタ・ペデスタルによって保護されない領域内に、外部ベースが形成される。その後、エミッタ、関連したスペーサ(180)及びシリサイド領域(220)が形成される。シリサイド、外部ベース及びエミッタは、全て互いに自己整合される。

(もっと読む)

改善されたベースエミッタ接合部を有するバイポーラトランジスタ及び製造のための方法

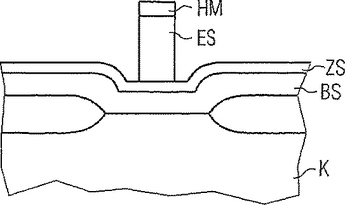

本発明は、基板を有し、この基板内に形成されたコレクタ(K)を有し、このコレクタの上に配置されたベース層に形成された単結晶のベース(B)を有し、このベースの上に配置された単結晶のエミッタ層(ES)を有する、改善されたバイポーラトランジスタに関する。本発明によれば、エミッタ層の構造は中間層(ZS)によって改善され、この中間層はエミッタ層とベースとの間に配置され、この中間層はエッチングストップ層として形成される。有利にはシリコンに対して選択的にエッチング可能なエピタキシャルに成長されるシリコンカーバイド層が利用される。  (もっと読む)

(もっと読む)

バイポーラトランジスタの形成方法

本発明はバイポーラトランジスタを形成する方法に関するものであり、この方法は次の工程を含む。すなわち、この方法は、第1導電型(n)のコレクタ領域(25)を含む半導体基板(1)を設ける工程であって、このコレクタ領域が基板に埋め込まれ、かつコレクタ領域の上面が露出する構成の工程と、単結晶ベース領域(30;32;120)を設ける工程と、第2導電型(p)のベース接続領域(40;160)をベース領域(30;32;34;120,130)の上に設ける工程と、絶縁領域(35;35’’;170)をベース接続領域(40;160)の上に設ける工程と、開口(F)を絶縁領域(35;35’’;170)及びベース接続領域(40;160)に形成してベース領域(30;32;34;120,130)を少なくとも一部露出させる工程と、絶縁サイドウォールスペーサ(55’;80;180)を開口に設けてベース接続領域(40;160)を絶縁する工程と、単結晶エミッタ層(60a)がベース領域(30;32;34;120,130)の上に、そして多結晶エミッタ層(60a)が絶縁領域(35;35’’;170)及びサイドウォールスペーサ(55’;80;180)の上に形成される構成のエミッタ層(60a,60b)を異なる構造に成長させてパターニングする工程と、そして熱処理工程を実施する工程と、を含む。  (もっと読む)

(もっと読む)

外部応力層を持つバイポーラ・トランジスタ

【課題】 高性能のバイポーラ・デバイスおよびその製造方法を提供する。

【解決手段】 バイポーラ・デバイスにおいて電荷キャリアの移動度を増加させる方法は、該デバイス内に圧縮歪みを生じさせて、該デバイスの内部ベースにおける正孔移動度を増加させるステップと、該デバイス内に引っ張り歪みを生じさせて、該デバイスの該内部ベースにおける電子移動度を増加させるステップと、を含む。圧縮歪みおよび引っ張り歪みは、デバイスの内部ベースの近傍に応力層を形成することによって生じさせる。応力層は、少なくとも一部が、デバイスのエミッタ構造体に隣接して、該デバイスのベース層内に埋め込まれる。応力層は、内部ベースと異なる格子定数を有する。

(もっと読む)

バイポーラトランジスタおよび関連構造におけるアライメント許容誤差を向上させるための方法

例示的一実施例によれば、ヘテロ接合バイポーラトランジスタ(HBT)などのバイポーラトランジスタは、上面(324)を有するベース(327)を備える。HBTは、ベースの上面に位置する、第1の内部スペーサ(317)および第2の内部スペーサ(318)をさらに備える。HBTは、ベース(327)の上面(324)の上に、第1の内部スペーサ(317)に隣接する第1の外部スペーサ(327)および第2の内部スペーサ(318)に隣接する第2の外部スペーサ(328)をさらに備える。この例示的実施例によれば、HBTは、第1および第2の内部スペーサ(317、318)の間に位置するエミッタ(326)をさらに備える。HBTは、第1および第2の外部スペーサ(327、328)の上に位置する中間酸化層(316)をさらに含んでもよい。HBTは、前記中間酸化層(316)の上に位置するアモルファス層(321)をさらに含んでもよい。HBTは、アモルファス層(321)の上に反射防止膜層(322)をさらに含んでもよい。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 従来では、エミッタ取り出し電極上のコンタクトホールが、エミッタ領域の直上部から離間して形成されていた。そのため、エミッタ−ベース間の寄生容量及びベース−コレクタ間の寄生容量が増大し、高周波特性が悪化するという問題があった。

【解決手段】 本発明では、コンタクトホール20が、エミッタ領域12の直上部に配置されているので、エミッタ取り出し電極14を微細化することができる。また、コンタクトホール21もエミッタ領域12側へと配置することができ、ベース取り出し電極13の延在長も短くすることが出来る。そのことで、エミッタ−ベース間の寄生容量及びベース−コレクタ間の寄生容量を低減することができ、素子の高周波特性を向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】 従来では、半導体層表面に堆積された絶縁層にコンタクトホールを形成する際に、半導体層表面に耐エッチング膜としての絶縁膜を形成することで、製造工程が煩雑となり、また、余計な製造コストが掛かるという問題があった。

【解決手段】 本発明では、コレクタ領域の拡散領域4表面のシリコン酸化膜8、TEOS膜9、20をエッチングする工程と、ベース取り出し電極16表面のTEOS12、20膜をエッチングする工程とを別工程とする。そして、露出した拡散領域4表面及びベース取り出し電極16表面にコバルトシリサイド膜21を形成する。コバルトシリサイド膜21をコンタクトホール25、26、27を形成する際の、耐エッチング膜として用いることで、オーバーエッチングを防ぐことができる。

(もっと読む)

半導体素子

【課題】 作製が容易で広い温度範囲で高速動作するホットエレクトロントランジスタを提供すること

【解決手段】 窒化物系半導体から構成されたコレクタ層107、コレクタ障壁層106、ベース層105、アンドープ第1エミッタ障壁層115およびエミッタ層102を順に備えた半導体素子であって、コレクタ層107、ベース層105およびエミッタ層102は、それぞれ、n型半導体から構成されており、第1エミッタ障壁層115は、エミッタ層102とベース層105との間に配置されており、第1エミッタ障壁層115のバンドギャップは、エミッタ層102のバンドギャップよりも大きく、第1エミッタ障壁層115に接してベース電極111が形成されている半導体素子。

(もっと読む)

シリコン・ゲルマニウム層中に高濃度のゲルマニウムを有するバイポーラ接合トランジスタおよびその形成方法

ヘテロ接合バイポーラ・トランジスタ内にゲルマニウム濃縮領域を形成する方法およびゲルマニウム濃縮領域を有するヘテロ接合バイポーラ・トランジスタ。シリコン・ゲルマニウム部分を有するベースが、コレクタの上に形成される。ベースの熱酸化が、熱酸化を受けたシリコン・ゲルマニウム部分の表面上にゲルマニウム濃縮領域を形成させる。エミッタが、ゲルマニウム濃縮部分領域の上に位置して形成される。ゲルマニウム濃縮領域が、改善された高周波/高速動作を含めて、有利な動作特性をヘテロ接合バイポーラ・トランジスタに与える。

(もっと読む)

(もっと読む)

BICMOSプロセスにおいてシード層トポグラフィを軽減する方法

バイポーラデバイスにおいてエピタキシャルベース層を形成する方法。同方法は:活性シリコン領域(10)に隣接したフィールドアイソレーション酸化物領域(12)を有する構造を提供するステップと;前記フィールドアイソレーション酸化物領域(12)上に窒化シリコン/シリコン積層(14,16)を形成するステップであって、前記窒化シリコン/シリコン積層(14,16)はシリコンの上位層(14)と窒化シリコンの下位層(16)とを含む、前記ステップと;階段状シード層を形成するために前記窒化シリコン/シリコン積層(14,16)にエッチングを実行するステップであって、前記窒化シリコンの下位層がエッチングされると同時に前記シリコンの上位層が横方向にエッチングされる、前記ステップと;前記階段状シード層および活性領域(10)とにわたってSi/SiGe/Si積層(20)を成長させるステップと;含む。  (もっと読む)

(もっと読む)

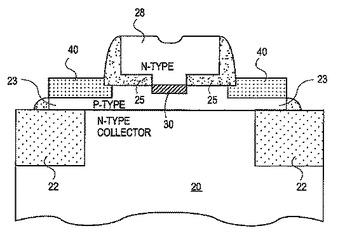

改善された外部ベース領域を備えたバイポーラ接合形トランジスタ及びその製造方法

バイポーラトランジスタ及びその製造方法に関する。第1のエピタキシャル層(23)上への第2の、より高濃度にドープされたエピタキシャル層の成長によって、外部ベース領域(40)が形成される。第2のエピタキシャル層は上にあるポリシリコンエミッタ台座(28)の下まで広がり、かつ、この台座(28)から絶縁される。  (もっと読む)

(もっと読む)

増大した線形性および製造可能性を有するFETを含むBiFET

例示的一実施例によれば、基板上に位置するBiFETは、基板の上に位置するエミッタ層部分を含み、エミッタ層部分は第1のタイプの半導体を含む。HBTはエッチストップ層の第1の部分をさらに含み、エッチストップ層の第1の部分はInGaPを含む。BiFETは基板の上に位置するFETをさらに含み、FETはソース領域およびドレイン領域を含み、エッチストップ層の第2の部分はソース領域およびドレイン領域の下に位置し、エッチストップ層の第2の部分はInGaPを含む。FETはエッチストップ層の第2の部分の下に位置する第2のタイプの半導体層をさらに含む。エッチストップ層はFETの線形性を増大させ、HBTの電子の流れを低下させない。  (もっと読む)

(もっと読む)

高いfTおよびfmaxを有するバイポーラ・トランジスタおよびこれを製造する方法

【課題】 ベース抵抗を低減したバイポーラ・トランジスタを提供する。

【解決手段】 高いfTおよびfmaxを有するバイポーラ・トランジスタ(100)は、エミッタ(104)、ベース(120)、およびコレクタ(116)を含む。エミッタは、下部(108)と、この下部を越えて延在する上部(112)とを有する。ベースは、真性ベース(140)および外部ベース(144)を含む。真性ベースは、エミッタの下部とコレクタとの間に位置する。外部ベースは、エミッタの下部からエミッタの上部を越えて延在し、エミッタの上部の下からエミッタの上部の下よりも外側まで延在する連続導体(148)を含む。連続導体は、ベース・コンタクト(図示せず)から固有ベースまでの低電気抵抗の経路を提供する。このトランジスタは、第2の導体(152)を含むことができ、これは、エミッタの上部の下に延在せず、これによって、外部ベースを介した電気抵抗を更に低減する。

(もっと読む)

HBTの製造方法

【課題】 オーバエッチングがべ一ス層まで及ぶことがなく、高速化を図ったHBTの製造方法を提供する。

【解決手段】 コレクタ層とベース層が同じエッチング液でエッチングされる材質で形成されている場合において、

を含んでいる。

(もっと読む)

61 - 76 / 76

[ Back to top ]