Fターム[5F004DB02]の内容

半導体のドライエッチング (64,834) | 被エッチング物 (6,778) | Si (1,365) | 多結晶Si (435)

Fターム[5F004DB02]に分類される特許

421 - 435 / 435

二層レジストプラズマエッチングの方法

【課題】

【解決手段】プラズマエッチング室内において、基板の上に形成された二層レジストをエッチングするための方法が提供される。該方法は、二層レジストの第1の層の上にパターンを形成された基板をエッチング室に導入する工程から開始される。次いで、SiCl4ガスがエッチング室に流し込まれる。次に、SiCl4ガスを流し入れつつエッチング室内においてプラズマを発生させる。次いで、二層レジストがエッチングされる。

(もっと読む)

最少スカラップ基板の処理方法

【解決課題】本発明は、最少スカラップ基板処理方法に関する。

【解決手段】基板を少スカラップで処理することによって耐久性と品質が改善される。ポリマー蒸着ステップと基板エッチングステップとをあらゆる順序で交互に実施することで、エッチングマスクを通して層に特徴部をエッチング加工する。さらに、プロセスステップ間のプロセスガス圧は実質的に等しくてもよい。また、基板処理全体を通じて継続プラズマ流が維持される。また、プロセスガスが250ミリ秒以下で切り替えて、1体の質量流制御バルブによってプロセスガスをコントロールできる。

(もっと読む)

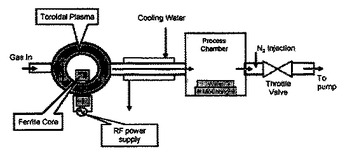

表面堆積物を除去するための遠隔チャンバ方法

本発明は、電子デバイスを製造する際に使用される堆積チャンバの内部などの表面から表面堆積物を除去するための改良されたリモートプラズマクリーニング方法に関する。改良は、遠隔チャンバから表面堆積物までの経路の内面のフルオロカーボンリッチプラズマ前処理を伴う。  (もっと読む)

(もっと読む)

デュアルドープポリシリコン及びシリコンゲルマニウムエッチング

【課題】

【解決手段】処理チャンバ内で、基板上に少なくとも一つのシリコンゲルマニウム層を有するスタックをエッチングする方法を提供する。シリコンゲルマニウムエッチングを提供する。エッチャントガスは、処理チャンバ内に提供され、エッチャントガスは、HBrと、不活性希釈剤と、O2及びN2の少なくとも一方とを含む。基板は、40℃未満の温度に冷却される。エッチャントガスは、シリコンゲルマニウム層をエッチングするために、プラズマに転換される。

(もっと読む)

表面堆積物を除去するための遠隔チャンバ方法

本発明は、電子デバイスを製造する際に使用される堆積チャンバの内部などの表面から表面堆積物を除去するための改良されたリモートプラズマクリーニング方法に関する。改良は、酸素とフルオロカーボンとを含む供給ガス混合物への窒素源の追加を伴う。改良は、窒素源を含む前処理ガス混合物を活性化し、活性化前処理ガスを、遠隔チャンバから表面堆積物までの経路に通過させることによる、経路の内面の前処理も伴う。  (もっと読む)

(もっと読む)

基板処理方法、プラズマ室および半導体デバイス

【課題】

【解決手段】基板処理のシステムおよび方法には、プラズマ室に基板を装填しプラズマ室の圧力を所定の圧力設定値に設定することが含まれる。プラズマ領域を構成するいくつかの内面が約200℃以上の処理温度に加熱される。プラズマを形成するために処理ガスがプラズマ領域に注入され、基板が処理される。

(もっと読む)

半導体反応器用の排気調整システム

本発明は、概して排気システムに関し、特に、過圧力および/または逆流の防止および組合せトラップ/消音器(126、126’)を含む、半導体エッチングおよび堆積プロセス用の排気調整システム(110、110’、110”)に関する。利点は、自動連続動作、予定外の真空ポンプ停止によるウェーハ損失の実質的ゼロ、低減した微粒子欠陥、および改善された歩留りを含む。  (もっと読む)

(もっと読む)

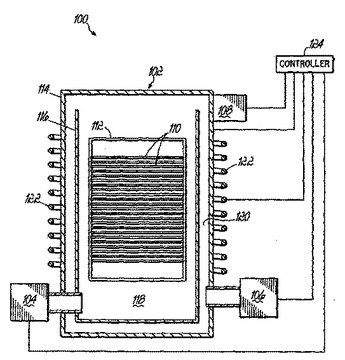

システムコンポーネントの状態をモニタリングするための方法およびそのための処理システム

処理中にコンポーネント(200,300)の状態をモニタリングする方法およびシステム。本方法は、処理中にコンポーネントを反応ガス(エロージョン生成物発生のためコンポーネント材をエッチングできる)に曝露することと、コンポーネントの状態を判定するため処理中にエロージョン生成物の放出をモニタリングすることを含む。モニターできる処理はチャンバークリーニング、同コンディショニング、基板エッチングおよび薄膜形成処理を含む。コンポーネントは、チューブ(25)、シールド、リング、バッフル、インジェクター、基板ホルダー(35,12)、ライナー、ペデスタル、キャップカバー、電極およびヒーター(15,20,65,70,122)等消耗部品でもよく、それらは保護コーティングを有していてもよい。処理システム(1,100)は、処理チャンバー(10,102)内のコンポーネント、ガス噴射システム(94,102)、チャンバー保護システム(92,108)およびコントローラ(90,124)を含む。  (もっと読む)

(もっと読む)

フィーチャ微小寸法の低減

【課題】レイヤ中にフィーチャを形成する方法を提供する。

【解決手段】レイヤ上にフォトレジストレイヤが形成される。フォトレジストレイヤがパターン付けされることによって、フォトレジスト側壁を持つフォトレジストフィーチャが形成され、フォトレジストフィーチャは第1微小寸法を有する。フォトレジストフィーチャの側壁上にコンフォーマルレイヤが堆積されることによって、フォトレジストフィーチャの前記微小寸法が低減される。レイヤ内でフィーチャがエッチングされ、レイヤフィーチャは、第1微小寸法より小さい第2微小寸法を有する。

(もっと読む)

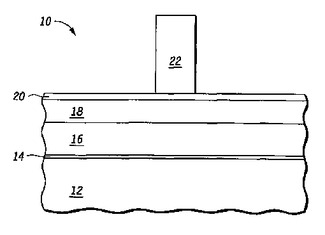

有機反射防止膜(ARC)を有する半導体装置及びその方法

半導体装置(10)の製造において、エッチングされる導電性材料(16)上のパターニング積層部は、下層にあるオルトケイ酸テトラエチル(TEOS)層(20)のパターニングに用いられるパターニングフォトレジスト層(22)を有している。TEOS層(20)は、従来より低い温度で成膜される。低温TEOS層(20)は、有機反射防止膜(ARC)(18)上に設けられ、有機反射防止膜は、導電層(16)上に設けられる。低温TEOS層(20)は、有機ARC(18)とフォトレジスト(22)との間の接着を提供し、低い欠陥性を有し、ハードマスクとして機能し、有機ARC(18)と共に望ましくない反射を低減させる位相シフト層として機能する。  (もっと読む)

(もっと読む)

シリコン基板に凹部を異方性エッチングにより形成する方法およびプラズマエッチングシステムの使用方法

【課題】シリコン基板に異方性エッチングにより深さが大きい凹部を形成するための、簡便な方法およびプラズマエッチングシステムの使用方法を提供する。

【解決手段】反応性エッチングガスをエネルギー励起するためにプラズマを用いる。反応性エッチングガスは、連続的に流れるガスフローの成分である。凹部は、エッチング時に、上記ガスフローを中断することなく少なくとも50マイクロメートルの深さに形成される。その結果、深さの大きい凹部を製造するための簡便な方法が提供される。

(もっと読む)

半導体装置の製造方法

【課題】残渣を生じることなく、精度良くエッチング可能な半導体装置の製造方法の提供。

【解決手段】ゲート酸化膜により段差を持つポリシリコン膜7を積層後、フォトレジスト6を全面に塗布し、パターン形成せず段差が見えるまでフォトレジストをアッシングする。そのあとRIEにより段差部のエッチングを行い、段差を緩和する。この後、フォトレジストをパターンしSiO2に対する選択比の高いHBrでエッチングを行うことにより、残渣を生じないエッチングができる。

(もっと読む)

プラズマプロセス用装置

【技術課題】 基板に損傷や表面汚染を与えることなく、エッチングや成膜が行え、チャンバや電極等の構造は同一であるにも拘らず、導入するガスやプラズマ励起周波数を変えることにより、エッチングや成膜にも応用可能であり、生産性に優れるとともに、低価格で高性能なプラズマプロセス用装置を提供すること。

【解決手段】 容器内105に対向するように設けられ夫々平板状に形成された第1及び第2電極102,104と、プラズマに対して安定な材料から成り第1電極102上を覆うように設けられる保護部材101と、第2電極104上に被処理物103を取り付けるための保持手段と、第1電極102に接続される第1の高周波電源111と、第2電極104に接続される第2の高周波電源110と、容器105内に所望のガスを導入するためのガス供給手段とを少くとも備え、第1の高周波電源の周波数が前記第2の高周波電源の周波数より高いことを特徴とする。

(もっと読む)

多結晶シリコン薄膜の平坦化方法

【課題】 多結晶シリコン薄膜の表面に形成された突起を容易且つ確実に除去することができる多結晶シリコン薄膜の平坦化方法を提供することを目的とする。

【解決手段】 多結晶シリコン薄膜を炭素(C)とフッ素(F)と水素(H)とを少なくとも含有するガスのプラズマに曝すことにより突起を除去して多結晶シリコン薄膜の表面を容易且つ確実に平坦化することができる。

(もっと読む)

半導体装置の製造方法

【課題】 シリル化プロセスを用いて微細なパターンの形成を可能とし、しかもシリル化部表面に形成されるSiOx 層の除去を支障なく行うことのできる、半導体装置の製造方法が提供が望まれている。

【解決手段】 下地基板20上の被パターニング層23上にレジスト層24を形成し、次にレジスト層24の所定箇所を露光し、次いでこの露光工程後のレジスト層24における未露光部分をシリル化する。続いて、露光した箇所のレジスト層24をドライ現像によって除去し、シリル化された部分に対応した積層パターン30を得る。次いで、積層パターン30からその表層部に形成されたSiOx層29を除去してレジストパターン32を形成する。その後、レジストパターン32をマスクにして被パターニング層23をエッチングする。

(もっと読む)

421 - 435 / 435

[ Back to top ]