Fターム[5F004FA01]の内容

半導体のドライエッチング (64,834) | エッチング工程前後の処理 (659) | 加熱処理 (106)

Fターム[5F004FA01]に分類される特許

41 - 60 / 106

低誘電率シリカ系被膜のダメージ修復方法および該方法により修復された低誘電率シリカ系被膜

【課題】 低誘電率シリカ系被膜のエッチング加工時に発生するシリカ系変性物やアッシング加工時に発生するレジスト分解物などの残渣除去、あるいはCMP加工時に発生する研磨屑などの残渣除去を目的として使用される洗浄液によって化学的なダメージを受けた低誘電率シリカ系被膜を修復する方法に関する。

【手段】 化学的なダメージを受けた低誘電率シリカ系被膜を有する基板またはデバイスを容器内に収納し、さらに該容器内に過熱水蒸気を導入して前記シリカ系被膜を加熱処理することを特徴とする低誘電率シリカ系被膜のダメージ修復方法および該方法により修復された低誘電率シリカ系被膜。

(もっと読む)

エッチング方法及び記録媒体

【課題】深さDと開口幅Wとの比D/Wが大きい溝の内面に形成されたシリコン酸化膜を効率よくエッチングする。

【解決手段】基板Wの表面のシリコン酸化膜103をエッチングする方法であって、シリコン酸化膜103の表面に、フッ化水素ガス及びアンモニアガスを含む混合ガスを供給し、シリコン酸化膜103と混合ガスとを化学反応させ、シリコン酸化膜103を変質させて反応生成物106を生成させる変質工程と、反応生成物106を加熱して除去する加熱工程とを有し、変質工程において、シリコン酸化膜103の温度を50℃以上にする。

(もっと読む)

三次元微細加工方法及び三次元微細構造

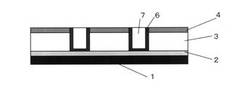

【課題】高密度かつ複雑な三次元微細構造を基板の表面に形成可能な三次元微細加工方法を提供する。

【解決手段】第1工程では、真空中でIII−V族化合物半導体基板1の表面に電子ビームを照射することにより、当該基板1の表面の自然酸化膜2を化学的に安定なIII族酸化物3に置換させ、改質マスク部3を周期的に形成する。第2工程では、真空中で前記基板1を昇温させることにより、前記改質マスク部3以外の部分の前記自然酸化膜2を脱離させて基板表面を露出させる。第3工程では、真空にV族原料を供給した環境下で前記基板1を所定温度で加熱することで、前記基板表面の露出部分からIII族原子を優先的に剥離させて前記改質マスク部3上をホッピングさせ、当該露出部分に窪み4を形成する。第4工程では、固体成長原料を用いた分子線エピタキシャル成長法を行うことで、前記窪み4の部分にIII−V族化合物半導体結晶5を選択成長させる。

(もっと読む)

化合物半導体デバイスおよびその製造方法

【課題】化合物半導体表面にプラズマプロセスによるダメージを与えることなく、化合物半導体と金属電極との接触抵抗を低減し、両者の接触部におけるオーミック特性を改善することができる化合物半導体デバイスの製造方法を提供する。

【解決手段】塩素ガスとハロゲンガスとから成ると共にこの塩素ガスを標準状態で0.05〜10.0%の体積の割合で含む混合ガスにより、プラズマを生成する。そして、n型GaN層103を、このn型GaN層103に含まれる元素の塩化物の沸点以上の温度に加熱すると共に、上記プラズマ中のラジカルを、上記n型GaN層103における金属電極104と接する表面に接触させて、このn型GaN層103の表面を加工する。

(もっと読む)

アッシャ装置及び半導体製造方法

【課題】ポッピング現象の発生を抑制し、基板の搬送を効率的にすることができるアッシャ装置及び半導体の製造方法を提供する。

【解決手段】アッシャ装置10は、ウエハ600のベーキングを行うロードロックチャンバ250と、ウエハ600をロードロックチャンバ250に搬送するカセットトランスファーユニット110と、ベーキングされたウエハ600のアッシング処理を行うプロセスチャンバ410と、ウエハ600を搬送するトランスファーチャンバ310とを有し、ロードロックチャンバ250は、真空引きがなされるとともにウエハ600のベーキング処理を開始し、ベーキング処理時に基板にポッピングが生じない程度の温度でウエハ600をベーキングする。

(もっと読む)

基板処理装置及び基板処理方法並びに記憶媒体

【課題】ウエハに対して熱処理モジュールにて複数回の熱処理を行うにあたって、支持部材の支持に起因したウエハの損傷を防止することのできる基板処理装置を提供する。

【解決手段】基板処理装置は、半導体ウエハの処理レシピにおける処理条件と半導体ウエハの向きとを対応付けて設定するためのレシピ設定画面を備えたレシピ設定部を設けており、このレシピ設定画面上にて半導体ウエハの向きを設定し、位置合わせモジュールにおいて前記レシピ設定画面上で設定した向きになるように半導体ウエハの向きを合わせている。このような構成にすることで、熱処理モジュールで行われる熱処理では熱処理毎に半導体ウエハの裏面を支持部材により支持する部位を異ならせることができる。

(もっと読む)

プラズマ処理装置およびプラズマ処理方法

【課題】真空処理容器内におけるパーティクルの落下を低減し、半導体基板の製品歩留まりの低下を低減するプラズマ処理装置およびプラズマ処理方法を提供する。

【解決手段】

真空処理容器内に配置され、マイクロ波を吸収し発熱、昇温するマイクロ波吸収発熱体を有するプラズマ処理装置であって、マイクロ波を使用する真空処理容器内での昇華物再付着防止のため、真空処理容器内部にマイクロ波吸収発熱体を設け、プラズマ生成用のマイクロ波発振器を使用し、第1の処理工程でプラズマを励起せず、マイクロ波吸収発熱体を加熱し、第2の処理工程で被処理基板を挿入し、通常のプラズマ処理を行う。

(もっと読む)

半導体製造装置、半導体装置の製造方法及び記憶媒体

【課題】有機系の低誘電率膜であるシリコン、炭素、水素及び酸素を含む膜に対してエッチング及びアッシングをプラズマにより行った後に、低誘電率膜の電気的特性を回復させる処理を行える半導体製造装置を提供する。

【解決手段】アッシング処理を行ったチャンバー内で、基板を50℃〜300℃程度に加熱すると共に、C、H、OのみからなるDPM(ジピバロイルメタン、(CH3)3CCOCH2COC(CH3)3)ガスを基板に供給して回復処理を行う。

(もっと読む)

半導体装置の製造方法、半導体装置の製造装置及び記憶媒体

【課題】層間絶縁膜にプラズマエッチングによりビアホール等の接続用ホールを形成するにあたり、接続用ホールの配列密度の大小に係らず均一性の高いエッチングを行うことの可能な半導体装置の製造方法等を提供する。

【解決手段】

本発明に係る半導体装置の製造方法は、基板上の層間絶縁膜10上にパターンマスク15を含む上層膜16を形成し、次いで層間絶縁膜10の表面が露出した状態で基板に脱水処理用のガスを供給して層間絶縁膜10から水分を除去し、続いて層間絶縁膜10をエッチングして、電気的接続部が埋め込まれる接続用ホールを形成する。

(もっと読む)

面発光レーザアレイ、光走査装置、画像形成装置、光伝送モジュール及び光伝送システム

【課題】複数の発光部がいずれも高パワーのレーザ光を出力する。

【解決手段】2次元配列されている複数の発光部における各発光部の間、及び複数の発光部を取り囲む領域に、−Z側の面の全面が半導体積層体の下部反射鏡103に接する金属膜110を放熱部材として形成する。これにより、各発光部で発生する熱は、金属膜110を介して面発光レーザアレイ100の周辺部へすみやかに放熱され、発光部間の熱干渉を従来に比べて小さくすることができる。そこで、複数の発光部がいずれも高パワーのレーザ光を出力することが可能となる。

(もっと読む)

アッシング方法及びその装置

【課題】フォトレジストを除去するアッシング工程において、レジスト残渣を低減し、アッシング時間を短縮することのできる簡便かつ実用的な手段を提供する。

【解決手段】真空処理容器内においてパターンニングされたレジスト膜をマスクとして用いて低誘電率膜の一部をプラズマエッチングした後に、前記真空処理容器内において、前記レジスト膜を除去する、被処理基板のアッシング方法において、前記アッシングに先立って、前記被処理基板を80℃から200℃までの温度範囲内で保持し、所定時間アッシングする前処理アッシングを行う。

(もっと読む)

プラズマ処理装置

【課題】処理室内に温度計を設置しなくても、処理室内の昇温状態を簡便に判別できる機能を搭載したプラズマ処理装置を提供する。

【解決手段】被処理体をプラズマ処理する処理室と、前記処理室にガスを供給する手段と、前記処理室を減圧する排気手段と、プラズマ生成用高周波電源と、被処理体を載置する載置電極とを有するプラズマ処理装置において、前記プラズマ処理の前に実施される昇温放電の終点を判定するための、昇温放電終点判定用プラズマ発光モニタ及び昇温放電終点判定手段を有している。

(もっと読む)

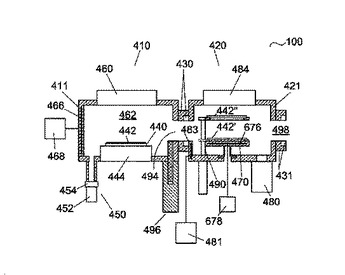

高スループットの非プラズマ処理を行う処理システム及び方法

高スループットの非プラズマ処理を行う装置及び方法の実施例(100)が一般的に本明細書において記載されている。他の実施例も記載及び主張されている。  (もっと読む)

(もっと読む)

表面処理方法及びその装置

【課題】 微細な接続孔内等に発生した酸化膜をドライエッチングにより効率良く除去できる表面処理方法及びその装置を提供する。

【解決手段】 表面に酸化膜が発生している被処理体Wは、処理容器10内に搬入され、該処理容器内は真空に維持され、N2 とH2 との混合ガスがプラズマ発生部30に導入され、プラズマ化され、それぞれの活性ガス種が形成される。活性化ガス種は被処理体に向けてフローされ、これにNF3 ガスが添加され、活性化されたガスが形成される。被処理体は所定温度以下に冷却手段22により冷却され、活性化されたNF3 ガスに曝され、該ガスと反応し、酸化膜は変質して反応膜が被処理体Wの表面に形成される。N2 、H2 及びNF3 ガスの供給が停止され、加熱手段19で被処理体は所定の温度に加熱され、反応膜が昇華して除去される。

(もっと読む)

NH3−NF3化学による酸化物エッチング

【課題】半導体基板上の種々の酸化物を選択的に除去するための装置および方法を提供する。

【解決手段】エッチングガス混合物を使用して所望の除去レートで基板401上の酸化物402,403,404を選択的に除去するため、該エッチングガス混合物は第1のガスおよび第2のガスを備え、該第1のガスおよび第2のガスの比は該所望の除去レートによって決定される。例えば第1のガスがアンモニア(NH3)であり、前記第2のガスが三フッ化窒素(NF3)であり、又アンモニアおよび三フッ化窒素の比が約10:1〜約20:1である。

(もっと読む)

半導体装置の製造方法

【課題】ボンディングパッドやヒューズ窓の形成に際して、MISFETの特性の劣化を抑制する。

【解決手段】半導体装置の製造方法は、半導体基板の上部に、MISFETに接続された配線15を形成するステップと、配線15上にパッシベーション膜16を形成するステップと、パッシベーション膜16をエッチングし、配線15の所定部分を露出する開口18を形成するステップと、開口18から露出した配線15を含む半導体基板を、H2ガス雰囲気中でアニールするステップと、を有する。配線15は、順次に積層された、バリアメタル層12、メタル層13、及び、キャップメタル層14を含む。

(もっと読む)

パターン形成方法、および半導体装置の製造方法

【課題】 微細化への対応が可能で、かつプラズマダメージが生じにくいパターン形成方法および半導体装置の製造方法を提供する。

【解決手段】 パターン形成方法は、被処理体上に第1の線幅を有する初期パターンが形成されたシリコン表面を、プラズマ処理装置の処理室内でプラズマ酸化処理し、初期パターンの表面にシリコン酸化膜を形成する表面酸化工程と、シリコン酸化膜を除去する酸化膜除去工程と、を繰り返し行なうことにより、被処理体上に、第1の線幅に比べ微細な第2の線幅を持つ目的のパターンを形成する。

(もっと読む)

ポリシリコン膜の形成方法

【課題】 レーザアニール法を大きく変更することなく特性バラツキを解消することが可能なポリシリコン膜の形成方法を提供する。

【解決手段】 アモルファスシリコン膜2を堆積したガラス基板1を相対移動させながらパルスレーザビームを照射することによってレーザアニールを行う。アニール工程の後、プラズマ処理によりレジストを除去するレジスト除去工程(アッシング)を行う。レジスト除去工程におけるプロセス時間を、レジスト除去開始からレジスト除去終了までの時間の1.5倍以上とする。

(もっと読む)

シリコン基板の粗面化方法および光起電力装置の製造方法

【課題】従来の方法では困難だった15cm角程度あるいはそれ以上の大面積基板を対象にしても、シリコン基板に均一な凹凸を再現性良く、低コストで形成すること。

【解決手段】有機金属溶液あるいは有機金属の分散液を基板にインクジェット法でドット状に塗布する工程と、上記基板を乾燥する工程と、上記基板の表面にプラズマを照射する工程と、上記基板をエッチング処理する工程とを備えたシリコン基板の粗面化方法である。

(もっと読む)

熱プロセスによってエッチングされた基板からハロゲン残渣を除去するための統合された方法

【課題】 基板から揮発性残渣を除去するための方法及びシステムの提供。

【解決手段】 一実施形態において、基板上でハロゲン処理プロセスを行いつつ、揮発性残渣除去プロセスが、システム内のエンルートで行われる。揮発性残渣除去プロセスは、ハロゲン処理チャンバとFOUP以外のシステム内で行われる。一実施形態において、基板から揮発性残渣を除去する方法は、真空気密プラットフォームを持つ処理システムを準備するステップと、プラットフォームの処理チャンバ内で基板をハロゲンを含む化学で処理するステップと、処理された基板をプラットフォーム内で処理して、処理された基板から揮発性残渣を放出させるステップと、を含む。

(もっと読む)

41 - 60 / 106

[ Back to top ]