Fターム[5F005AF02]の内容

Fターム[5F005AF02]に分類される特許

41 - 60 / 68

光学制御炭化ケイ素および関連ワイドバンドギャップトランジスタおよびサイリスタ

光活性材料を用いて、電源エレクトロニクスデバイスおよび回路の光制御に影響を与えるために従来法に対する大きな性能利点を有する電源デバイスおよび回路を作成する。浅いドナーをホウ素関連D−センターで補償することにより炭化ケイ素光活性材料を形成する。生成する材料はn型であることもp型であることもあるが、ポリタイプ毎に異なる、D−センターからの光励起電子が伝導バンド末端に近い状態となることが可能となるのに必要な閾値エネルギーよりも過剰な光子エネルギーを有する電磁放射線で照射するとき、その中に持続的光伝導性を誘導する能力により、他の材料と区別される。  (もっと読む)

(もっと読む)

発光素子アレイ、発光装置および画像形成装置

【課題】 少ない駆動用ICで時分割駆動することができる発光素子アレイおよびそれを用いた小型な発光装置ならびにその発光装置を備える画像形成装置を提供する。

【解決手段】 発光ダイオードDとスイッチ用サイリスタSSを並列接続したn(nは2以上の整数)個スイッチデバイスSと、前記スイッチ用サイリスタSSのゲート電極gに個別に接続されるn本の信号伝送路GHと、前記n本の信号伝送路GHのうちのいずれか1つとゲート電極hが接続される複数の発光用サイリスタTとを含んで発光素子アレイチップ1を構成する。スイッチデバイスSのアノードa,cに共通のセレクト信号(ハイレベル)が入力されている発光素子アレイチップ1を発光させることができるので、発光信号(ハイレベル)およびゲート信号(ローレベル)を複数の発光素子アレイチップ1間で共用する時分割駆動が実現できる。

(もっと読む)

圧接型半導体装置およびその製造方法

【課題】本発明は、圧接型半導体装置に組み込む際に付着していた異物を発見しやすくし、より容易に取り除くことができる半導体素子およびその製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体素子は、第1の導電型の第1の半導体層と、前記第1の半導体層の所定の領域上に積層された第2の導電型の第2の半導体層と、前記第1の半導体層上に形成された第1の電極層と、前記第2の半導体層上に形成された第2の電極層と、前記第1の電極層上に形成された絶縁層と、前記絶縁層および前記第2の電極層の上に貼り合わされた導電性シートとを備えたことを特徴とする。

(もっと読む)

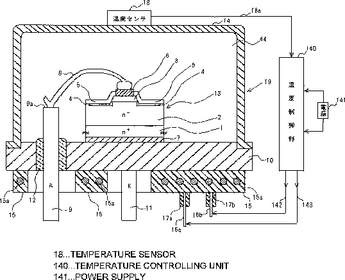

電力変換装置およびワイドギャップバイポーラ半導体素子の駆動方法

【課題】ワイドギャップバイポーラ半導体素子を高信頼性かつ低損失で駆動でき、可制御電流を大きくできる電力変換装置を提供する。

【解決手段】この電力変換装置では、SiC−GTOサイリスタ1の稼動に先立ち、温度上昇用n型MOSFET11のゲート13に信号を印可してオンさせ、電源14 → アノード端子2 → ゲート端子4 → 抵抗12 → 温度上昇用n型MOSFET11 → 電源14の経路で温度上昇用電流(加熱電流)として約40Aの電流を流す。上記温度上昇用電流により、SiC−GTOサイリスタ1の温度を上昇させる。これにより、サイリスタ1の稼動により積層欠陥が増大したとしても、オン電圧の増大や最小ゲート点弧電流の増大、ターンオン時間の増大およびオフ時の電流の不均衡の増大などの劣化現象を抑制できる。

(もっと読む)

半導体素子

【課題】本発明は、カソード電極とゲート電極の間に生じるリーク電流を低減することにより、高信頼性のスイッチング動作を実現する半導体素子およびその製造方法を提供することを目的とする。

【解決手段】本発明の1つの態様による半導体素子は、所定の積層領域と非積層領域を含む第1の導電型の第1の半導体層と、前記第1の半導体層の前記積層領域上に積層された第2の導電型の第2の半導体層と、前記第1の半導体層の前記非積層領域上に形成された第1の電極層と、前記第2の半導体層上に形成された第2の電極層と、前記第1および第2の半導体層のそれぞれの表面を連続的に接続する傾斜面上に、前記第1および第2の電極層から離間して形成された絶縁層とを備え、前記絶縁層と前記第1の電極層の間および該絶縁層と前記第2の電極層の間の少なくとも一方に、凹部が形成されたことを特徴とする。

(もっと読む)

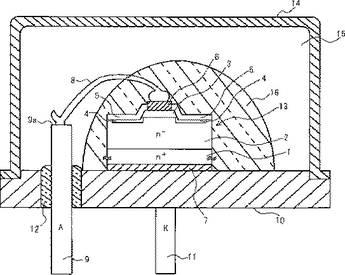

電流抑制層付き静電誘導サイリスタ、電流抑制層付き静電誘導サイリスタの保護回路及びパルス発生回路

【課題】負荷短絡時に過電流を抑制し、ターンオフ時間を短縮する電流抑制層付き静電誘導サイリスタを提供する。

【解決手段】高抵抗半導体層1と、高抵抗半導体層1の第1表面に配置されたカソード領域7と、高抵抗半導体層1の第2表面に配置されたアノード領域6と、高抵抗半導体層1中のカソード領域7近傍に埋め込まれて形成されたゲート領域2と、ゲート領域2に隣接して配置された電流抑制層3と、ゲート領域2及び電流抑制層3と、7カソード領域との間に配置されたエピタキシャル成長層8と、カソード領域7にオーミック接触するカソード電極5と、6アノード領域にオーミック接触するアノード電極4とを備える電流抑制層付き静電誘導サイリスタ。

(もっと読む)

絶縁ゲート型サイリスタ

【課題】

オン抵抗が低く、ゲートターンオフの可能な絶縁ゲート型サイリスタを提供する。

【解決手段】

絶縁ゲート型サイリスタは、第1導電型、高不純物濃度の第1電流端子半導体領域と、第1電流端子半導体領域上に形成された、第1導電型と逆導電型の第2導電型、低不純物濃度の第1ベース半導体領域と、第1ベース半導体領域上に形成された、第1導電型、低不純物濃度の第2ベース半導体領域と、第2ベース半導体領域上に形成された、第2導電型、高不純物濃度の第2電流端子半導体領域と、第2電流端子半導体領域表面から第1ベース半導体領域に向かう方向で、第2電流端子半導体領域を貫通し、第2ベース半導体領域に入り、その厚さの一部を残すように形成されたトレンチと、トレンチ内に形成された絶縁ゲート電極構造と、を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】サイリスタを構成する一部の領域を積層構造とすることで、素子面積の縮小化を図るとともにパンチスルー耐性の向上を図ることを可能とする。

【解決手段】第1伝導型の第1領域(第1p型領域p1)と、前記第1伝導型とは逆伝導の第2伝導型の第2領域(第1n型領域n1)と、第1伝導型の第3領域(第2p型領域p2)と、第2伝導型の第4領域(第2n型領域n2)とが順に接合されたサイリスタを有するとともに、前記第3領域にゲート電極23を有する半導体装置1において、前記第2領域(第1n型領域n1)は半導体基体(半導体基板21)に形成され、前記第2領域上に前記第1領域(第1p型領域p1)が形成されているものである。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】pnpn接合のサイリスタ構成を有する半導体装置において、同一伝導型に挟まれた異伝導型の領域中に再結合中心となる領域を形成して少数キャリアを再結合させることで、ライフタイムを短くし、onからoffへのスイッチング速度の高速化を図る。

【解決手段】第1伝導型(n型)の第1領域(第1p型領域)p1と、第2伝導型(p型)の第2領域(第1n型領域)n1と、第1伝導型の第3領域(第2p型領域)p2と、第2伝導型の第4領域(第2n型領域)n2とが順に接合されてなるサイリスタを有し、第2領域n1および第3領域p2のいずれか一方の領域にゲート絶縁膜12を介してゲート電極13が形成されている半導体装置1において、第2領域n1および第3領域p2のうちゲート電極13が形成されていない領域中にキャリアの再結合中心となる欠陥領域21が形成されているものである。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】スイッチング速度、とくにオン状態からオフ状態への高速でのスイッチングが可能なサイリスタ構成の半導体装置、さらにはこのような半導体装置の駆動方法および製造方法を提供する。

【解決手段】p型領域p1、n型領域n1、p型領域p2、およびn型領域n2がこの順に接して設けられた半導体層101と、両端部に配置されたp型領域p1に接続されたアノード電極Aと、n型領域n1に接続されたカソード電極K電極と、中央に配置されたp型領域p2に接続されたゲート電極G1,G2とを備えた半導体装置1において、ゲート電極は、p型領域p2を構成する半導体層101部分を挟んで対向配置されている。

(もっと読む)

半導体装置、半導体装置の駆動方法、および半導体装置の製造方法

【課題】スイッチング速度、とくにオン状態からオフ状態への高速でのスイッチングが可能なサイリスタ構成の半導体装置、さらにはこのような半導体装置の駆動方法および製造方法を提供する。

【解決手段】第1のp型領域p1、第1のn型領域n1、第2のp型領域p2、および第2のn型領域n2がこの順に接して設けられた半導体層101、第1のp型領域p1に接続されたアノード電極Aと、第2のn型領域n2に接続されたカソード電極Kと、第1のn型領域n1と第2のp型領域p2とに、それぞれ独立して制御可能に接続されたゲート電極Gn1,Gp2とを備えたことを特徴とする半導体装置。

(もっと読む)

電界効果トランジスタおよびサイリスタ

【課題】耐圧の低下を可及的に防止することを可能にする。

【解決手段】SiCからなるドレイン領域2と、ドレイン領域上に設けられたn型のSiCからなるドリフト層4と、ドリフト層の表面に設けられたn型のSiCからなるソース領域18と、ソース領域の側部のドリフト層の表面に設けられたSiCからなるチャネル領域12aと、チャネル領域上に設けられた絶縁ゲート22と、ソース領域の底部とドリフト領域との間に設けられ2種類のp型不純物を含むp型のベース領域15と、を備えている。

(もっと読む)

半導体リレー装置

【課題】光結合型PNPNスイッチを用いた半導体リレー装置において、光結合型PNPNスイッチのターンオン時の光感度を良くすると共に、ターンオフ時のノイズ耐量の低下を防止する。

【解決手段】入力信号S1により光信号L1を発生するLED2aと、この光信号L1により交流をスイッチングする光スイッチ3と、光スイッチ3をオンするための電圧を発生させるインピーダンス回路4とを備えた半導体リレー装置1aにおいて、インピーダンス回路4を抵抗とディプレッション型MOSFET5の並列回路で構成し、入力信号の無い場合は、MOSFET5を短絡状態とし、入力信号が入力された場合は、LED2aの光信号L2を受けた受光素子7により、MOSFET5をオフ乃至高抵抗状態とし、光スイッチ3のターンオン時の光感度の向上と、ターンオフ時のノイズ耐量の低下防止を両立させる。

(もっと読む)

半導体リレー装置

【課題】光結合型PNPNスイッチを用いた半導体リレー装置において、光結合型PNPNスイッチのターンオン時の光感度を良くすると共に、ターンオフ時のノイズ耐量の低下を防止する。

【解決手段】入力信号S1に応じて光信号L1を発生するLED2aと、このLED2aの光信号L1を受けて交流電源をスイッチングする出力用の光スイッチ3と、この光スイッチ3をオンするための電圧をPゲートとカソード間に発生させるインピーダンス回路とを備えた半導体リレー装置1aにおいて、インピーダンス回路を外部磁界の大きさにより抵抗値を変化できる磁気抵抗素子4とし、この磁気抵抗素子4の抵抗値を磁気発生手段5で発生させる磁界により制御し、光スイッチ3のターンオン時の光感度の向上と、ターンオフ時のノイズ耐量の低下の防止を両立させる。

(もっと読む)

半導体装置

【課題】 IGBT等の半導体装置のpn接合の耐圧向上を容易に達成することが困難であった。

【解決手段】 p+型コレクタ領域8とn-型ベース領域9とp型べース領域10とn+型エミッタ領域11とを有するIGBT用半導体基板1の外周にトレンチ17を設ける。このトレンチ17はn-型ベース領域を貫通してp型コレクタ領域8に至るように形成する。トレンチ17の壁面に誘電体膜23を介してn-型ベース領域8の側面に対向し且つp+型コレクタ領域8に接続されるように導電体層24を設ける。導電体層24のフィールドプレート効果で耐圧を向上させる。

(もっと読む)

高速切替え速度を有する電源装置及びその製造方法

サイリスタ(25)及びMOSFETトランジスタ(26)が第1の電流伝導端子(A)と第2の電流導電端子(S)との間で直列接続されることによって形成される電源装置(1)。電源装置は更に、MOSFETトランジスタの絶縁ゲート電極(20)に接続され、装置をオン及びオフにするための制御電圧を受信する制御端子(G)と、オフ時の電荷の高速抽出のためにサイリスタに接続される第3の電流導電端子(B)を有する。これにより、オフにするときに、電流テイルがなく、また、オフにすることは非常に高速である。電源装置は、寄生コンポーネントを有さないので、非常に高い逆バイアス安全動作領域(RBSOA)を有する。  (もっと読む)

(もっと読む)

バイポーラ型半導体装置の順方向電圧回復方法、積層欠陥縮小方法およびバイポーラ型半導体装置

【課題】炭化珪素単結晶基板の表面から成長させた炭化珪素エピタキシャル膜の内部で通電時に電子と正孔が再結合するバイポーラ型半導体装置において、電流通電により拡大した積層欠陥面積を縮小し、増加した炭化珪素バイポーラ型半導体装置の順方向電圧を回復させる方法を提供する。

【解決手段】電流通電により積層欠陥面積が拡大し、順方向電圧が増加した炭化珪素バイポーラ型半導体装置を350℃以上の温度で加熱し、積層欠陥回復させる。

(もっと読む)

半導体装置及びその製造方法、この半導体装置を用いた電力変換装置

可制御電流が大きく、かつ低損失のパワー半導体装置を得るために、ワイドギャップ半導体を用いるバイポーラ半導体素子の温度を、ヒーターなどの加熱手段を用いて上昇させる。その温度は、ワイドギャップバイポーラ半導体素子の、温度の上昇に応じて低下するビルトイン電圧の低下量に対応する前記ワイドギャップバイポーラ半導体素子の定常損失の減少量が、前記温度の上昇に応じて増加するオン抵抗の増加量に対応する前記定常損失の増加量よりも大きくなる温度を超える温度にする。  (もっと読む)

(もっと読む)

高耐熱半導体装置

150℃以上の高温で使用するSiCなどのワイドギャップ半導体装置において、ワイドギャップ半導体素子の絶縁性を改善し、高耐電圧のワイドギャップ半導体装置を得るために、ワイドギャップ半導体素子の外面を合成高分子化合物で被覆する前記合成高分子化合物は、シロキサン(Si−O−Si結合体)による橋かけ構造を有する1種以上の有機珪素ポリマーAと、シロキサンによる線状連結構造を有する1種以上の有機珪素ポリマーBとをシロキサン結合により連結させた有機珪素ポリマーC同士を、付加反応により生成される共有結合で連結させて三次元の立体構造に形成している。  (もっと読む)

(もっと読む)

高耐熱合成高分子化合物及びこれで被覆した高耐電圧半導体装置

【課題】150℃以上の高温で使用するSiCなどのワイドギャップ半導体装置において、ワイドギャップ半導体素子の絶縁性を改善し、高耐電圧のワイドギャップ半導体装置を得る。

【解決手段】ワイドギャップ半導体素子の外面を、合成高分子化合物で被覆する。この合成高分子化合物は、シロキサン(Si−O−Si結合体)による橋かけ構造を有する1種以上の有機珪素ポリマーAとシロキサンによる線状連結構造を有する1種以上の有機珪素ポリマーBとをシロキサン結合により連結させた有機珪素ポリマーC同士を、付加反応により生成される共有結合で連結させて三次元の立体構造に形成している。この合成高分子化合物に高い熱伝導性を有する絶縁性セラミックスの微粒子を混合し、熱伝導率を高くしている。

(もっと読む)

41 - 60 / 68

[ Back to top ]