Fターム[5F005AF02]の内容

Fターム[5F005AF02]に分類される特許

21 - 40 / 68

半導体装置の製造方法

【課題】逆回復時のdV/dtの増加を抑制し、逆回復時の電圧電流波形の振動を抑制し、高速・低損失特性とソフトリカバリー特性の両者を同時に向上させる半導体装置の製造方法を提供すること。

【解決手段】リンを含むn型で高比抵抗のFZのバルクウェハ300にて通常のプロセス処理を行い、一方の表面にpアノード層301、アノード電極302を形成する。その後、プロトン等の軽イオン照射303を行う。照射後、裏面から所定の厚さまで、切削する。切削後、裏面の切削面305にリン等のn型不純物イオン(不純物307)のイオン注入306を行い、熱処理を行い、nカソード層308を形成し、その上にカソード電極309を形成する。

(もっと読む)

トライアック

【課題】トライアックの雷サージ特性を向上させ、信頼性の高いトライアックを提供する。

【解決手段】p層がn層を挟み込む半導体基板のp層内にn層41及び43が選択的に形成され、p層内にn層42が選択的に形成され、トライアックが形成される。その際、n層41〜43は、互いに重複しないように配置され、かつ、n層41及び42は、その平面領域がそれぞれ対称形となるように形成される。このため、サージ電圧が印加されてターンオンする初期段階において、異なる2以上の局所領域がオン状態となり、電流集中を緩和することができるので、雷サージ特性を大幅に向上させることができる。

(もっと読む)

半導体装置およびその製造方法およびその駆動方法

【課題】サイリスタ動作時に、寄生バイポーラトランジスタを作らせず、書き込みのディスターブの発生を防止して、誤書き込みを防止することを可能にするSRAM型の半導体装置とその製造方法を提供する。

【解決手段】半導体基板11に形成されたサイリスタ形成領域21を分離する素子分離領域12と、サイリスタ形成領域21に形成されていて、p型の第1領域(第1p型領域)p1と、n型の第2領域(第1n型領域)n1と、p型の第3領域(第2p型領域)p2と、n型の第4領域(第2n型領域)n2とが順に接合されたサイリスタT1、T2と、第2p型領域p2の下部に形成されたn型の第5領域(第1ウエル領域)31を有する半導体装置1において、第5領域31の底部および素子分離領域12の下部に接合するp型の第6領域(第2ウエル領域)32を有する。

(もっと読む)

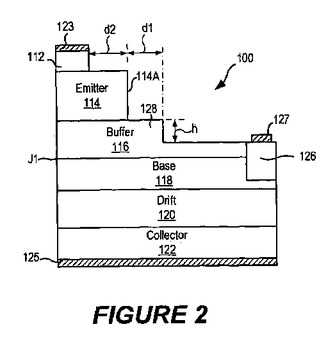

メサ構造とメサ段差を含むバッファ層とを備えた電力半導体デバイス

バイポーラ接合トランジスタが、第1の導電型を有するコレクタと、このコレクタ上の、第1の導電型を有するドリフト層と、このドリフト層上の、第1の導電型と反対の第2の導電型を有するベース層と、このベース層上の、低濃度でドープされ第1の導電型を有しベース層とp−n接合部を形成するバッファ層と、このバッファ層上の第1の導電型を有し側壁を有するエミッタメサとを含む。バッファ層は、エミッタメサの側壁の近傍でそこから横方向に間隔を置いて配置されたメサ段差を含み、エミッタメサの下のバッファ層の第1の厚さは、メサ段差外側のバッファ層の第2の厚さよりも厚い。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】エピタキシャル成長層上に形成したシリサイド層やエピタキシャル成長層と半導体基板とがショートを起こすのを防止することを可能にする。

【解決手段】半導体基板11に形成された素子分離領域14によって分離された該半導体基板11の素子形成領域12と、前記半導体基板11上に形成された絶縁膜41と、前記素子形成領域12の選択エピタキシャル成長させる領域上を含むように前記絶縁膜41に形成された開口部42と、前記開口部42内の半導体基板11の素子形成領域12より選択エピタキシャル成長により形成された半導体層15とを有することを特徴とする。

(もっと読む)

ゲートターンオフサイリスタ

【課題】メサ型のエミッタ層を有するワイドギャップ半導体のゲートターンオフサイリスタにおいて、可制御電流を大きくできるものを提供すること。

【解決手段】 n型の第1のエミッタ層、p型の第1のベース層、n型の第2のベース層、p型の第2のエミッタ層をこの順に備える。第2のベース層の表面近傍の、メサ型の第2エミッタ層と第2のベース層との接合部近傍を含むメサの底部に、p型の領域7を介在させてn型の低抵抗ゲート領域5を設ける。これにより、エミッタ層と、そのエミッタ層に近接する、ゲートが設けられるベース層との接合部の端部近傍の絶縁膜の電界を緩和する。なお、各層および各領域のn型とp型とを入れ替えても良い。

(もっと読む)

絶縁ゲート型サイリスタ

【課題】

オン抵抗が低く、ゲートターンオフの可能な絶縁ゲート型サイリスタを提供する。

【解決手段】

絶縁ゲート型サイリスタは、第1導電型、高不純物濃度の第1電流端子半導体領域と、

第1電流端子半導体領域上に形成された、第1導電型と逆導電型の第2導電型、低不純物

濃度の第1ベース半導体領域と、第1ベース半導体領域上に形成された、第1導電型、低不純物濃度の第2ベース半導体領域と、第2ベース半導体領域上に形成された、第2導電型、高不純物濃度の第2電流端子半導体領域と、第2電流端子半導体領域表面から第1ベース半導体領域に向かう方向で、第2電流端子半導体領域を貫通し、第2ベース半導体領域に入り、その厚さの一部を残すように形成されたトレンチと、トレンチ内に形成された絶縁ゲート電極構造と、を有し、トレンチが第2ベース半導体領域上部を複数の部分に分割し、分割された各部分を取り囲むように形成されている。

(もっと読む)

半導体装置及びその駆動方法

【課題】ターンオフ時間を短くできるサイリスタを有する半導体装置を提供する。

【解決手段】基板に第1導電型の第1半導体領域が形成され、その表層部に第2導電型の第2半導体領域と第2導電型の第3半導体領域(アノードAN)と第1導電型の第4半導体領域(アノードゲートAG)が、第2半導体領域の表層部に第1導電型の第5半導体領域(カソードCA)と第2導電型の第6半導体領域(カソードゲートCG)が形成され、第1及び第2半導体領域の境界から第2及び第5半導体領域の境界までの領域の第2半導体領域上にゲート絶縁膜及びゲート電極MGが、第3半導体領域に負荷素子が形成されてサイリスタSCRが構成された半導体装置において、サイリスタをオンからオフにする際に、アノードより高電位をアノードゲートに印加し、アノードとアノードゲートでサイリスタ内部に構成されるダイオードを降伏させてアノードの電位を制御して駆動する。

(もっと読む)

炭化珪素バイポーラ型半導体装置

【課題】メサ構造をもつ炭化珪素バイポーラ型半導体装置において、素子の表面付近に存在する欠陥核を起点とした積層欠陥の発生およびその面積拡大を抑制し、これにより順方向電圧の増加を抑制する。

【解決手段】第1導電型炭化珪素単結晶基板、第1導電型炭化珪素ドリフト層、第2導電型炭化珪素電荷注入層および該炭化珪素電荷注入層よりもドーピング密度が高い第2導電型の高ドーピング層が、この順序にて積層してなり、前記炭化珪素ドリフト層から前記高ドーピング層側の素子表面に至るメサ構造を有し、前記高ドーピング層の厚さが15nm〜1.5μmであり、かつ、前記高ドーピング層における最大ドーピング密度が1×1020cm-3〜2×1021cm-3であることを特徴とする炭化珪素バイポーラ型半導体装置。

(もっと読む)

pnダイオード、電気回路装置、および電力変換装置

【課題】小型,安価でオン抵抗の大きなpnダイオードを提供する。

【解決手段】このSiCpnダイオードは、約3×1013cm−2以上の電子線を照射したことで、ライフタイム制御がなされている。このライフタイム制御の結果、図1の電流電圧特性K10に示すように、このSiCpnダイオードでは、電流は約32Vから流れ出し、100A通電時のオン電圧は50Vとなった。このときの上記SiCpnダイオードのオン時の抵抗は0.5Ωである。このSiCpnダイオードの通電領域は0.4cm2であり、上記ライフタイム制御によってオン抵抗を増大させて、0.2Ωcm2にしたから、例えば、従来はダイオードと抵抗とを直列に接続して使用していた電気回路装置において、上記抵抗を省略可能となる。

(もっと読む)

半導体装置

【課題】可制御電流が大きく、低損失のパワー半導体装置に適したアセンブリ構造を提供すること。

【解決手段】金属基板125と、絶縁板126と、金属膜7とを備える。金属基板125上に、ワイドギャップ半導体層からなるバイポーラスイッチング素子20を備える。金属膜7上に、n型ワイドギャップ半導体層を含むダイオード素子13を備える。バイポーラスイッチング素子20の低電位側の主電極32は、金属基板125に直接に半田付けされている。一方、バイポーラスイッチング素子20の高電位側の主電極29は、金属膜7に配線34、7aを介して電気的に接続されている。ダイオード素子13の低電位側の主電極32は、金属膜7に直接に半田付けされている。一方、ダイオード素子13の高電位側の主電極6は、金属基板125に配線8を介して電気的に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】可制御電流が大きく、低損失のパワー半導体装置を作製すること。

【解決手段】順方向特性にビルトイン電圧を有するワイドギャップバイポーラ半導体素子を形成するように、互いに異なる導電型を有する少なくとも2層のワイドギャップ半導体層1、2、3を積層する。積層欠陥を有するワイドギャップ半導体層1、2、3に、所定の照射エネルギーのγ線、電子線または荷電粒子線を所定量照射する。

(もっと読む)

半導体装置及びその製造方法、動作方法、この半導体装置を用いた電力変換装置

【課題】可制御電流が大きく、かつ低損失のパワー半導体装置を得ること。

【解決手段】ワイドギャップ半導体を用いた、順方向特性にビルドイン電圧を有するワイドギャップバイポーラ半導体素子13を備える。ワイドギャップバイポーラ半導体素子13を収納し、ワイドギャップバイポーラ半導体素子13を外部の装置に接続するための電気接続手段7、8、9、11を有する半導体パッケージ10、14を備える。半導体パッケージ10、14内の前記ワイドギャップバイポーラ半導体素子13を50℃以上、750℃以下の温度範囲に加熱するための発熱手段15を備える。

(もっと読む)

半導体装置

【課題】 簡便な方法で電極部付近の電流集中を防いで、逆回復耐量を向上させ

ること。

【解決手段】 ライフタイムの短い調整領域10を、ソース電極4を半導体基板1内へ投影させた場合の電極端部を跨いだ領域で、かつ、基板深さ方向に位置する高濃度のp型ウェル領域20と低濃度の半導体層との境界部6を含む領域に形成する。

(もっと読む)

半導体装置及びその駆動方法

【課題】ターンオフ時間を短くできるサイリスタを有する半導体装置を提供する。

【解決手段】基板に第1導電型の第1半導体領域20が形成され、第1半導体領域の表層部に第2導電型の第2半導体領域22とアノードとなる第2導電型の第3半導体領域23とアノードゲートとなる第1導電型の第4半導体領域24が形成され、また、第2半導体領域の表層部にカソードとなる第1導電型の第5半導体領域26とカソードゲートとなる第2導電型の第6半導体領域25が形成され、第1半導体領域と第2半導体領域の境界から第2半導体領域と第5半導体領域の境界までの領域における第2半導体領域の上層にゲート絶縁膜30及びゲート電極31が形成され、第3半導体領域、第4半導体領域、第6半導体領域及び第5半導体領域に入出力用の導電層が形成されており、第3半導体領域、第1半導体領域、第2半導体領域及び第5半導体領域からサイリスタが構成されている。

(もっと読む)

SiC結晶の質を向上させる方法およびSiC半導体素子

【課題】高温アニーリングにより、キャリア捕獲中心を効果的に減少または除去するSiC層の質を向上させる方法、および該方法により作製されたSiC半導体素子を提供する。

【解決手段】(a)最初のSiC結晶層(E)における浅い表面層(A)に炭素原子(C)、珪素原子、水素原子、またはヘリウム原子をイオン注入して、注入表面層に余剰な格子間炭素原子を導入する工程と、(b)当該層を加熱することにより、注入表面層(A)からバルク層(E)へ格子間炭素原子(C)を拡散させるとともにバルク層における電気的に活性な点欠陥を不活性化する工程と、を含む、幾つかのキャリア捕獲中心を除去または減少することによりSiC層の質を向上させる方法および該方法により作製された半導体素子。上記工程の後、表面層(A)を、エッチングするかまたは機械的に除去してもよい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】移動度を高めることで、オンからオフへのスイッチング速度を高速化することを可能とする。

【解決手段】第1伝導型の第1領域(第1p型領域p1)と、前記第1伝導型とは逆伝導の第2伝導型の第2領域(第1n型領域n1)と、第1伝導型の第3領域(第2p型領域p2)と、第2伝導型の第4領域(第2n型領域n2)とが順に接合されたもので、該第3領域(第2p型領域p2)にゲート(ゲート電極14等)が形成されたサイリスタ2を有する半導体装置1であって、前記サイリスタ2の第1領域乃至第4領域は、シリコンゲルマニウム領域もしくはゲルマニウム領域に形成されていることを特徴とするものである。

(もっと読む)

半導体装置およびその駆動方法

【課題】ゲート電極からのバイアス効果を大きくするとともに、オンからオフへのスイッチング速度を高速化することを可能とする。

【解決手段】第1伝導型の第1領域(第1p型領域p1)と、前記第1伝導型とは逆伝導の第2伝導型の第2領域(第1n型領域n1)と、第1伝導型の第3領域(第2p型領域p2)と、第2伝導型の第4領域(第2n型領域n2)とが順に接合されたサイリスタ2と、前記第3領域に形成されたゲート電極13と、前記第3領域が形成されるもので前記バルク半導体基板10に形成された第2伝導型のウエル領域11とを有する半導体装置1であって、前記サイリスタ2の第1領域側に第1電圧が印加され、前記サイリスタ2の第4領域側に前記第1電圧よりも高い第2電圧が印加され、前記ウエル領域11に前記第1電圧よりも高い電圧もしくは前記第1電圧と同等の電圧が印加されることを特徴とする。

(もっと読む)

半導体装置およびその駆動方法

【課題】バルク半導体基板を用い、選択セルと非選択セルとを区別し、選択セルのみをオフさせて、オンからオフへのSRAMメモリセル用サイリスタのスイッチング速度を高速化させることを可能とする。

【解決手段】バルク半導体基板10に、ゲート電極13が形成されたサイリスタ3と、このサイリスタ3に接続された電界効果トランジスタ4とからなる記憶素子2を複数有する半導体装置1であって、電界効果トランジスタ4のカソード側にビット線BLが接続され、選択された記憶素子2(2a)のオフ動作時に、選択された記憶素子2aのサイリスタ3の第1領域p1側に第1電圧が印加され、その記憶素子2aの電界効果トランジスタ4のカソード側に第1電圧よりも高い第2電圧が印加され、その記憶素子2aと同じビット線BLに接続する非選択の記憶素子2bの電界効果トランジスタ4に形成されたワード線WLに第1電圧よりも低い電圧が印加される特徴を有する。

(もっと読む)

双方向サイリスタ

【課題】双方向サイリスタの感度の向上と誤動作の防止との両方を良好に達成することが困難であった。

【解決手段】双方向サイリスタを構成するために、半導体基板1に第1、第2、第3及び第4のN型半導体領域N1、N2、N3、N4と第1及び第2のP形半導体領域P1、P2とを設ける。半導体基板1の一方の表面2に第1の主電極T1とゲ−ト電極Gとを配置する。半導体基板1の他方の主面3に第2の主電極T2を設ける。第4のN形半導体領域N4に浅く拡散された第1の部分N4aと深く拡散された第2の部分N4bとを設ける。第2の部分N4bを第1及び第2の主サイリスタの中心から遠い位置に配置する。

(もっと読む)

21 - 40 / 68

[ Back to top ]