Fターム[5F005GA04]の内容

Fターム[5F005GA04]に分類される特許

1 - 11 / 11

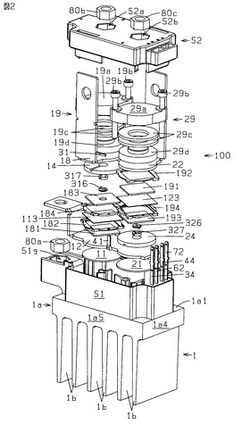

圧接型大電力用サイリスタモジュールおよびその製造方法ならびにその使用方法

【課題】水冷設備を準備できない使用環境でサイリスタチップを冷却する。

【解決手段】サイリスタチップ113,123を具備する圧接型大電力用サイリスタモジュール100において、複数の放熱フィン1bを有するヒートシンク1のベース部分1aに対して絶縁板11とコモンバー12とアノードサブスペーサ181とサイリスタチップ113とカソードサブスペーサ183とカソードスペーサ14とカソード端子バー18とを圧接手段19によって上下方向に圧接し、ヒートシンク1のベース部分1aに対して絶縁板21とコモンバー12とカソードスペーサ24とカソードサブスペーサ193とサイリスタチップ123とアノードサブスペーサ191とアノード端子バー22とを圧接手段29によって上下方向に圧接した。

(もっと読む)

サイリスタ

【課題】ゲート電極の接触抵抗の値を制御できるサイリスタを提供することを目的としている。

【解決手段】第1導電型半導体基板14の一方の表面近傍に第1の第2導電型半導体領域16が形成され、第1の第2導電型半導体領域の表面近傍にカソード電極20と接合する第1導電型半導体領域17およびゲート電極21と接合する第2の第2導電型半導体領域18が形成され、第1導電型半導体基板の他方の表面近傍にアノード電極22と接合する第3の第2導電型半導体基板13が形成されたサイリスタにおいて、ゲート電極と第2の第2導電型半導体領域とが接合してオーミック接触を形成し、ゲート電極と第1の第2導電型半導体領域とが接合して非オーミック接触を形成する。

(もっと読む)

半導体装置

【課題】トライアックが形成された半導体装置の性能を向上させる。

【解決手段】トライアック形成用の半導体領域が形成された半導体基板1の表面に電極T1,G1が形成され、裏面に裏面電極が形成されている。電極T1から裏面電極へ電流を流す場合と、裏面電極から電極T1へ電流を流す場合の両方の動作モードにおいて、ゲート端子である電極G1に電極T1よりも高電位の電圧を印加することで、半導体基板1に形成されたサイリスタをターンオンする。半導体基板1の表面側には、p型半導体領域P2とそれに内包されるn型半導体領域N2とが形成され、電極T1はp型半導体領域P2とn型半導体領域N2に接し、電極G1はp型半導体領域P2のみに接する。そして、平面視において、電極G1が接する部分のp型半導体領域P2と電極T1が接する部分のp型半導体領域P2の間に、n型半導体領域N2が延在している。

(もっと読む)

バイポーラ半導体素子

【課題】制御電極による制御能力を向上できるバイポーラ半導体素子を提供する。

【解決手段】このゲートターンオフサイリスタは、隣り合う2列R1,R2のメサ型のアノードエミッタ層5の間で列方向に延在している列間の第1のコンタクトホール20Bに形成された第1のゲート端子15だけでなく、各列R1,R2の端側で各列R1,R2に沿って列方向に延在している端側の第2,第3のコンタクトホール20C,20Dに形成された第2,第3のゲート端子16,17を有する。これにより、列間の第1のゲート端子15と端側の第2,第3のゲート端子16,17とでターンオフ時の転流を分担できて、転流の不揃いを抑制できる。

(もっと読む)

半導体装置及びその製造方法

【課題】製造コストを抑えつつ、ガードリングに接するPN接合部の耐圧の向上を図る。

【解決手段】半導体基板10の表面にN−型半導体層11を形成し、その上層にP型半導体層12を形成する。P型半導体層12上には、絶縁膜13を形成する。その後、絶縁膜13からN−型半導体層11の厚さ方向の途中に至る複数の溝、即ち第1の溝17A、第2の溝17B、第3の溝17Cを形成する。これらの複数の溝は、そのうち互いに隣接する2つの溝において、電子デバイスに近い側、即ちアノード電極14に近い側の溝は、該溝よりも外側の他方の溝よりも浅く形成される。その後、第1の溝17A内、第2の溝17B内、第3の溝17C内に、絶縁材料18が充填される。その後、半導体基板10及びその上層に積層された各層からなる積層体をダイシングラインDLに沿ってダイシングする。

(もっと読む)

サイリスタ

【課題】高いゲート・カソード間耐圧を有するサイリスタを提供する。

【解決手段】第1導電型の半導体基板の第1主面には、第1導電型の不純物領域であるカソード領域と、前記カソード領域を取り囲むような第2導電型の不純物領域であるアノード領域と、前記カソード領域と前記アノード領域との間にはメサ溝部とを有し、前記半導体基板の第2主面には、第2導電型の不純物領域部であるゲート領域と、前記第1主面から前記ゲート領域まで達する深さの前記メサ溝部と、前記第1主面の前記カソード領域にはカソード金属電極、前記アノード領域にはアノード金属電極を有し、前記第2主面の前記ゲート領域上にはゲート金属電極を有することを特徴とするサイリスタであり、ゲート・カソード間距離が充分に確保できる構造であるため、ゲート・カソード間耐圧を高く確保することができる。

(もっと読む)

pnダイオード、電気回路装置、および電力変換装置

【課題】小型,安価でオン抵抗の大きなpnダイオードを提供する。

【解決手段】このSiCpnダイオードは、約3×1013cm−2以上の電子線を照射したことで、ライフタイム制御がなされている。このライフタイム制御の結果、図1の電流電圧特性K10に示すように、このSiCpnダイオードでは、電流は約32Vから流れ出し、100A通電時のオン電圧は50Vとなった。このときの上記SiCpnダイオードのオン時の抵抗は0.5Ωである。このSiCpnダイオードの通電領域は0.4cm2であり、上記ライフタイム制御によってオン抵抗を増大させて、0.2Ωcm2にしたから、例えば、従来はダイオードと抵抗とを直列に接続して使用していた電気回路装置において、上記抵抗を省略可能となる。

(もっと読む)

双方向サイリスタ

【課題】双方向サイリスタの感度の向上と誤動作の防止との両方を良好に達成することが困難であった。

【解決手段】双方向サイリスタを構成するために、半導体基板1に第1、第2、第3及び第4のN型半導体領域N1、N2、N3、N4と第1及び第2のP形半導体領域P1、P2とを設ける。半導体基板1の一方の表面2に第1の主電極T1とゲ−ト電極Gとを配置する。半導体基板1の他方の主面3に第2の主電極T2を設ける。第1の主電極に、第2のN型半導体領域N2に対向する第1の部分T1aと、第3のN型半導体領域N3に対向する第2の部分T1bと、第2及び第3モードにおけるトリガに寄与する第3の部分T1cとを設ける。第3の部分T1cを第1及び第2の主サイリスタの中心から遠い位置に配置する。

(もっと読む)

半導体装置およびその製造方法

【課題】セル面積を縮小化するとともに、サリサイドプロセスによるサイリスタを構成する領域間の短絡を防ぐことを可能とする。

【解決手段】第1伝導型の第1領域21と、第2伝導型の第2領域22と、第1伝導型の第3領域23と、第2伝導型の第4領域24とが順に接合されたもので、第3領域23が半導体領域(半導体基板11)に形成されたサイリスタ20、および第3領域23上に形成されたゲート(ゲート電極32)を有する半導体装置1であって、第2領域22は第3領域23上に形成された絶縁膜40の第3領域23に達する開口部47内部に形成され、第1領域21は開口部47内の第2領域22上から絶縁膜40上の一部にかけて形成され、第1領域21上、ゲート電極32上、第4領域24上に金属シリサイド膜25、26,27が形成されていることを特徴とする。

(もっと読む)

圧接型半導体装置およびその製造方法

【課題】本発明は、圧接型半導体装置に組み込む際に付着していた異物を発見しやすくし、より容易に取り除くことができる半導体素子およびその製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体素子は、第1の導電型の第1の半導体層と、前記第1の半導体層の所定の領域上に積層された第2の導電型の第2の半導体層と、前記第1の半導体層上に形成された第1の電極層と、前記第2の半導体層上に形成された第2の電極層と、前記第1の電極層上に形成された絶縁層と、前記絶縁層および前記第2の電極層の上に貼り合わされた導電性シートとを備えたことを特徴とする。

(もっと読む)

半導体素子アレイチップのアライメントマークの構造および配置方法

【課題】検査装置による半導体素子アレイの中間部分の繰り返しパターンについて、検査の視野ごとのアライメント成功率を向上させることのできるアライメントマークの構造を提供する。

【解決手段】輝度の濃淡を明確にしやすい配線パターンを用いて、検査の視野ごとに、アライメントマークを作る。幅がW(数μm〜10μm)の通常の配線14の右側エッジに、局所的に3分の2程度の線幅にする矩形の切り欠き部16を設けた。この矩形の局所的な形状よりなる特徴を、C1とする。このような特徴C1の形状は、矩形の外に、台形または半円形とすることができる。

(もっと読む)

1 - 11 / 11

[ Back to top ]