Fターム[5F032AA37]の内容

素子分離 (28,488) | 絶縁物を用いる分離 (9,448) | 素子領域側面を絶縁物で分離するもの (8,208) | 溝内埋込み分離 (7,414) | 溝の断面形状 (2,101) | 垂直側面を有するもの (1,970) | 溝底部にテーパのあるもの (77)

Fターム[5F032AA37]に分類される特許

1 - 20 / 77

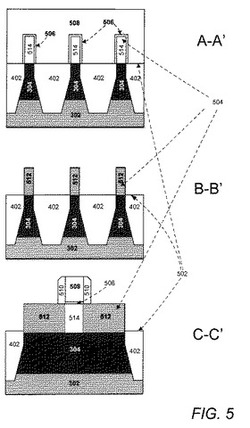

バッファ付きフィンFETデバイス

【課題】フィンFETデバイスのロバストネスを向上させる。

【解決手段】トランジスタデバイスであって、半導体基板と、半導体基板に形成されたバッファ付き垂直フィン状構造であって、垂直フィン状構造は、ドレーン領域とソース領域512との間にチャンネル領域514を含む上位の半導体層と、上位の半導体層の下のバッファ領域304であって、第1のドーピング極性を有するバッファ領域と、第1のドーピング極性と反対である第2のドーピング極性を有するウェル領域302の少なくとも一部分と、バッファ領域とウェル領域との間の少なくとも1つのp−n接合であって、該垂直フィン状構造の水平断面を少なくとも部分的にカバーする少なくとも1つのp−n接合とを含むバッファ付き垂直フィン状構造と、上位の半導体層のチャンネル領域をおおい形成されたゲートスタックとを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】製造プロセスが複雑になるといったことを防ぎつつ、n型及びp型MOSトランジスタについて両方の性能を向上させた半導体装置を提供する。

【解決手段】半導体基板1の面内に、n型MOSトランジスタと、p型MOSトランジスタとを備える半導体装置であって、n型MOS型トランジスタが形成される第1の拡散層2aの間を絶縁分離する第1の絶縁層3aと、p型MOS型トランジスタが形成される第2の拡散層2cの間を絶縁分離する第2の絶縁層3bとを備え、第1の絶縁層3aは、半導体基板1の表層に形成された第1の溝部4aに、シリコン窒化膜5と、このシリコン窒化膜5の上にシリコン酸化膜6とを埋め込むことによって形成され、第2の絶縁層3bは、半導体基板1の表層に第1の溝部4aよりも幅広となるように形成された第2の溝部4bに、シリコン酸化膜6を埋め込むことによって形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離溝を塗布系の材料で埋め込む素子分離構造において、熱処理時に素子分離溝に大きな応力が作用することを防止する。

【解決手段】メモリセル領域に形成され第1の開口幅を有する第1の素子分離溝と、周辺回路領域に形成され第1の開口幅より大きい第2の開口幅を有する第2の素子分離溝と、第1の素子分離溝の内面に形成された第1の酸化膜と、第1の酸化膜上に形成されて前記第1の素子分離溝内に埋め込まれた第1の塗布型酸化膜と、第2の素子分離溝の内面のうちの側部に形成された第2の酸化膜と、第2の素子分離溝内の内面のうちの底部上に形成された第3の酸化膜と、第3の酸化膜上に形成されて第2の素子分離溝内に埋め込まれた第2の塗布型酸化膜とを備えた。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板の結晶性の悪化を招くことなく、素子分離トレンチの幅を小さくできる半導体装置の製造方法を提供する。

【解決手段】マスク用窒化膜51およびパッド酸化膜52からなるハードマスクを用いて、シリコン基板2がエッチングされることにより、素子分離トレンチ21が形成される。素子分離トレンチ21の内面に熱酸化法によりライナー酸化膜22が形成される。続いて、半導体基板2を窒素雰囲気中に配置して、半導体基板2が熱処理される。熱処理後に、エッチングにより、ライナー酸化膜22が薄膜化される。そして、HDP−CVD法により、絶縁物23が素子分離トレンチ21内に埋め込まれる。

(もっと読む)

半導体装置とその製造方法

【課題】下側半導体層と埋込み絶縁層と上側半導体層が積層した積層体を有する半導体装置の耐圧を向上させることを目的としている。

【解決手段】半導体装置10は、下側半導体層20と埋込み絶縁層30と上側半導体層40が積層したSOI基板50を有する。下側半導体層20の埋込み絶縁層30と接する面の一部に凹部66が形成されている。凹部66内の比誘電率は、下側半導体層20の比誘電率よりも低い。

(もっと読む)

シングルゲートフィンFET及びその製造方法

【課題】新規なFinFET構造及びその製造方法を提供する。

【解決手段】シングルゲートフィンFET構造100は、2つの拡大された頭部、及び当該拡大された頭部と下層の超薄型ボディとを連結する2つの徐々に細くなる首部を有するアクティブフィン構造を含む。2つのソース/ドレイン領域102,104が、2つの拡大された頭部にそれぞれドープされる。絶縁領域26が、2つのソース/ドレイン領域の間に挿入される。溝分離構造24が、音叉形状のフィン構造の一方の側に配置される。片面サイドウォールゲート電極12bが、アクティブフィン構造における、溝分離構造とは反対側の垂直なサイドウォールに配置される。

(もっと読む)

半導体装置、及び、半導体装置の製造方法

【課題】結晶欠陥の発生を抑制しながら、深い素子分離膜を形成する。

【解決手段】半導体装置100は、基板(半導体基板1)と、基板に形成され、素子形成領域4を他の領域と分離する素子分離膜2と、素子形成領域4にて基板上に形成された半導体層3と、を有する。素子分離膜2は、基板上に形成された第1絶縁膜21と、第1絶縁膜21上に形成された第2絶縁膜22と、を含む。第1絶縁膜21の底面21Aは下方に向けて膨出する凸曲面状である。

(もっと読む)

デュアルドープゲートの用途におけるプロフィル制御とN/Pローディングを改善する方法

【課題】プラズマエッチングチャンバ内でデュアルドープゲート構造をエッチングするための方法を提供する。

【解決手段】エッチングされるポリシリコンフィルムを保護するパターンを設ける工程、次いで、プラズマが点火され、保護されていないポリシリコンフィルムのほぼすべてがエッチングされる。次いで、シリコン含有ガスを導入しつつポリシリコンフィルムの残りをエッチングする。また、エッチング処理中にシリコン含有ガスを導入するよう構成されたエッチングチャンバ。

(もっと読む)

画像撮像デバイス及びその製造方法

【課題】微細で製造が容易な画像撮像デバイス及びその製造方法を提供する。

【解決手段】半導体基板2上にハードマスク材料膜を形成し、半導体基板2の上面2aにおける開口部の直下域に凹部2cを形成する。次に、ハードマスク材料膜をマスクとして撮像領域Aに不純物を注入することにより、凹部2cの直下域にp型領域4を形成する。また、処理領域Bにおいて凹部2cをさらに加工することによりトレンチ14を形成する。そして、凹部2c内及びトレンチ14内に絶縁材料を埋め込むことにより半埋込絶縁膜5及びSTI7を形成し、ハードマスク材料膜を除去する。次に、半埋込絶縁膜5及びSTI7にそれぞれ乗り上げるように電極8a及び8bを形成し、電極8a及び半埋込絶縁膜5をマスクとして撮像領域Aに不純物を注入することにより、半導体基板2におけるp型領域4に接する領域に、フォトダイオードを構成するn型領域3を形成する。

(もっと読む)

半導体装置の製造方法

【課題】SOIデバイスにおいて生じやすい基板浮遊問題やホットキャリアの問題を充分に抑制することが可能で、広く分布する部分分離絶縁膜であっても周囲の構造に対し結晶欠陥を生じさせにくい半導体装置の製造方法を提供する。

【解決手段】各MOSトランジスタTR1の間に設けられた部分分離絶縁膜5b内におよそ一定の間隔を置いて、素子としての機能を有しないダミー領域DM1を形成する。これにより、部分分離絶縁膜5b下のシリコン層3bよりも抵抗値の低いダミー領域DM1の占める割合が増加して、基板浮遊問題やホットキャリアの問題の抑制が行えるようになる。

(もっと読む)

フィン型電界効果トランジスタ

【課題】フィン型電界効果トランジスタを提供する。

【解決手段】本発明は、フィン型電界効果トランジスタの分離構造に関する。フィン型電界効果トランジスタの例は、主表面からなる基板と、基板の主表面から突出する複数のフィン構造と、フィン構造の間に位置する複数の分離構造と、からなる。各フィン構造は、変化位置により分けられる上部分と下部分からなり、この変化位置は、フィン構造の側壁と基板の主表面の角度85度のところにあり、上部分は、この基板の主表面と実質上、垂直な側壁、及び、第一幅を有する頂面を有し、下部分は、上部分の両側のテーパ型側壁、及び、第一幅より大きい第二幅を有する底部を有する。複数の分離構造は、それぞれ、基板の主表面から、変化位置上の点に延伸する。

(もっと読む)

半導体デバイスの絶縁

【課題】半導体デバイスの絶縁構造の構造、および、形成方法を提供する。

【解決手段】当該絶縁構造は、底部が最上部よりも広くなっており、半導体デバイスの大きさを調整できる。第1のエッチングプロセスが、第1のトレンチ部分226を形成するために用いられ、第2のエッチングプロセスまたは酸化工程が、第1のトレンチ部分226の下に第2のトレンチ部分228を形成するために用いられる。第2のトレンチ部分は、第1のトレンチ部分よりも広い。一形態では、下地膜222が、第1のトレンチ部分の間、第1のトレンチ部分の側壁上に形成されてもよい(この第1のトレンチ部分は、第2のエッチングプロセスの間、第1のトレンチ部分の側壁を保護する)。あるいは、他の形態では、下地膜222が、第1のトレンチ部分の側壁上に堆積されていてもよい。

(もっと読む)

半導体装置およびその製造方法

【課題】埋め込み層を有するSOI基板を従来に比して安価に、そして寸法を小さくすることができる半導体装置を提供する。

【解決手段】半導体装置は、p型のシリコン基板10の内部に部分的に形成された平板状の空洞11の内部、およびシリコン基板10の表面から空洞11に到達するように形成される膜形成用溝12の内部に形成される絶縁膜15と、空洞11および膜形成用溝12の周縁部に形成されるn型埋め込み層14と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ溝を挟んで隣接する同一の導電型の拡散層同士の間の耐圧の低下を防止できるようにする。

【解決手段】半導体基板100には、PMOS領域AとNMOS領域Bとが形成されている。PMOS領域AとNMOS領域Bとは、該PMOS領域AとNMOS領域Bとを電気的に分離するための絶縁膜が充填された第1のトレンチ溝105によって区画されている。第1のトレンチ溝105は、その底部の幅が上部の幅よりも大きい。これにより、PMOS領域AとNMOS領域Bとの間の耐圧の劣化を防止することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】薄膜BOX−SOI基板に形成される電界効果型トランジスタの信頼性および動作特性の劣化を防ぐことのできる技術を提供する。

【解決手段】薄膜BOX−SOI基板の主面上に所定の間隔で配置されたnウェルnwおよびpウェルpwが形成されており、pウェルpwに形成されたnMIS1nは、SOI層1iの主面上に所定の距離を隔てて積み上げられた半導体層に形成された一対のn型ソース・ドレイン領域2nと、一対のn型ソース・ドレイン領域2nに挟まれたゲート絶縁膜3、ゲート電極4、およびサイドウォール5とを有しており、nウェルnwとpウェルpwとの間に素子分離10を形成し、素子分離10の側端部が、n型ソース・ドレイン領域2nの側端部(BOX層1bの側壁部)よりもゲート電極4側に広がっている。

(もっと読む)

集積化半導体装置及びその製造方法

【課題】 SOIウェーハを使用する集積化半導体装置の結晶欠陥の低減、耐圧向上、リーク電流の低減が要求されている。

【解決手段】 SOIウェーハにトレンチ16を形成する時に、トレンチ16の底に傾斜面17を有するように半導体層13を残存させる。この傾斜面17に沿って厚いシリコン酸化膜(第2の絶縁膜)25aを形成する。この厚いシリコン酸化膜(第2の絶縁膜)25aによって埋込み絶縁層12と半導体層13との界面への酸素の侵入を防ぐ。

(もっと読む)

半導体装置

【課題】素子分離領域の端部における応力ひずみの発生及び結晶欠陥発生を抑制する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1と、半導体基板1内に形成された第1素子領域9、半導体基板1に埋め込まれて第1素子領域9を分離する第1素子分離領域4を有し、印加される電圧が第1レベルで動作を行うメモリ回路領域と、半導体基板内1に形成された第2素子領域15、半導体基板1に埋め込まれて第2素子領域15を分離する第2素子分離領域12を有し、印加される電圧が第1レベルよりも大きい第2レベルで動作を行う周辺回路領域とを備え、第1素子分離領域4の溝下方の側面と半導体基板1に垂直な平面のなす第1のテーパー角度は、第2素子分離領域12の溝下方の側面と半導体基板1に垂直な平面のなす第2のテーパー角度よりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】拡大された底部トレンチに、確実に分離膜を充填することで、トレンチ分離の縮小効果を維持しつ、高耐圧の分離膜を形成する技術を提供することを課題とする。

【解決手段】基板に形成された上部トレンチと前記上部トレンチの下に形成された底部トレンチとからなるトレンチを備え、前記底部トレンチが、前記上部トレンチより広い幅を有し、かつSOG膜又は熱酸化膜で埋め込まれ、前記上部トレンチが酸化膜で埋め込まれていることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置

【課題】SOI基板を用いたパワー半導体装置において、漏れ電流によるデバイス特性の劣化を防止した誘電体分離型の半導体装置を高い製品歩留まりで提供する。

【解決手段】本発明に係る半導体装置は、SOI基板を用い前記SOI基板中の中間絶縁膜と閉ループのトレンチとによって区画分離された誘電体分離型の半導体装置であって、前記トレンチの内壁は該トレンチを挟んで互いに接触していない側壁絶縁膜によるトレンチ側壁部と前記中間絶縁膜によるトレンチ底部とで構成されており、前記トレンチ側壁部は側壁平面部と側壁曲面部とを有し、前記側壁平面部が前記側壁曲面部を介して前記トレンチ底部と接続しており、前記側壁曲面部は前記トレンチの内部に向かって凸状の曲面であり、かつ該曲面の曲率半径が0.2μm以上10μm以下である。

(もっと読む)

半導体装置の製造方法

【課題】開口幅の異なる複数のトレンチ3を有する半導体装置の製造方法において、従来の半導体装置の製造方法より各トレンチ3で半導体基板1表面に対する側壁角度のばらつきを抑制する。

【解決手段】半導体基板1に対して、マスク2の形状に対応した開口幅の異なる複数のトレンチ3を形成するトレンチ形成工程を行う。そして、複数のトレンチ3の内壁に、ポリマー膜4より反応性イオンエッチングに対する耐性が強い保護膜5を形成する工程と、ポリマー膜4を成膜するポリマー膜成膜工程とを有するトレンチ保護膜形成工程を行う。そして、トレンチ形成工程と、トレンチ保護膜形成工程とを交互に繰り返すことによりトレンチを深くする。

(もっと読む)

1 - 20 / 77

[ Back to top ]