Fターム[5F032AB02]の内容

素子分離 (28,488) | PN接合を用いる分離 (255) | 素子領域側面のみをPN接合で分離するもの (51)

Fターム[5F032AB02]に分類される特許

1 - 20 / 51

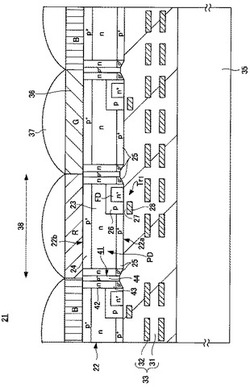

固体撮像装置及びその製造方法、電子機器

【課題】画素分離部の幅を縮小することや光電変換部の面積の拡大することを可能にする固体撮像装置を提供する。

【解決手段】第1導電型の電荷蓄積領域23を含む光電変換部及び画素トランジスタTr1から成る画素38と、画素38が複数配列された画素領域と、この画素領域内の隣接する画素38間の半導体層22に設けられたトレンチ42の内壁部に形成された、エピタキシャル成長による第1導電型の半導体層43と、この第1導電型の半導体層43の内部に形成され、隣接する画素38の電荷蓄積領域23を分離する、画素分離部41とを含んで、固体撮像装置21を構成する。

(もっと読む)

固体撮像装置および固体撮像装置の製造方法

【課題】本発明の一つの実施形態の目的は、素子分離特性を向上可能な固体撮像装置および固体撮像装置の製造方法を提供することである。

【解決手段】実施形態によれば、固体撮像装置の製造方法が提供される。固体撮像装置の製造方法は、素子分離領域形成工程と、電荷蓄積領域形成工程とを含む。素子分離領域形成工程では、第1導電型の半導体層をエピタキシャル成長させて光電変換素子間を分離する素子分離領域を形成する。電荷蓄積領域形成工程では、第2導電型の半導体層をエピタキシャル成長させて前記光電変換素子における電荷蓄積領域を形成する。

(もっと読む)

半導体装置及びその製造方法並びに抵抗器及び半導体素子

【課題】pn接合におけるリーク電流を抑制する。

【解決手段】N−型半導体層10と、シリサイド層20sがその表面に形成されたP−型半導体層20とが、絶縁体9上に形成される。半導体層10にはPMOSトランジスタを、半導体層20にはNMOSトランジスタを、それぞれ形成することができる。半導体層10,20がpn接合J50aを形成する場合、これはシリサイド層20sの端部から近く、結晶欠陥が小さい位置に存在するので、ここにおけるリーク電流は非常に小さい。半導体層10,20が形成するpn接合は、シリサイド層20sの端部から2μm以下の距離にあることが望ましい。

(もっと読む)

半導体装置及びその製造方法

【課題】閾値電圧調整用金属を含む高誘電率絶縁膜を有するゲート絶縁膜を備えたn型MISトランジスタを有する半導体装置において、ゲート幅が狭くなっても、n型MISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】n型MISトランジスタnTrは、半導体基板1における素子分離領域32に囲まれた活性領域1aと、活性領域1a上及び素子分離領域32上に形成され且つ高誘電率絶縁膜12aを有するゲート絶縁膜13aと、ゲート絶縁膜13a上に形成されたゲート電極16aとを備えている。活性領域1aにおける素子分離領域32に接する部分のうち少なくともゲート絶縁膜13aの下側に位置する部分に、n型不純物領域28が形成されている。

(もっと読む)

半導体装置の製造方法

【目的】SON構造上に素子を形成する場合や繰り返しのエピタキシャル成長で素子を形成する場合に正確な位置あわせをすることができる半導体装置の製造方法を提供すること。

【解決手段】シリコンウェハ1のダイシングライン4などの無効領域の内部にSON構造11のアライメントマーク9を形成し、このアライメントマーク9を赤色レーザ(透過型レーザ)の反射光16の変化で認識することで、図示しないSON構造23上に素子を形成する場合や繰り返しのエピタキシャル成長で素子を形成する場合に正確な位置合わせをすることができる。

(もっと読む)

固体撮像装置、及び固体撮像装置の製造方法。

【課題】 本発明は、リセットトランジスタまたは増幅トランジスタと光電変換部とを分離するための素子分離領域で発生する暗電流によるノイズを低減するとともに、画素の微細化に有利な固体撮像装置を提供することを目的とする。

【解決手段】 第1画素領域には光電変換部、FD、及び転送トランジスタが画素を単位として行列状に配される。第2画素領域には増幅トランジスタ、及びリセットトランジスタが配される。第1画素領域には第1素子分離部が配され、第2画素領域には第2素子分離部が配される。第1素子分離部において絶縁膜が半導体基板内部に突出する量が、第2素子分離部において絶縁膜が半導体基板内部に突出する量に比べて小さい。配線が配された第1主面側とは反対の第2主面側から、光電変換部に光が入射する。

(もっと読む)

半導体装置

【課題】IGBT素子領域とダイオード素子領域とを同一半導体基板に備えた逆導通型の半導体装置において、電流検知領域によるIGBT検知電流、ダイオード検知電流の検知精度を向上させる。IGBTとダイオードとの境界部分によって検知電流が不安定化することを抑制する。

【解決手段】電流検知領域を主活性領域のIGBT素子領域に隣接して配置し、IGBT素子領域のコレクタ領域を電流検知領域のコレクタ領域に接するまで伸ばす。IGBTとダイオードとの境界部分による影響を受けにくくなるため、IGBT検知電流が安定化する。同様に、電流検知領域を主活性領域のダイオード素子領域に隣接して配置し、ダイオード素子領域のカソード領域を電流検知領域のカソード領域に接するまで伸ばす。これによって、ダイオード検知電流が安定化する。

(もっと読む)

逆阻止型絶縁ゲート形バイポーラトランジスタおよびその製造方法

【課題】半導体特性または拡散炉に悪影響を及ぼすような高温、長時間の拡散をすることなく、また、トレンチ形成のような長時間プロセス加工による良品率低下が無く、高耐圧用の厚い半導体基板の表面から裏面に達する程度の深さの拡散分離層を備える逆阻止型絶縁ゲート形バイポーラトランジスタの製造方法の提供。

【解決手段】第1導電型半導体基板1の半導体デバイス領域を取り巻く位置に、該第1導電型半導体基板を貫通する第2導電型貫通領域5を、いずれか一方の主面または両主面から形成する工程と、複数枚の前記第1導電型半導体基板1を鏡面加工し、前記第2導電型貫通領域5の位置を合わせて真空中で貼り合わせる工程とを有する半導体装置の製造方法とする。

(もっと読む)

半導体装置の製造方法

【課題】高耐電圧により大電流化が可能で、オン抵抗が低く高速動作が可能で、高集積化と省エネルギーが可能で、素子間分離の容易な、電気熱変換素子駆動用の半導体装置を提供する。

【解決手段】電気熱変換素子とそれに通電するためのスイッチング素子とがp型半導体基体1に集積化されている。スイッチング素子は、半導体基体1の表面に設けられたn型ウェル領域2と、それに隣接して設けられチャネル領域を提供するp型ベース領域6と、その表面側に設けられたn型ソース領域7と、n型ウェル領域2の表面側に設けられたn型ドレイン領域8,9と、チャネル領域上にゲート絶縁膜を介して設けられたゲート電極4とを有する絶縁ゲート型電界効果トランジスタである。ベース領域6は、ドレイン領域8,9を横方向に分離するように設けられた、ウェル領域2より不純物濃度の高い半導体からなる。

(もっと読む)

半導体装置

【課題】第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供することを目的とする。

【解決手段】第1、第2素子形成領域20、30に形成された半導体素子のうち、第1素子形成領域20に形成された半導体素子を外部機器と接続し、第1素子形成領域20と第2素子形成領域30との間に、第1導電型層60と、当該第1導電型層60に挟まれる第2導電型層61とを配置し、第1、第2導電型層60、61の間に、オフ時に半導体層12の表面から埋込絶縁膜11に達し、第1、第2素子形成領域20、30との間を仕切る空乏層63、64を構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、従来の製造方法と比較し、同一ウエハまたは製品上において複数のデバイス耐圧帯と良好なオン抵抗をもったLDMOSを備えた半導体装置およびその製造方法を提供することを目的とするものである。

【解決手段】 第1電界緩和用酸化膜24と第2電界緩和用酸化膜25と素子分離用LOCOS酸化膜17の膜厚を別々に最適化することにより、同一ウエハにおいて複数のデバイス耐圧と良好なオン抵抗を実現する。

(もっと読む)

半導体装置

【課題】高電源電圧回路部に十分なラッチアップ耐性を持たせつつ、低電源電圧回路部においても高電源電圧回路部と同じトレンチ分離を使用しながら高い素子集積度を持った半導体装置を提供する。

【解決手段】トレンチ分離構造を有する半導体装置において、高電源電圧回路部には少なくとも一つのウエル領域とMOS型トランジスタが形成されて成り、ウエル領域の端部近傍のトレンチ分離領域下面にラッチアップを防止するための一対のキャリア捕獲領域を形成し配置する。

(もっと読む)

固体撮像装置およびその製造方法

【課題】本発明は、受光センサー部内のP型領域のホウ素がN型領域中へ拡散することを抑制して飽和電荷量の低下を抑えることを可能にする。

【解決手段】半導体基板11に形成されたN型領域13と、前記N型領域13上に形成された第1炭化シリコン層21と、前記炭化シリコン層21上に形成されたシリコン層22からなるP型領域14とで構成されたフォトダイオード15を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】相対的に厚いゲート絶縁膜を有するMOSトランジスタと相対的に薄いゲート絶縁膜を有するMOSトランジスタを同時に形成する半導体装置およびその製造方法の提供。

【解決手段】相対的に薄いゲート絶縁膜25を有するMOSトランジスタが形成される領域のフィールド絶縁膜端23を相対的に厚いゲート絶縁膜24で覆うことにより、フィールド絶縁膜下部に形成された反転防止拡散層31から相対的に薄いゲート絶縁膜25を有するMOSトランジスタのチャネル領域33をオフセットさせることによって、フィールド絶縁膜の膜厚ばらつきや相対的に厚い第一のゲート絶縁膜24のエッチングばらつき、および反転防止拡散層によるチャネル端の濃度変動の影響を受けず、MOSトランジスタのチャネル幅を短く設計した際に生じる狭チャネル効果の影響を抑制することが可能となり、素子特性が安定した半導体装置。

(もっと読む)

高耐圧半導体装置

【目的】裏面工程追加などの複雑な製造プロセスを一切伴わず、レベルシフタ素子である高耐圧NMOSFETの高耐圧化が安価で実現できるほか、安定した高電位配線、低いオン電圧による低電圧駆動かつ高速応答性の実現を可能とする高耐圧半導体装置および高電圧集積回路装置を提供することにある。

【構成】支持基板100上に埋め込み酸化膜200を介して半導体層101が形成され、半導体層101上に高電位側第2段トランジスタ302とそれを囲むように低電位側第1段トランジスタ301を形成し、第2段トランジスタのドレイン電極1071と第1段トランジスタ301のソース電極1072を接続する。第2段トランジスタ302のドレイン電極114はドレインパッド119と接続される。

(もっと読む)

半導体装置

【課題】IGBT素子領域とダイオード素子領域とを同一半導体基板に備えた逆導通型の半導体装置において、電流検知領域によるIGBT検知電流、ダイオード検知電流の検知精度を向上させる。IGBTとダイオードとの境界部分によって検知電流が不安定化することを抑制する。

【解決手段】電流検知領域を主活性領域のIGBT素子領域に隣接して配置し、IGBT素子領域のコレクタ領域を電流検知領域のコレクタ領域に接するまで伸ばす。IGBTとダイオードとの境界部分による影響を受けにくくなるため、IGBT検知電流が安定化する。同様に、電流検知領域を主活性領域のダイオード素子領域に隣接して配置し、ダイオード素子領域のカソード領域を電流検知領域のカソード領域に接するまで伸ばす。これによって、ダイオード検知電流が安定化する。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体基板、および半導体基板の製造方法

【課題】化合物半導体と絶縁性材料との界面に形成される界面準位が低減した半導体装置を提供する。

【解決手段】閃亜鉛鉱型の結晶構造を有する3−5族化合物半導体と、3−5族化合物半導体の(111)面、(111)面と等価な面、または、(111)面もしくは(111)面と等価な面から傾いたオフ角を有する面に接する絶縁性材料と、絶縁性材料に接し、金属伝導性材料を含むMIS型電極とを備える半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI基板に形成されたMOSトランジスタを備えた半導体装置において、ソース領域及びドレイン領域におけるPN接合領域を低減する。

【解決手段】PMOSトランジスタにおいて、LOCOS酸化膜7のバーズビーク下のシリコン層であってゲート電極17から所定範囲内に位置する第1バーズビーク下シリコン層21はチャネル領域と同じ導電型で形成されている。LOCOS酸化膜7のバーズビーク下のシリコン層であってソース領域9及びドレイン領域11と接し、かつ第1バーズビーク下シリコン層21を除く位置の第2バーズビーク下シリコン層5はソース領域9及びドレイン領域11と同じ導電型でソース領域9及びドレイン領域11よりも薄い不純物濃度で形成されている。

(もっと読む)

ワイドバンドギャップ半導体装置

【課題】JFETが形成されるセル領域とダイオード形成領域との間の絶縁耐圧を向上でき、耐圧の最適設計が行える構造のSiC半導体装置を提供する。

【解決手段】電界緩和領域R3に備えたp型領域9bとn型領域8bとにより構成されるPN分離部により、セル領域R1とダイオード形成領域R2の間の素子分離を行う。これにより、トレンチ内に酸化膜を配置して素子分離を行う場合と比べて、素子分離用の酸化膜が絶縁破壊されることが無いため、JFETが形成されるセル領域R1とダイオード形成領域R2との間の絶縁耐圧を向上できる。このため、素子分離に酸化膜を用いる場合と比べて耐圧の最適設計を行うことが可能となる。

(もっと読む)

MOSトランジスタ、固体撮像装置、電子機器、及びそれらの製造方法

【課題】チャネル領域の特性向上及び、1/fノイズの改善を図ったMOSトランジスタを提供する。また、そのMOSトランジスタを用いた固体撮像装置を提供する。

【解決手段】ゲート電極31と、ゲート電極31に対して、チャネル領域34が素子分離領域32により複数に分割されたソース・ドレイン領域33から構成されるMOSトランジスタとする。

(もっと読む)

1 - 20 / 51

[ Back to top ]