Fターム[5F032BA05]の内容

Fターム[5F032BA05]の下位に属するFターム

厚さの異なる素子領域 (101)

Fターム[5F032BA05]に分類される特許

1 - 20 / 244

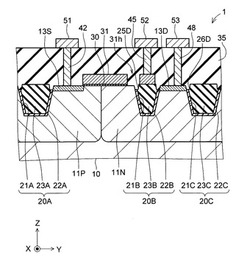

半導体装置及びその製造方法

【課題】トレンチ分離構造の上面の周縁部にディボットが形成されても、このディボットに起因するゲート絶縁膜の破壊を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、トレンチ分離構造20Bと、トレンチ分離構造20Bで区画される活性領域上に形成されたゲート絶縁膜30と、ゲート絶縁膜30の上面からトレンチ分離構造20Bの上面まで延在するゲート電極層31と、ゲート電極層31の両側に形成された第1及び第2の不純物拡散領域13D,13Sとを備える。ゲート電極層31は、ゲート絶縁膜30と第1の不純物拡散領域13Dとの間の領域に貫通孔31hを有し、貫通孔31hは、トレンチ分離構造20Bの上面の周縁部の直上に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】素子の特性が均一な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板上の一部の領域にマスク膜を形成する工程と、前記マスク膜を形成した領域及び前記マスク膜を形成していない領域の双方において、前記半導体基板の上方に、マスク部材を形成する工程と、前記マスク部材をマスクとしてエッチングを施すことにより、前記マスク膜及び前記半導体基板の上層部分をパターニングする工程と、前記パターニングされたマスク膜をマスクとしてエッチングを施すことにより、前記パターニングされた半導体基板の上層部分の一部を除去する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】FinFETの特性が均一な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板の上層部分に凹部を形成する工程と、前記凹部内に犠牲材を配置する工程と、前記半導体基板及び前記犠牲材を選択的に除去することにより、一方向に延び、周期的に配列された複数本のフィンを形成する工程と、前記フィン間の空間の下部に素子分離絶縁膜を形成する工程と、前記犠牲材を除去する工程と、前記フィンの露出面上にゲート絶縁膜を形成する工程と、前記素子分離絶縁膜上に、前記フィンを跨ぐように、前記一方向に対して交差した方向に延びるゲート電極を形成する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】アモルファスカーボン膜などの酸化によりパターン精度が劣化する材料からなるハードマスク膜上に保護膜とマスク膜の積層膜を形成し、マスク膜をダブルパターニング技術を用いてパターニングすると、保護膜も2回のエッチングに曝されて、保護膜としての機能が損なわれ、パターニングに使用する有機膜除去のアッシングの際に、ハードマスク膜が酸化されてパターン精度が劣化し、忠実なパターン転写ができなくなる。

【解決手段】マスク膜6の2回目のエッチングの際に、パターニングに用いる有機膜(反射防止膜7b、8b)をマスク膜6表面は露出するが、保護膜5表面は露出しないようにエッチングし、マスク膜6のみを選択的にパターニングすることで、その後の残存する有機膜のアッシング除去に際して、ハードマスク膜4を酸化から保護する保護膜5の機能を確保でき、パターン転写の忠実性を確保できる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜の膜厚が異なる複数のトランジスタを有する半導体装置において、オフリークの増加を抑制する。

【解決手段】半導体装置は、半導体層上に形成された第1MISトランジスタ及び第2MISトランジスタを備える。第1MISトランジスタは、活性領域101が素子分離膜102に囲まれた第1活性領域と、第1活性領域上に第1ゲート絶縁膜111を介して形成された第1ゲート電極104とを有する。第2MISトランジスタは、活性領域101が素子分離膜102に囲まれた第2活性領域と、第2活性領域上に第2ゲート絶縁膜103を介して形成された第2ゲート電極104とを有する。第2ゲート絶縁膜103は、第1ゲート絶縁膜111よりも薄い。第2MISトランジスタは、少なくとも第2ゲート電極104の下方において、第2活性領域と素子分離膜102との境界部上に、素子分離膜102の側面を覆う保護絶縁膜108を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの一部が素子分離領域上に配置された構造の半導体装置において、短絡及び接合漏れ電流の増大を抑制する。

【解決手段】半導体装置50は、半導体基板10における活性領域10aを取り囲むように形成された溝15bに素子分離絶縁膜15aが埋め込まれた素子分離領域15と、活性領域10aに形成された不純物領域26と、半導体基板10上を覆う層間絶縁膜28と、層間絶縁膜28を貫通し、活性領域10a上及び素子分離領域15上に跨って形成されたコンタクトプラグ34と、少なくともコンタクトプラグ34下方において、不純物領域26上に形成された金属シリサイド膜33とを備える。素子分離領域15は、コンタクトプラグ34の下方において、素子分離絶縁膜15と活性領域10aとの間に設けられた保護絶縁膜35を更に有する。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに絶縁分離された複数の素子を有する半導体装置の小型化と、その製造コストの低減とを実現できるようにする。

【解決手段】半導体装置は、第1の素子151、第2の素子152、第3の素子153及び第4の素子154を備えている。基板100は、基板を貫通する第1素子分離領域131により互いに分離された第1の区画101及び第2の区画102を有している。第1の区画は、第2素子分離領域132により互いに分離された第1素子領域121及び第2素子領域122を含む。第2の区画は、第3素子分離領域133により互いに分離された第3素子領域123及び第4素子領域124を含み、基板の裏面に露出した裏面拡散層を有している。第3の素子は、第3素子領域に形成され、第4の素子は、第4素子領域に形成され、第3の素子及び第4の素子は、裏面拡散層105を介在させて互いに接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】ウェル給電領域の面積を縮小して、半導体装置の微細化を行う。素子形成領域間のウェル電位のばらつきを抑制する。分離部の幅を細くする。

【解決手段】半導体装置は、半導体基板の表面に形成され、底部がウェル領域内に位置する溝状の分離部を有する。分離部は、ウェル領域と電気的に接続された導体配線と、底部に導体配線を埋め込む絶縁膜とを有する。分離部に囲まれるようにして区画されたウェル領域の一部は素子形成領域を形成し、素子形成領域には半導体素子が配置される。

(もっと読む)

半導体装置

【課題】 素子特性の劣化を抑制する。

【解決手段】 実施形態による半導体装置は、トランジスタ領域を有する半導体装置であって、トランジスタ領域は、基板上に形成された半導体領域と、半導体領域に隣接する素子分離領域と、ラテラルエピタキシャル層を備え、半導体領域上及び半導体領域と素子分離領域との間で横方向に成長するエピタキシャル層と、を具備する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】工程増を最小限とした簡便な手法で、素子形成領域における化合物半導体と同時に、しかもその結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上の素子分離領域に初期層3を選択的に形成し、初期層3上を含むSi基板1上の全面に化合物半導体の積層構造4を形成して、積層構造4は、素子分離領域では初期層3と共に素子分離構造4Bとなり、素子形成領域ではソース電極5、ドレイン電極6及びゲート電極7が形成される素子形成層4Aとなる。

(もっと読む)

半導体装置

【課題】SOI−MISFETにおいて、多結晶シリコンの残存による電気的な短絡、ゲート電極の寄生容量の増大を防止する。逆狭チャネル効果の抑制。

【解決手段】シリコン膜13を有するSOI基板上にゲート絶縁膜14、第1の多結晶シリコン膜15、ストッパー窒化膜(16)を順次堆積する。シリコン膜13、第1の多結晶シリコン膜15の側面に逆テーパー面(テーパー角θが鈍角)が形成されるようにエッチングして素子分離溝を形成する。STI埋め込み絶縁膜17を堆積し、CMPにより平坦化した後、等速性のRIEによりストッパー窒化膜(16)と絶縁膜17をエッチングして平坦な表面を得、その上に第2の多結晶シリコン膜18を堆積し(e)、積層多結晶シリコン膜をエッチングして積層ゲート電極(15、18)を形成する(f)。以下、ソース・ドレイン領域21、シリサイド膜22、層間絶縁膜23及びメタル配線24等を形成する(g)。

(もっと読む)

半導体装置及びその製造方法

【課題】電子及び正孔の移動度を向上させたSOI構造のCMOSの提供

【解決手段】Si基板1上にシリコン窒化膜2及びシリコン酸化膜3を介して貼り合わせられ、島状に絶縁分離されたGe層8(第2の半導体層)が設けられ、このGe層8に高濃度のソースドレイン領域(14、15)が形成されたPチャネルのMISFETと、Si基板1上にシリコン窒化膜2及び一部に空孔5を有するシリコン酸化膜3を介して、空孔5直上の歪みSi層7を挟み、左右にSiGe層6を有する構造からなるエピタキシャル半導体層(第1の半導体層)が島状に絶縁分離されて設けられ、歪みSi層7には概略チャネル領域が形成され、SiGe層6には概略高濃度及び低濃度のソースドレイン領域(10、11、12,13)が形成されたNチャネルのMISFETとから構成したCMOS。

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】信頼性の高いLocalSOI構造を有する基板を低コストで作製する。

【解決手段】第1の半導体からなる基板10上に、結晶成長により第2の半導体からなる層及び前記第1の半導体からなる層12を順次形成する半導体層形成工程と、前記第2の半導体からなる層をエッチングにより除去し開口領域13を形成する開口領域形成工程と、前記開口領域に、窒化物膜、炭化物膜又は酸化物膜を含む材料により形成される酸化遅延膜14を前記開口領域の入口における膜厚が所定の膜厚となるように成膜する酸化遅延膜成膜工程と、前記第1の半導体からなる基板及び前記第1の半導体からなる層の前記第1の半導体の一部を熱酸化することにより、前記開口領域に熱酸化膜15を形成する熱酸化工程とを有することを特徴とする、Local SOI半導体基板の製造方法。

(もっと読む)

素子間分離層の形成方法

【課題】半導体基板上に形成された絶縁膜の研磨工程における制御性を向上させ、優れた素子間分離性能を有する素子間分離層を形成する方法を提供する。

【解決手段】半導体基板の表面上にパッド酸化膜及び窒化膜を順次形成する工程と、パッド酸化膜及び窒化膜を貫通し、半導体基板内部に到達するトレンチを形成する工程と、トレンチを充填し且つ窒化膜を覆うように埋め込み酸化膜を形成する工程と、窒化膜上に埋め込み酸化膜が残存するように第1の研磨材を用いて埋め込み酸化膜を研磨する工程と、第1の研磨材の窒化膜に対する埋め込み酸化膜の研磨選択比よりも大なる研磨選択比を備える第2研磨材を用いて埋め込み酸化膜を研磨し、窒化膜を露出させるとともに窒化膜及び埋め込み酸化膜の露出面を平坦化する工程と、を有すること。

(もっと読む)

半導体装置およびその製造方法

【課題】少工数で製造可能で且つ高い耐圧性能を有する半導体装置を提供する。

【解決手段】素子形成領域と、素子形成領域を外部領域から絶縁分離するべく素子形成領域表面から基板表面までの深さで素子形成領域側面を包囲するよう形成された第1絶縁トレンチ領域10aとを備える半導体装置であって、素子形成領域は、埋め込みコレクタ領域と、コレクタ耐圧領域4と、ベース領域5と、表面コレクタ領域8bと、エミッタ領域8aと、ベース領域と表面コレクタ領域との間におけるキャリアの直線的な移動を遮るよう、当該領域間において素子形成領域表面から基板表面にまでの深さで形成される第2絶縁トレンチ領域10bとを備え、半導体装置を平面視した際、第2絶縁トレンチと第1絶縁トレンチ領域との間には、キャリアが第2絶縁トレンチを迂回してベース領域と表面コレクタ領域との間を移動するためのキャリア迂回領域12a,12bが形成される。

(もっと読む)

半導体装置

【課題】従来に比してオン電圧性能に優れた横型IGBT、および順方向電圧特性に優れた横型FWDを同一基板上に構成可能とする半導体装置を提供する。

【解決手段】半導体基板上において、横型IGBTと、横型FWDとが、絶縁体であるトレンチ絶縁仕切り部を挟むように横方向に隣接配置されて成る半導体装置であって、横型IGBTは、平面視した場合に、エミッタ領域と当該横型IGBTのドリフト領域との境界面の幅がコレクタ領域と当該横型IGBTのドリフト領域との境界面の幅より狭くなるよう形成されており、横型FWDは、平面視した場合に、カソード領域と当該横型FWDのドリフト領域との境界面の幅がアノード領域と当該横型FWDのドリフト領域との境界面の幅より狭くなるよう形成されていることを特徴とする、半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】工程が簡単で、よりラッチアップに強いCMOS構造を得る。

【解決手段】1×1018cm−3から1×1019cm−3の高不純物濃度の半導体基板2を用い、CMOS構造のP型ウェル4とN型ウェル5の境界に設けられた溝分離部13の先端部分がその高不純物濃度領域に達する(エピタキシャル層3を貫通して半導体基板2の領域に至る)ように深く形成することにより、従来のように溝分離部13よりも更に深い領域(溝分離部13の下側)を電子が通過することなく、従来のようにウェル領域内にN+埋め込み層やP+埋め込み層を基板深く埋め込む必要もなく、簡便な方法で、よりラッチアップに強いCMOS構造を得ることができ、コスト性能の両方に優れた半導体装置1を得ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、トランジスタを容易にOn(オン)させることが可能で、かつ良好なデータ保持特性を実現することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板12に形成され、第1の方向に延在する第1の素子分離用51、及び第1の素子分離用溝51を埋め込む第1の素子分離用絶縁膜53よりなり、複数の素子形成領域Rを有した活性領域16を区画する第1の素子分離領域14と、半導体基板12に、第1の方向と交差する第2の方向(Y方向)に延在するように形成され、第1の素子分離領域14の一部を分断する第2の素子分離用溝54、及び第2の素子分離用溝54を埋め込む第2の素子分離用絶縁膜56よりなり、複数の素子形成領域Rを区画する第2の素子分離領域17と、を有する。

(もっと読む)

半導体装置の製造方法、および電気機器

【課題】半導体装置の製造方法において、高電圧トランジスタのゲート耐圧を確保し得る程度の厚いゲート酸化膜の形成時に、この厚いゲート酸化膜が素子領域とトレンチ分離領域との境界で薄膜化するのを抑制することができ、しかも、サイズの小さい低電圧トランジスタの活性領域で、トレンチ分離溝の側壁部分での基板材料の酸化に起因した結晶欠陥が発生するのを防止する。

【解決手段】半導体基板101の表面に、半導体素子が形成されるべき素子領域を分離するようトレンチ分離領域100c、100f、100gを形成した後、該トレンチ分離領域を覆い、かつトレンチ分離領域からはみ出して該トレンチ分離領域に接する素子領域に一部重なるようシリコン窒化膜(酸化防止膜)109を形成し、該素子領域上に該酸化防止膜をマスクとして、該複数の半導体素子のうちの所定サイズの半導体素子で必要となる熱酸化膜の厚さより厚い熱酸化膜110を形成する。

(もっと読む)

1 - 20 / 244

[ Back to top ]