Fターム[5F032BA06]の内容

素子分離 (28,488) | 形状・配置 (1,422) | 素子領域の形状(断面・平面) (345) | 厚さの異なる素子領域 (101)

Fターム[5F032BA06]に分類される特許

1 - 20 / 101

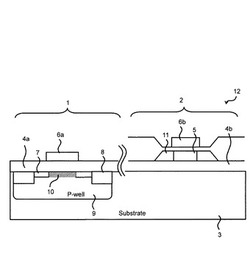

半導体装置の製造方法

【課題】閾値電圧ばらつきを改善した半導体装置の製造方法を提供する。

【解決手段】SOI基板を用いた半導体装置の製造方法において、活性層基板を酸化して埋め込み酸化膜4bを生成する工程と、支持基板3表面に、MOSトランジスタ1の閾値電圧を決定するためのチャネルドープ10を行う工程と、支持基板3と活性層基板5とを前記埋め込み酸化膜を介して貼り合せる工程と、活性層基板を部分的に除去し埋め込み酸化膜4aを露出させる工程と、埋め込み酸化膜4a上にゲート電極6aを形成する工程と、を含む半導体装置の製造方法とする。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

半導体基板およびその製造方法、その半導体基板を用いた半導体装置

【課題】実施形態は、異なる種類の半導体素子のそれぞれに適合した厚さを有する半導体層が1つの絶縁膜上に設けられた半導体基板およびその製造方法、その半導体基板を用いた半導体装置を提供する。

【解決手段】実施形態に係る半導体基板10は、第1絶縁層5と、前記第1絶縁層の上に設けられた半導体層7とを有する半導体基板であって、前記半導体層の中に選択的に設けられ、前記半導体層の表面に平行に延在し、その延在方向の長さが前記第1絶縁層よりも短い第2絶縁層13と、前記半導体層の表面から前記第1絶縁膜に至る深さに延設され、前記半導体層の前記第2絶縁層を含む部分と、前記半導体層の残りの部分と、を電気的に分離する第3絶縁層15と、を備える。

(もっと読む)

半導体装置の製造方法

【目的】SON構造上に素子を形成する場合や繰り返しのエピタキシャル成長で素子を形成する場合に正確な位置あわせをすることができる半導体装置の製造方法を提供すること。

【解決手段】シリコンウェハ1のダイシングライン4などの無効領域の内部にSON構造11のアライメントマーク9を形成し、このアライメントマーク9を赤色レーザ(透過型レーザ)の反射光16の変化で認識することで、図示しないSON構造23上に素子を形成する場合や繰り返しのエピタキシャル成長で素子を形成する場合に正確な位置合わせをすることができる。

(もっと読む)

半導体装置

【課題】トランジスタ間の分離性が良好な半導体装置を提供する。

【解決手段】半導体装置において、第1導電型の半導体基板と、前記半導体基板の上層部分を複数の能動領域に区画する素子分離絶縁膜と、前記能動領域の上部に相互に離隔して形成された第2導電型のソース層及びドレイン層と、前記半導体基板上における前記ソース層と前記ドレイン層との間のチャネル領域の直上域に設けられたゲート電極と、前記半導体基板と前記ゲート電極との間に設けられたゲート絶縁膜と、第1導電型であり、実効的な不純物濃度が前記半導体基板の実効的な不純物濃度よりも高く、前記能動領域における前記ソース層及び前記ドレイン層の直下域に形成され、前記ゲート電極の直下域には形成されていないパンチスルーストッパ層と、を設ける。

(もっと読む)

半導体装置の製造方法

【課題】同一の半導体基板上にゲート絶縁膜の膜厚の異なる半導体素子領域を容易に形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板に素子分離絶縁膜を形成することにより、第1の半導体素子領域と第2の半導体素子領域とを画定する工程と、前記第2の半導体素子領域と前記第2の半導体素子領域を囲う前記素子分離絶縁膜を覆い、前記第1の半導体素子領域と前記第1の半導体素子領域を囲う前記素子分離絶縁膜を露出させるマスクを形成する工程と、前記マスクを用いて、前記第1の半導体素子領域を囲う前記素子分離絶縁膜をエッチングする工程と、前記素子分離絶縁膜をエッチングする工程の後、前記マスクを用いて前記第1の半導体素子領域に対して異方性エッチングを行う工程と、前記マスクを除去する工程と、前記マスクを除去した後に熱酸化により第1の半導体素子領域と第2の半導体素子領域とにゲート酸化膜を形成する工程と、を有することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

半導体装置およびその作製方法

【課題】特性の良い光電変換素子を有する半導体装置を提供することを目的の一とする。または、簡単な工程で、特性の良い光センサ光電変換装置を有する半導体装置を提供することを目的の一とする。

【解決手段】光透過性を有する基板と、光透過性を有する基板上の絶縁層と、絶縁層上の、光電変換を奏する半導体領域、第1の導電型を示す半導体領域、および、第2の導電型を示す半導体領域を有する単結晶半導体層と、第1の導電型を示す半導体領域と電気的に接続された第1の電極と、第2の導電型を示す半導体領域と電気的に接続された第2の電極とを有する光電変換素子とを備える半導体装置を提供する。

(もっと読む)

ハイブリッド半導体基板の製造プロセス

【課題】ハイブリッド半導体基板及びその製造方法を提供する。

【解決手段】本発明は、(a)ベース基板3の上の絶縁層5と絶縁層の上のSeOI層7とを備えるセミコンダクタ−オン−インシュレータ(SeOI)領域13と、バルク半導体領域11とを具備するハイブリッド半導体基板1を提供するステップであって、SeOI領域とバルク半導体領域とは同じベース基板を共用するステップと、(b)SeOI領域の上にマスク層9を提供するステップと、(c)SeOI領域とバルク半導体領域を同時にドーピングすることにより、第1の不純物レベルを形成するステップであって、このドーピングは、SeOI領域の第1の不純物レベルがマスク内に含まれるように実行されるステップとを含む方法に関する。それによって、ハイブリッド半導体基板の製造プロセスに、より多くのプロセスステップが含まれることを防ぐ。

(もっと読む)

半導体およびその製造方法

【課題】SOI構造を有するCMOSトランジスタにおいて、CMOSトランジスタのチャネル領域に応力を印加する構造の製造方法の提供。

【解決手段】単結晶のシリコン基板11の表面に素子分離領域13Iにより画成されたnチャネルMOSトランジスタ10Aが形成された第1の素子領域13AとpチャネルMOSトランジスタ10Bが形成された第2の素子領域13Bとを含む単結晶シリコンの活性層13を形成し、シリコン基板と活性層との間に形成されたシリコン酸化膜を有し、シリコン酸化膜は第1の素子領域の下および第2の素子領域の下に連続して延在し、nチャネルMOSトランジスタのチャネル領域のシリコン酸化膜は最大の膜厚を有し、ゲート長方向に向かって膜厚を減少させ、pチャネルMOSトランジスタのチャネル領域のシリコン酸化膜は最小またはゼロの膜厚を有し、チャネル領域から、ゲート長方向に向かって膜厚を増大させることを特徴とする。

(もっと読む)

半導体装置

【課題】隣接するゲート電極間がショートすることを防止して、半導体装置の製造歩留まりを向上させる。

【解決手段】メモリセル領域に溝型ゲート電極構造のMOS型トランジスタ、周辺回路領域にはプレーナー型ゲート電極構造又は溝型ゲート電極構造のMOS型トランジスタが形成されるDRAMにおいて、ダミートランジスタ及び電界効果型トランジスタを第2の方向21に配列して、ダミートランジスタは第2の方向21に関して少なくとも一方の端に配置し、ダミートランジスタのゲート電極の埋設部36が電界効果トランジスタのゲート電極の埋設部36よりも第2方向21の幅が短い。

(もっと読む)

半導体装置およびその製造方法

【課題】周辺回路部のLV系トランジスタでの結晶欠陥の発生を抑制しつつ、HV系トランジスタでの反転リークなどの増加を抑制できるようにするNAND型フラッシュメモリの半導体装置と製造方法を提供する。

【解決手段】LV系トランジスタ領域103のSTI304の上面を、EB加工により、セル領域104のSTI404の上面と同時にエッチングする。こうして、HV系トランジスタ領域102のSTI204の上面の高さはそのままに、LV系トランジスタ領域103のSTI304の上面のみを、第1の電極膜12の上面の高さよりも下げる。上面の高さを下げた分だけ、LV系トランジスタ領域103のSTI304での素子分離用絶縁膜の膜厚を削減して、塗布膜の収縮応力を緩和させる。

(もっと読む)

SRAMデバイスにおけるHOTプロセスSTIおよび製造方法

【課題】H0T(ハイブリッド配向技術)プロセスおよび個々のデバイス間のSTI(シャロウトレンチアイソレーション領域)の組み合わせを使用して、同じ集積回路上のSRAMおよびロジック回路を提供する。

【解決手段】STIを備えたHOT基板上に複数のSRAM(1208)が形成され、さらに、複数のロジック回路が、複数のSOI(1202)領域上の一部のデバイスおよび複数のSOI(1202)領域上の他のデバイスと共に同じチップ上に形成される。

(もっと読む)

HOTデバイスのためのSOI/バルク境界のSTI構造

【課題】複数のHOT領域を分離する複数のSTIを備えた半導体装置において。境界領域の複数のSTIのミスアラインメントによるボイドを排除する製造方法を提供する。

【解決手段】基板400上にBOX層401を形成し、BOX層401上にSOI層402を形成し、BOX層401の一端にサイドウォール構造を形成し、BOX層401に隣接し、サイドウォール構造によってBOX層から分離してエピタキシャル層403を形成し、BOX層401とサイドウォール構造に対して非選択にエッチング液を用いた反応性イオンエッチによりSTI領域404a,404b,404cを形成した後、酸化物で充填する。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の垂直方向より水平方向により厚くシリコン酸化膜又はシリコン窒化膜が形成される異方性酸化又は異方性窒化を行う半導体装置の製造方法を提供する。

【解決手段】半導体基板1の表面に、側壁部及び底部を有する素子分離溝を形成する工程と、マイクロ波、高周波、又は電子サイクロトロンのいずれかによって発生したプラズマに含まれる酸化性イオン、又はプラズマに含まれる窒化性イオンを、半導体基板1に所定電圧を印加して素子分離溝の側壁部及び素子分離溝の底部に供給し、素子分離溝の側壁部及び素子分離溝の底部に対して異方性酸化を行う、又は異方性窒化を行う工程とを備えることを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体製造装置

【課題】シリコンエピタキシャル層と配線材料との間でショートが発生しない半導体装置の製造方法、コンタクトプラグの形成においてコンタクトホールの径の拡大を抑制する半導体装置の製造方法、これらの目的を効果的に達成できる半導体製造装置を提供する。

【解決手段】シリコン表面に形成された第1の酸化シリコン膜2と、第1の酸化シリコン膜2とは形成方法の異なる第2の酸化シリコン膜3とを有し、各々の酸化シリコン膜2,3の少なくとも一部が露出して共存するシリコン基板1を前処理する前処理工程を備えた半導体装置の製造方法であって、前記前処理工程は、第1の酸化シリコン膜2を除去して前記シリコン表面を露出させるエッチング工程を有し、前記エッチング工程は、第1の酸化シリコン膜2と第2の酸化シリコン膜3とを同じエッチングレートでエッチングすることを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】複数枚のウエハを貼り合わせる際に、電気信号接続部に発生する損傷を効果的に防止することができ、信頼性に優れ、安定した性能の得られる半導体装置を提供する。

【解決手段】素子の形成された基板1SA,1SBからなる複数枚のウエハ1WA,1WBが貼り合わされてなり、各ウエハ1WA,1WBにおける別のウエハとの貼り合わせ面30a、30bには電気信号接続部9、26が設けられ、対向する電気信号接続部9、26同士のうちの少なくとも一方が、基板1SAが露出されている貼り合わせ面30aから突出して形成された凸状接続部であり、凸状接続部の形成されている貼り合わせ面30a上における前記電気信号接続部の配置されていない領域に、基板1SAと同じ材料からなり、半導体回路と絶縁され、貼り合わされたウエハ1WA,1WB間の間隔の寸法と同じ高さで貼り合わせ面30aから突出する補強凸部52が形成されている半導体装置とする。

(もっと読む)

SOIウエハの製造方法

【課題】半導体基板上に開口部と段差を有する絶縁膜上に、エピタキシャル成長により半導体膜を形成した後研磨することにより、高精度に膜厚を制御された薄膜のSOI層を形成する際にも、SOI層中に残留結晶欠陥が少なく結晶品質の高いSOIウエハの製造方法を提供すること。

【解決手段】半導体基板1に、段差のついた第一第二絶縁膜2、3を形成し、該絶縁膜2、3の第二開口部5bにエピタキシャル層5a成長させ、該エピタキシャル層5aが前記第二開口部5aから横方向に延び、前記第二絶縁膜3を覆うように成長させた際のエピタキシャル膜厚を3μm以下に制御し、続いて、CMP研磨により前記第一絶縁膜2をストッパとして該エピタキシャル層5aを研磨し、前記第一第二絶縁膜2、3の段差の厚みとちょうど同じ厚さに制御されたSOI層を有するSOIウエハとする。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI基板において半導体層の膜厚が異なる領域にSTI型素子分離領域の形状がそれぞれ最適化され、STI型素子分離領域の位置ずれが抑制されて微細化が容易であると共に構造の異なるSTI型素子分離領域の形成が容易な半導体装置を提供する。

【解決手段】半導体層は、第1の半導体層103aからなる薄膜領域と、第1の半導体層103a上に第2の半導体層107が積層されてなる厚膜領域と、アライメントマーク領域とを備え、薄膜領域は第1のSTI型素子分離領域104aを有し、厚膜領域は第2のSTI型素子分離領域を有し、アライメントマーク領域は第2のSTI型素子分離領域の位置決めをする際に使用するアライメントマークを有することを特徴とする半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な特性で且つ信頼性の高い素子分離領域を有する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板101上に、フラッシュメモリのメモリセルにおけるゲート絶縁膜102と電極膜103を含む積層膜を形成する工程と、前記積層膜を反応性イオンエッチングによって加工し、素子分離領域を形成するためのアイソレーション溝を形成し、このアイソレーション溝内に前記半導体基板の表面を露出させる工程と、前記アイソレーション溝内に、第一の埋め込み絶縁膜として、成膜時に下地選択性を示すO3−TEOS膜107を形成する工程と、前記アイソレーション溝を第二の埋め込み絶縁膜108によって埋め込むことで、STI構造の素子分離領域を形成する工程とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】膜厚の異なるSOI層に複数種のトランジスタを形成した半導体装置において、複数種のトランジスタ間の素子分離が精度良く行える半導体装置及びその製造方法を得る。

【解決手段】SOI層3は厚膜SOI領域101及び薄膜SOI領域102を有し、厚膜SOI領域101の上層部はエピタキシャルSOI層で形成され、このエピタキシャルSOI層の膜厚分、厚膜SOI領域101のSOI膜厚t1は、薄膜SOI領域102のSOI膜厚t2より厚い。厚膜SOI領域101,薄膜SOI領域102間は完全分離酸化膜10fにより素子分離される。厚膜SOI領域101内及び薄膜SOI領域102内はそれぞれ部分分離酸化膜10pにより隣接するトランジスタ間が素子分離される。完全分離酸化膜10f及び部分分離酸化膜10pの上面は厚膜SOI領域101及び薄膜SOI領域102におけるSOI層3の上面よりも高く形成される。

(もっと読む)

1 - 20 / 101

[ Back to top ]