Fターム[5F033HH07]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853)

Fターム[5F033HH07]の下位に属するFターム

Fターム[5F033HH07]に分類される特許

2,001 - 2,020 / 2,238

半導体装置の製造方法

キャパシタ誘電体膜の原料膜としてPLZT膜(30)を形成した後、PLZT膜(30)上に上部電極膜31を形成する。上部電極膜(31)は互いに組成の異なる2層のIrOx膜から構成する。続いて、半導体基板(11)の背面の洗浄を行う。そして、上部電極膜(31)上にIr密着膜(32)を形成する。このとき基板温度を400℃以上とする。次に、ハードマスクとしてTiN膜及びTEOS膜を順次形成する。このような方法では、Ir密着膜(32)を形成するに当たって半導体基板(11)の温度を400℃以上に保持している間に、背面の洗浄後に上部電極膜(31)上に残留していた炭素がチャンバ内に放出される。このため、その後に形成されるTiN膜とIr密着膜(32)との間の密着性が高くなり、TiN膜の剥がれが生じにくくなる。  (もっと読む)

(もっと読む)

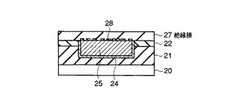

半導体装置およびその製造方法

【課題】 Cu配線を有し信頼性の高い半導体装置を提供する。

【解決手段】 半導体基板(20)と、前記半導体基板上に形成された第1の絶縁膜(21,22)と、前記第1の絶縁膜に埋め込まれたCu配線(25)と、前記Cu配線上に形成された第2の絶縁膜(27)を具備する半導体装置である。前記Cu配線と前記第2の絶縁膜との界面には、Ti、Al、W、Pd、Sn、Ni、Mg、およびZnからなる群から選択される少なくとも1種の金属またはその酸化物(28)が不連続に存在することを特徴とする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】半導体集積回路装置の高速化を図り、また、エレクトロマイグレーションやストレスマイグレーションの発生を抑え、配線寿命を長くする技術を提供する。

【解決手段】半導体基板1上に形成された酸化シリコン膜23および窒化シリコン膜22中の配線溝内を含む酸化シリコン膜23上にバリア層26aおよび銅膜26bを順次形成後、前記配線溝外部のバリア層26aおよび銅膜26bを除去することによって配線26を形成し、配線26上にタングステンを選択成長もしくは優先成長させることにより、配線26上にタングステン膜26cを形成する。

(もっと読む)

半導体装置、表示装置、及びそれらの作製方法、並びにテレビジョン装置

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な半導体装置、表示装置及びその作製技術を提供することを目的とする。また、それらの半導体装置、表示装置を構成する配線等のパターンを、所望の形状で密着性よく形成できる技術を提供することも目的とする。

【解決手段】第1の導電層と第2の導電層の間に、導電性の有孔バッファ層を形成することによって、第1の導電層と第2の導電層との密着性を高める。有孔バッファ層が有する孔に、粒子状の導電性材料を侵入させ、焼成によって固化し、第2の導電層を形成する。孔内で固化した導電層がくさびのような働きをし、この働く力によって、第2の導電層は、第1の導電層と密着性よく安定して形成される。

(もっと読む)

加熱方法及び加熱装置

【課題】 大気圧未満に減圧された環境下においても加熱対象物を効率的に加熱することができる加熱装置を提供する。

【解決手段】 気密構造を有するチャンバ8内に、加熱対象物1を収容した収容槽2と、収容槽2と熱的に結合し、外部から給電されて発熱を生じることにより、収容槽2を介して加熱対象物1を加熱する発熱構造体4と、発熱構造体4と収容槽2とに接触した状態で両者の間に介在し、両者を熱的に結合させる熱伝導媒体5とが配置される。発熱構造体4によって加熱対象物1を目標温度に加熱する過程で熱伝導媒体5が溶融する。溶融した熱伝導媒体5が、発熱構造体4と収容槽2との間の隙間を埋める。

(もっと読む)

半導体装置、半導体装置の製造方法、回路基板、及び電子機器

【課題】 貫通電極を備えて三次元実装を可能にした半導体装置について、さらなる小型化、薄型化を可能にした、半導体装置、半導体装置の製造方法、回路基板、及びこの回路基板を備えた電子機器を提供する。

【解決手段】 半導体基板10と、半導体基板10を貫通し、集積回路が形成された半導体基板の能動面10A、及びその裏面10Bから突出する貫通電極12と、を備えた半導体装置1である。半導体基板10の能動面10A側に設けられ、かつ能動面10B側に突出した貫通電極12の高さよりも厚く、貫通電極12の少なくとも一部を露出する開口を有した第1の樹脂層18を備える。第1の樹脂層18上に設けられ、かつ開口を介して貫通電極12に接続する配線層21と、配線層21に接続する外部接続端子23と、を備えている。

(もっと読む)

パッシベーション層を有する半導体素子

【課題】パッシベーション層に亀裂が生じても機能が損なわれない、または、機能が損なわれることを小さく抑える半導体素子を提供する。

【解決手段】半導体素子は、半導体基板(1)と上記半導体基板(1)の上側に配置されるとともに、側面に沿ってお互い隣接する複数の金属領域(81,82,83)と絶縁体領域(10)とを有し、上記金属領域(81,82,83)が、上記半導体本体(1)に電流を供給する役目を果たしている金属/絶縁体構造(2)とを備えている。上記金属/絶縁体構造は、半導体基板(1)の上側に配置されており、複数の金属領域(81,82,83)と側面に沿って相互に隣接する絶縁体領域(10)とを有している。さらに、半導体素子は、金属/絶縁体構造(2)上に配置されたパッシベーション層(3)を備えている。パッシベーション層(3)は、金属または金属を含む化合物からなっている。

(もっと読む)

半導体デバイスのためのARC層

半導体デバイスの製造において使用される反射防止膜(ARC)の層(201)。ARC層は底部を有し、同底部は、底部上に配置されたARC層の部分と比較して低いケイ素含有率を有する。ARC層は金属層(107)上に形成される。ARC層の比較的低いケイ素含有率は、金属層/ARC層の界面における望ましくないシリサイドの形成を抑制する。ARC層の頂部は、ARC層の中間部と比較して低いケイ素含有率を有し、頂部の比較的低いケイ素含有率は、ARC層上のフォトレジスト層の汚染を抑制し得る。ケイ素含有率は、蒸着工程中、ケイ素含有ガスの流量に対して窒素含有ガスの流量を減少、又は増大させることによって増大または減少させ得る。  (もっと読む)

(もっと読む)

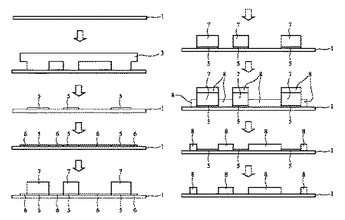

半導体装置の作製方法

【課題】好適な形状の配線を有する半導体装置を提供することを課題とする。

【解決手段】素子と接続される第1の導電層と、その上の第2の導電層とを形成し、第2の導電層上にレジストのマスクを形成し、マスクを用いたドライエッチングによって第2の導電層を加工し、マスクを残したままウエットエッチングによって第1の導電層を加工する配線の作製方法であって、ドライエッチングにおいて、第2の導電層のエッチングレートは第1の導電層のエッチングレートより大きく、ウエットエッチングにおいて、第2の導電層のエッチングレートは第1の導電層のエッチングレート以上とする。

(もっと読む)

半導体装置

【課題】実装面積が小さく性能ばらつきの少ないインダクタを有する半導体装置を提供する。

【解決手段】半導体基板10と、半導体基板10の表面11に配列して形成される少なくとも一つ以上の配線パターン13と、半導体基板10の裏面に配列して形成される少なくとも一つ以上の配線パターン14と、表面側及び裏面側の配線パターン13,14の夫々の面内に形成される、表面11から裏面12に貫通する少なくとも一つ以上の貫通電極15と、を有し、配線パターン13と配線パターン14とを貫通電極15を介して螺旋状に接続することにより形成される螺旋状インダクタ16を有する半導体装置1を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】 回路要素のキャパシタを備え、小型で冗長な配線を持たないICチップを搭載した低コストの半導体装置、およびその製造方法を提供すること。

【解決手段】 所定の厚さに裏面研削されたICチップ1のシリコン基板11の表面の電極または配線12を平行平板電極の一方の電極とし、一方の電極と対向して、シリコン基板11の裏面にパッケージ基板2の表面の電極または配線22を密接させ他方の電極とすると共に、ICチップ1とパッケージ基板2との間の電極または配線22を除く部分に接着樹脂4を適用して、パッケージ基板2上にICチップ1をフェイスアップに搭載する。これによって、シリコン基板11を誘電体層とし、一方の電極12と他方の電極22とからなるキャパシタ8を形成させる。

(もっと読む)

微細ワイヤ及びその製造方法

【課題】 1ナノメートルよりも細い微細ワイヤを提供する。

【解決手段】 第1の元素からなる第1のクラスタあるいは第2の元素からなる第2のクラスタと前記第1のクラスタとを複数連結してなる。

(もっと読む)

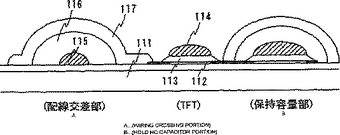

半導体装置およびその作製方法

島状の層間絶縁膜をソース線とゲート線が交差する領域に選択的に形成する。例えば、インクジェット法を用いて絶縁材料を含む液体をゲート線とソース線が交差する領域若しくは保持容量が形成される領域に滴下することにより、フォトリソグラフィー工程を削減し、TFT作製プロセス中において使用するマスク枚数を減らすことが可能となる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 チッピング防止溝やヒューズの開口部が形成されていても、再配線を形成する際に必要となるシード層を信頼性よく形成できる技術を提供する。

【解決手段】 ボンディングパッド3およびヒューズ4を形成した後、ボンディングパッド3およびヒューズ4上を含む層間絶縁膜2上に順次酸化シリコン膜5、窒化シリコン膜6、感光性ポリイミド樹脂膜7を形成する。そして、ヒューズ4上に溝9を形成するとともにボンディングパッド3上に開口部を形成する。さらに、チッピング防止溝10も形成する。続いて、溝9およびチッピング防止溝10を埋め込むように感光性ポリイミド樹脂膜11を形成する。そして、感光性ポリイミド樹脂膜11にボンディングパッド3に達する開口部を形成した後、ボンディングパッド3上を含む感光性ポリイミド樹脂膜11上にシード層13を形成する。

(もっと読む)

表面のパターン処理および制御された析出成長物を用いたビアの製造

本発明は、表面のパターン処理の方法、および制御された析出成長物を用いたビアの製造、ならびにそのような本発明による方法によって調製されたパターン化された基板に関する。本発明による方法は、上部に材料をパターン化する必要のある、少なくとも一つの表面を有する基板を提供するステップであって、前記表面は、異なる表面特性を有する少なくとも第1および第2の表面領域を有し、前記第1の領域には、さらに保護析出成長物が設置されるステップと、少なくとも前記第2の表面領域に、少なくとも一つの材料を設置するステップであって、前記設置された材料は、前記第1の表面領域には実質的に設置されないか、前記第1の表面領域に設置される場合、前記設置された材料は、前記第1の表面領域から選択的に除去されるステップと、を有する。  (もっと読む)

(もっと読む)

導電性微細パターンの製造方法

【課題】 本発明は、配線幅及び配線間隔が0. 2μm以上10μm以下の微細な配線パターンを容易に精度よく均一に且つ再現性よく得ることのできる導電性微細パターンの製造方法を提供する。

【解決手段】 熱可塑性樹脂を主体とする加熱消滅性材料と導電性金属ナノ粒子よりなる加熱消滅性組成物を、所定の微細パターンが形成されている型に塗布し、加熱消滅性組成物層を積層する工程、リバーサルインプリント法により、微細パターンに応じた加熱消滅性組成物層を基材上に転写する工程及び加熱して加熱消滅性材料を除去し、基材に導電性微細パターンを形成する工程からなることを特徴とする導電性微細パターンの製造方法。

(もっと読む)

薄膜トランジスタ、その製造方法及び薄膜トランジスタを備えた平板表示装置

【課題】薄膜トランジスタ、その製造方法及び薄膜トランジスタを備えた平板表示装置を提供する。

【解決手段】ゲート電極と、ゲート電極と絶縁されたソース及びドレイン電極と、ゲート電極と絶縁され、ソース及びドレイン電極にそれぞれ接する有機半導体層と、ソース及びドレイン電極及び有機半導体層とゲート電極とを絶縁させる絶縁層と、ゲート電極と連結された第1配線と、ソース及びドレイン電極の何れか一つと連結された第2配線と、を備え、ゲート電極、第1配線、ソース及びドレイン電極、及び、第2配線のうち、少なくとも何れか一つが、導電性ナノ粒子及び硬化性樹脂の硬化物を含む薄膜トランジスタである。また、その製造方法及び薄膜トランジスタを備えた平板表示装置である。これにより、薄膜トランジスタのうち導電性膜は、精密なパターンを有し、低コストの低温工程で製造されうる。

(もっと読む)

薄膜トランジスタ、その製造方法、これを有する表示装置、及び表示装置の製造方法

【課題】特性が向上した薄膜トランジスタの製造方法、これを有する表示装置、及び表示装置の製造方法を提供する。

【解決手段】薄膜トランジスタ100は、基板105上にゲート電極110、ゲート絶縁膜115、半導体パターン122及び半導体パターン上に相互離隔する第1及び第2導電性接合パターン127a,127b、第1バリヤーパターン131,141、ソース,ドレインパターン133,143、及び第1,第2キャッピングパターン135,145が形成されたソース,ドレイン電極130,140を含む。第1及び第2導電性接合パターン127a,127bが垂直なプロファイルを有するように形成する。

(もっと読む)

電子回路基板とその製造方法及び電子回路基板を用いた表示装置

【課題】繰り返し折り曲げても断線不良の起きない、接続信頼性が高いフレキシブル基板及びその製造方法、さらにその基板を用いた表示装置を提供する。

【解決手段】フレキシブル性を有するデバイスであって、基板に形成される金属配線12の少なくとも一部が導電性高分子により覆われている。具体的には、基板11上に金属の配線12を形成し、その配線上を覆うように導電性高分子の配線13を形成し、金属配線12と導電性高分子配線13とを多層構造にする。

(もっと読む)

半導体装置

【課題】銅ダマシン配線のエレクトロマイグレーション耐性の向上を図る。

【解決手段】本発明の例に関わる多層配線構造を有する半導体集積回路が形成される半導体装置は、銅配線14と、銅配線14の上面上に形成される絶縁層16とを備え、銅配線14は、銅配線14と絶縁層16との密着性を向上させる添加物を含み、その添加物のプロファイルは、銅配線14の上面から内部に向かうに従い、次第に濃度が減少する勾配を持ち、銅配線14の上面で最も高い濃度となる。

(もっと読む)

2,001 - 2,020 / 2,238

[ Back to top ]