Fターム[5F033HH25]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | シリサイド (1,618)

Fターム[5F033HH25]の下位に属するFターム

高融点金属のシリサイド (1,006)

Fターム[5F033HH25]に分類される特許

601 - 612 / 612

ビット線構造およびその製造方法

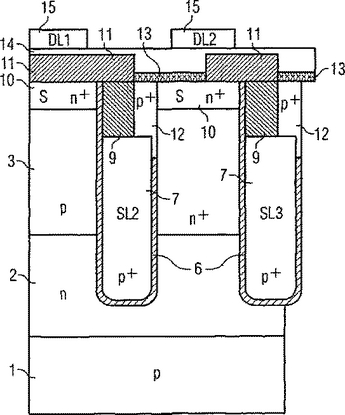

本発明は、表面ビット線(DLx)および埋め込みビット線(SLx)を備えたビット線構造に関するものである。これに関して、埋め込みビット線(SLx)は、トレンチ絶縁層(6)を備えたトレンチに形成されており、トレンチの上部に設けられた被覆接続層(12)と自動調心電極層(13)とを介して形成された接触部とともに、ドープ領域(10)に接続されている。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

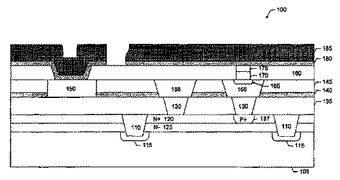

【課題】 高抵抗素子を、半導体基板内の不純物拡散層を用いて形成することにより、サリサイドプロセスにおいても、構造的に、高抵抗素子部におけるシリサイド膜の形成を防止し、工程数を増大させることなく、高抵抗素子の形成を可能とする。

【解決手段】 シリコン基板11aの上の素子領域にゲート絶縁膜12aを介してポリシリコン配線12層を形成し、このポリシリコン配線12層の上から、不純物を拡散してポリシリコン配線12層の抵抗値を調整すると共に、このポリシリコン配線12層をマスクとしてシリコン基板11a上の素子領域内において、ポリシリコン配線12層に隣接する領域に不純物を拡散させN型不純物層11cを形成してこれを高抵抗素子とし、この高抵抗素子つまりN型不純物層11cの上にSiN膜14からなる絶縁膜を配置して、この上から、サリサイドを施して、ポリシリコン配線12の上にシリサイド膜17を形成することにより得られる。

(もっと読む)

半導体装置

【課題】デュアルゲート構造を有するMIS型トランジスタにおいて、デュアルゲートにおけるシリサイド部分の断線に起因する遅延の劣化を防止して、動作不良を防止できるようにする。

【解決手段】 半導体装置は、上部がシリサイド化されたゲート電極22を有するP型MOSトランジスタ100及びN型MOSトランジスタ200を備え、ゲート電極22におけるP型MOSトランジスタ100部分は、P型不純物が導入されたポリシリコンを含み、そのN型MOSトランジスタ200部分は、N型不純物が導入されたポリシリコンを含む。P型MOSトランジスタ100及びN型MOSトランジスタ200の互いのドレインは、シリサイド化されたポリシリコンを含む共有配線23により接続されている。共有配線23の線幅は、ゲート電極22の線幅よりも大きくなるように設定されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 Bモード故障とシリサイド未形成による動作不良の双方を解消した半導体装置を提供する。

【解決手段】 素子分離領域により画成された第1および第2の素子領域を有する基板と、前記第1の素子領域に形成された第1のポリシリコンゲート電極を有する第1の電界効果トランジスタと、前記第2の素子領域に形成された第2のポリシリコンゲート電極を有する第2の電界効果トランジスタと、前記第1のポリシリコンゲート電極と前記第2のポリシリコンゲート電極とを結んで前記素子分離領域上を延在するポリシリコンパターンと、前記第1のポリシリコンゲート電極の表面および前記第2のポリシリコンゲート電極の表面、さらに前記ポリシリコンパターンの表面に形成され、前記第1のポリシリコンゲート電極から前記第2のポリシリコンゲート電極まで、前記ポリシリコンパターン上を延在するシリサイド層とよりなる半導体装置において、前記シリサイド層は前記ポリシリコンパターン上において層厚が増大した厚膜部を含み、前記厚膜部では、前記シリサイド層の表面が上方に突出する。

(もっと読む)

半導体構成のための電気的接続を形成する方法

本発明は、半導体構成に関連して電気的接続を形成する方法を含む。その上に導電線路を有し、導電線路に隣接して少なくとも2つの拡散領域を有する半導体基板が設けられる。パターン化されるエッチ・ストップが拡散領域の上に形成される。パターン化されるエッチ・ストップは、開口を貫通して延びる1対の開口を有し、開口は導電線路の軸に実質的に平行に一列に並んでいる。絶縁材料がエッチ・ストップ上に形成される。絶縁材料は、絶縁材料内にトレンチを形成し且つ開口をエッチ・ストップから拡散領域まで延ばすために、エッチングに対して露出される。トレンチの少なくとも一部分は開口の直上にあり、線路の軸に沿って延びる。導電材料が開口内とトレンチ内に形成される。  (もっと読む)

(もっと読む)

メモリセル形成のためのインサイチュ表面処理

有機メモリセルの製造中などに実施されうるものなど、導電層上にパッシブ層を形成するためのシステムおよび方法が開示され、これは、一般に、従来の無機メモリデバイスに固有の不具合を低減させる。パッシブ層は硫化銅(Cu2S)などの導電促進化合物を含み、これは、導電材料の上部から形成される。この導電材料はメモリセルにおいて下部電極として作用し、導電材料の上部が、フッ素(F)系ガスから生成されたプラズマによる処理によってパッシブ層に変換されうる。  (もっと読む)

(もっと読む)

半導体基板導電層表面の清浄化方法

残渣有機物や自然酸化物を十分に除去でき、且つ、ビアホールの側壁絶縁膜にダメージを与えることなく、k値に悪影響を与えることがない半導体基板導電層表面の清浄化方法を提供する。

半導体基板の導電層1表面上に絶縁膜2,3が形成され、絶縁膜3には

導電層1の一部を露出するビアホール4が形成された半導体装置を反応容器内に搬入し、反応容器内に水素を含むプラズマを発生させて、ビアホール4底部の導電層1上を清浄化し、アッシングにより残渣有機物6を分解除去し、導電層1表面上の銅酸化膜7をCuに還元する。

(もっと読む)

精密ポリシリコン・レジスタ・プロセス

【課題】 製造されるポリシリコン・レジスタのシート抵抗の許容誤差をより正確に制御する精密ポリシリコン・レジスタを製造するためのプロセスを提供する。

【解決手段】 プロセスは、一般に、部分的に形成されたポリシリコン・レジスタを有するウェハに対して、エミッタ/FET活性化高速熱アニール(RTA)を行うステップと、それに続いて、保護誘電体層をポリシリコン上に堆積させるステップと、ドーパントを該保護誘電体層を通して該ポリシリコンに注入して、ポリシリコン・レジスタの抵抗を定めるステップと、シリサイドを形成するステップとを含む。

(もっと読む)

基板上に多機能誘電体層を形成する方法

本発明は、多機能誘電体層を基板上、特に基板上に露出している金属配線系上に形成する方法に関する。本発明の目的は、銅による配線を形成するための多機能パッシベーション層を容易に形成する方法を提供するとともに、エレクトロマイグレーション、ストレスマイグレーション、および接着性を向上させる方法を提供することにある。本発明によれば、更なる金属層(5)を、露出した金属配線(3)の表面上に堆積することによって、本発明の目的は達せられる。この金属層は少なくともその一部が非導電性の金属酸化物に変換され、誘電体層となっている。  (もっと読む)

(もっと読む)

薄膜トランジスタ表示板、これを含む平板ディスプレイ表示装置及びその製造方法

本発明は、薄膜トランジスタ表示板とこれを含む液晶表示装置及びその製造方法に関し、薄膜トランジスタ表示板は液晶表示装置や有機EL(electro luminescence)表示装置などで、各画素を独立的に駆動するための回路基板において、画素電極またはゲート線及びデータ線の拡張部を外部回路と接続させるコンタクト補助部材を、IZO及びITOの2重層で形成することに対する発明であって、IZOで形成された下部層とITOで形成された上部層を有するように形成する。前記のように画素電極またはコンタクト補助部材を二重層で形成することによって、エッチング過程で下部配線が損傷されることを防止し、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を良好に確保することができる。また、コンタクト補助部材のみをIZOとITO二重層で形成することによって、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を確保することができ、ITOの使用を減らすことによって製造単価を下げることができる。  (もっと読む)

(もっと読む)

ビア開口部中に形成されるポリマーメモリデバイス

本発明は、ビア内にポリマーメモリデバイスを製造する方法に関する。この方法は、少なくとも1つの金属を含む層をその上に備える半導体基板を提供するステップと、この金属を含む層中に少なくとも1つの銅コンタクトを形成するステップと、銅コンタクト上に少なくとも1つの絶縁層を形成するステップと、絶縁層に少なくとも1つのビアを形成し、銅コンタクトの少なくとも一部を露出するステップと、ビアの下側部分にポリマー材料を形成するステップと、ビアの上側部分にトップ電極材料層を形成するステップとを含む。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗且つ高バリア性を有するバリアメタルを提供する。

【解決手段】バリアメタル201 が、配線溝16の底面及び側壁の表面に沿って形成された膜厚16nmのTaN0.87膜31と、TaN0.87膜上に形成され、配線溝16に埋め込み形成されたCuダマシン配線17に接する膜厚4nmのTaN1.19膜32とから構成されている。

(もっと読む)

601 - 612 / 612

[ Back to top ]