Fターム[5F033HH26]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | シリサイド (1,618) | 高融点金属のシリサイド (1,006)

Fターム[5F033HH26]の下位に属するFターム

Fターム[5F033HH26]に分類される特許

1 - 20 / 78

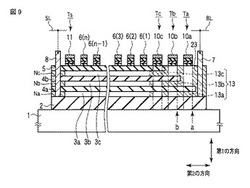

半導体装置及びその製造方法

【課題】微細配線を簡易に低抵抗化する。

【解決手段】実施形態に係わる半導体装置は、第1の方向に積み重ねられる第1乃至第3の半導体層3a,3b,3cを有し、第2の方向に延びるフィン型積層構造を有する。第1のレイヤーセレクトトランジスタTaは、第1のゲート電極10aを有し、第1の半導体層3aでノーマリオン状態である。第2のレイヤーセレクトトランジスタTbは、第2のゲート電極10bを有し、第2の半導体層3bでノーマリオン状態である。第3のレイヤーセレクトトランジスタTcは、第3のゲート電極10cを有し、第3の半導体層3cでノーマリオン状態である。第1の半導体層3aのうちの第1のゲート電極10aにより覆われた領域、第2の半導体層3bのうちの第2のゲート電極10bにより覆われた領域及び第3の半導体層3cのうちの第3のゲート電極10cにより覆われた領域は、それぞれ金属シリサイド化される。

(もっと読む)

半導体装置

【課題】半導体装置において、高電圧の配線層とその下方を横切るように配置された抵抗層との間の絶縁膜の耐圧を確保し、この配線層と抵抗層との間で破壊が起きるのを抑制することを目的とする。

【解決手段】第1半導体領域10に接続され第2半導体領域11上を通過するように第3配線層22が配置されている。第3配線層22と第2半導体領域11との間に配置される絶縁膜14内には、一端が第3配線層22に接続されると共に、他端が第1半導体領域11よりも電位の低い制御端子12に接続され、且つ第3配線層22とSOI層2との間において第3配線層22を少なくとも1回以上横切る構成で抵抗層25が配置されている。この抵抗層25は、第3配線層22を横切る部位の上面が他の部位よりも下方位置となるように段差状に形成されている。

(もっと読む)

半導体素子の製造方法

【課題】本発明は、Si基板の表面にシリサイド層を形成しつつ、Si基板の裏面における低融点金属とSi基板のSiとの相互拡散を防止できる半導体素子の製造方法を提供することを目的とする。

【解決手段】本願の発明に係る半導体素子の製造方法は、Si基板の裏面に低融点金属を形成する工程と、該Si基板の表面に高融点金属層を形成する工程と、該高融点金属層の上にレーザ吸収層を形成する工程と、該レーザ吸収層にレーザ光を照射し、該低融点金属と該Si基板のSiとの相互拡散を防ぐように該低融点金属の温度を低く保ちつつ、該レーザ吸収層と該高融点金属層の界面、及び該高融点金属層と該Si基板の界面にシリサイド層を形成する工程と、該レーザ吸収層をエッチングする工程と、を備えたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】シェアードコンタクトの接触不良を防止して、半導体装置の製造歩留まりを向上させることのできる技術を提供する。

【解決手段】高密度版回路における電界効果トランジスタTr3のゲート電極G3と電界効果トランジスタTr4のゲート電極G4とのピッチは、高速版回路における電界効果トランジスタTr1のゲート電極G1と電界効果トランジスタTr2のゲート電極G2のピッチよりも小さいが、シェアードコンタクトホールSCが達する部分のゲート電極G3に切欠を設けることにより、シェアードコンタクトホールSCと不純物領域S/Dとの接触面積を広くする。

(もっと読む)

半導体装置の製造方法

【課題】制御性よく空洞部を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】ダミーゲート電極22上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極22の側壁下部にオフセットスペーサ24を形成する。そして、サイドウォール15の形成後、ダミーゲート電極22とオフセットスペーサ24とを除去し、高誘電率材料からなるゲート絶縁膜13とメタルゲート電極14とを異方性の高い堆積方法を用いて形成する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのチャネル部に印加される応力を増加させて、電流増加効果を高めることを可能とする。

【解決手段】半導体基板上にダミーゲートを形成した後、該ダミーゲートの側壁に側壁絶縁膜を形成し、該ダミーゲートの両側の前記半導体基板にソース・ドレイン領域を形成する工程と、前記ダミーゲートおよび前記ソース・ドレイン領域の上に応力印加膜を形成する工程と、前記ダミーゲートの上の領域に形成された前記応力印加膜と前記ダミーゲートを除去して溝を形成する工程と、前記溝内の前記半導体基板上にゲート絶縁膜を介してゲート電極を形成する工程と、を備えた半導体装置の製造方法。

(もっと読む)

半導体デバイス用基板洗浄液及び洗浄方法

【課題】基板表面を腐食することなく微粒子付着による汚染、有機物汚染及び金属汚染を同時に除去することができ、しかも水リンス性も良好で、短時間で基板表面を高清浄化することができる半導体デバイス用基板洗浄液を提供する。

【解決手段】

半導体デバイス製造における化学的機械的研磨工程の後に行われる、半導体デバイス用基板の洗浄工程に用いられる洗浄液であって、以下の成分(A)〜(D)を含有してなる半導体デバイス用基板洗浄液。

(A)有機酸

(B)スルホン酸型アニオン性界面活性剤

(C)ポリビニルピロリドン及びポリエチレンオキシド−ポリプロピレンオキシドブロック共重合体から選ばれる少なくとも1種の高分子凝集剤

(D)水

(もっと読む)

ドライエッチング剤

【課題】経済性を備え、地球環境に対する影響が小さく、かつ必要とされる性能を有するドライエッチング剤を提供する。

【解決手段】(A)3,3,3−トリフルオロプロピンと、(B)O2、O3、CO、CO2、COCl2、及びCOF2からなる群より選ばれる少なくとも1種のガスを含むドライエッチング剤を用いることにより、酸化物、窒化物、炭化物、フッ化物、オキシフッ化物、シリサイド及びこれらの合金等を好適にエッチングできる。ドライエッチング剤は、大気中での分解性があり、地球温暖化への寄与もCF4やCF3H等のPFC類やHFC類より格段に低く、環境への負荷が低い。さらに、第二のガスとして、含酸素ガス、含ハロゲンガス、あるいは第三のガスとして不活性ガスと混合することで、飛躍的にプロセスウインドウを広げることができ、特殊な基板の励起操作等なしに高アスペクト比が要求される加工にも対応できる。

(もっと読む)

半導体装置およびその製造方法

【課題】配線構造に接続される低抵抗の貫通プラグ、または貫通プラグ及びコンタクトプラグを有する半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板1と、半導体基板1の表面近傍に埋め込まれた素子分離絶縁膜2と、素子分離絶縁膜2を貫通するように半導体基板1の裏面から表面まで貫通し、半導体基板1中で素子分離絶縁膜2に囲まれた領域を有する上段部101aと上段部101aよりも径が大きい下段部101bとを含む多段構造を有する貫通プラグ101と、貫通プラグ101の半導体基板1の表面側の端部に接続され、半導体基板1の表面側の上方に形成された電極パッド104と貫通プラグ101を接続するコンタクトプラグ103と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法に関し、シリサイドを構成する金属のサイドウォールの直下への潜り込みの影響を低減する。

【解決手段】 シリコン基板上にゲート電極を形成する工程と、ゲート電極の側壁に、第1絶縁膜による第1サイドウォールと、第1サイドウォール上にあって、第1絶縁膜とはエッチング特性の異なる第2絶縁膜による第2サイドウォールを形成する工程と、シリコン基板および第2サイドウォールを含む表面に金属をスパッタリングにより堆積させ、金属の一部をシリコン基板に侵入させる工程と、シリコン基板上に堆積した金属を除去する工程と、金属の除去工程の後に熱処理を行って、スパッタリングによってシリコン基板に侵入した金属とシリコン基板中のシリコン原子とを反応させてシリサイド層を形成する工程とを備える。

(もっと読む)

固体撮像装置及びその製造方法

【課題】画素における光のクロストーク等の光学特性を改善することにより、画素の微細化を実現することができる固体撮像装置を提供することである。

【解決手段】半導体基板に配され、光を電荷に変換する複数の光電変換素子(11)と、半導体基板に配され、光電変換素子により変換された電荷を電圧に変換する第1の半導体領域(13)と、第1の半導体領域に接続されたゲート電極を有し、第1の半導体領域により変換された電圧を増幅する増幅MOSトランジスタと、半導体基板を覆う絶縁膜(23)と、絶縁膜上に配される金属配線層(42)と、第1の半導体領域及び増幅MOSトランジスタのゲート電極とを金属配線層を介さず接続する第1の導電体(21)と、半導体基板に配され、第1の半導体領域とは異なる第2の半導体領域(18)と、第2の半導体領域と金属配線層の少なくとも一部とを接続する第2の導電体とを有する固体撮像装置が提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域に印加される応力分布のピークとソース領域近傍に発生する電位分布のピークの位置を最適化することで、キャリア速度を向上させて飽和電流特性を向上させることを可能にする。

【解決手段】半導体基板11に形成されたチャネル領域12と、前記チャネル領域12の一方側に形成されたソース領域19と、前記チャネル領域12の他方側に形成されたドレイン領域20と、前記チャネル領域12上にゲート絶縁膜13を介して形成されたゲート電極14と、前記チャネル領域12に応力を印加する第1、第2応力導入層21、23を有し、前記チャネル領域12と前記ソース領域19とのpn接合境界と、前記チャネル領域12と前記ドレイン領域20とのpn接合境界の間に、前記ソース領域19側の応力分布のピークと前記ドレイン領域20側の応力分布のピークが位置する。

(もっと読む)

半導体装置およびその製造方法

【課題】低電圧動作のトランジスタ群と高耐圧(高電圧動作)のトランジスタ群とを同一半導体基板に形成して、高耐圧のトランジスタ群のゲート電極の低抵抗化を可能にする。

【解決手段】半導体基板11に、第1トランジスタ群と、第1トランジスタ群の動作電圧よりも低い動作電圧の第2トランジスタ群とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介して形成された第1ゲート電極15と、この第1ゲート電極15上に形成されたシリサイド層40とを有し、第2トランジスタ群は、半導体基板11上の絶縁膜(ライナー膜36、第1層間絶縁膜38)に形成したゲート形成溝42に第2ゲート絶縁膜43を介して形成された第2ゲート電極47、48を有し、第1トランジスタ群の第1ゲート電極15上のシリサイド層40を被覆する保護膜41が形成されていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1に形成したnチャネル型MISFETQnのソース・ドレイン用のn+型半導体領域7bおよびゲート電極GE1上と、pチャネル型MISFETQpのソース・ドレイン用のp+型半導体領域8bおよびゲート電極GE2上とに、ニッケル白金シリサイドからなる金属シリサイド層13bをサリサイドプロセスで形成する。その後、半導体基板1全面上に引張応力膜TSL1を形成してから、pチャネル型MISFETQp上の引張応力膜TSL1をドライエッチングで除去し、半導体基板1全面上に圧縮応力膜CSL1を形成してからnチャネル型MISFETQn上の圧縮応力膜CSL1をドライエッチングで除去する。金属シリサイド層13bにおけるPt濃度は、表面が最も高く、表面から深い位置になるほど低くなっている。

(もっと読む)

半導体装置の製造方法

【目的】従来よりも比抵抗の低いW膜のプラグ或いは配線が得られる半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、前記絶縁膜に開口部を形成する工程(S106)と、前記開口部の少なくとも底面に、ルテニウム(Ru)膜を形成する工程(S112)と、前記Ru膜が形成された前記開口部内に、水素(H2)還元による化学気相成長(CVD)法によりタングステン(W)膜を埋め込む工程(S114)と、を備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通孔(接続孔)内に形成された絶縁膜上に設けられる配線層と半導体基板との間の電気的絶縁性の不良の発生が低減された半導体装置の製造方法を提供する。

【解決手段】半導体基板11の一方の面上に第1の絶縁層12を介して位置する第1の配線層13と、半導体基板の他方の面から第1の配線層に至る接続孔19を形成する。接続孔の側面から他方の面に亘って半導体基板上に位置し、接続孔内で第1の配線層に接する第2の絶縁層14を形成する。接続孔の側面上から他方の面上に亘って第2の絶縁層上に位置し、接続孔内で第1の配線層に接する第2の配線層16を形成する。この形成において、第2の絶縁層を、膜質の異なる2種の絶縁膜14a、14b又はそれ以上の絶縁膜の積層体から構成する。

(もっと読む)

半導体装置

【課題】トランジスタの集積化を妨げることなく、トランジスタの駆動力を向上させる半導体装置を提供する。

【解決手段】所定の結晶からなる半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、ゲート幅方向に凸部を有して前記半導体基板内に形成され、前記所定の結晶とは異なる格子定数を有するエピタキシャル結晶が埋め込まれたソース・ドレイン領域と、を具備するトランジスタと、前記凸部以外の前記ソース・ドレイン領域に接続されたコンタクトプラグと、を備えた半導体装置を提供する。

(もっと読む)

半導体基板の製造方法および半導体装置の製造方法

【課題】性能劣化を招く金属元素の半導体基板への侵入及び拡散を防ぐことのできる半導体基板の製造方法および半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体基板の製造方法は、半導体基板1の両面および側面に窒化膜2を形成する工程と、前記窒化膜2上の全面に、シリコンを含む酸化膜3および所定の金属を含む前駆体膜4Aを積層する工程と、前記酸化膜3と前記前駆体膜4Aとを反応させることにより、前記シリコンおよび前記所定の金属を含む自己形成バリア膜4を自己整合的に形成する工程と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】金属ゲートを形成した後に形成される絶縁膜中の水素の影響を抑制して、しきい値電圧Vthを所望の値(例えば0.3V)以下にすることを可能にする。

【解決手段】半導体基板11上に第1絶縁膜41が形成され、第1絶縁膜41に溝部42が形成され、溝部42の第1絶縁膜41側の半導体基板11上にサイドウォールスペーサ31が形成され、溝部42内にゲート絶縁膜21を介してゲート電極22が形成され、ゲート電極22の両側の半導体基板11にエクステンション領域23,24を介してソース・ドレイン領域25,26が形成され、第1絶縁膜41上にゲート電極22上を被覆する第2絶縁膜43を有し、サイドウォールスペーサ31は水素の通過を阻止する絶縁膜からなり、ゲート電極22上に水素の通過を阻止する水素バリア膜33が形成され、水素バリア膜33はゲート電極22上の周囲でサイドウォールスペーサ31と接続されている。

(もっと読む)

半導体装置

【課題】 容量低減とビア加工マージンの確保を効率的に達成する。

【解決手段】 複数の配線層を有する半導体装置であって、所定領域を有する第1配線層26と、第1配線層の上層に位置する第2配線層47と、第1配線層と第2配線層との間に設けられる層間絶縁膜36と、層間絶縁膜と第1配線層の配線との間に設けられるバリア絶縁膜(29,31)とを有し、所定領域における配線上部のバリア絶縁膜の厚さは、所定領域以外の領域における配線上部のバリア絶縁膜の厚さよりも厚く、所定領域においては隣接する配線間にエアギャップ35が形成され、所定領域以外においては隣接する配線間にエアギャップが形成されない。

(もっと読む)

1 - 20 / 78

[ Back to top ]