Fターム[5F033JJ03]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 半導体(基板を除く) (666)

Fターム[5F033JJ03]の下位に属するFターム

Fターム[5F033JJ03]に分類される特許

41 - 58 / 58

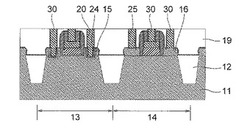

半導体装置及びその製造方法

【課題】マスク数を増やすことなく、PMOSトランジスタのソース/ドレイン拡散層内にSiGe層を形成することで、PMOSトランジスタのオン電流を向上する。

【解決手段】選択成長層15が表面に形成されたPMOSトランジスタのシリコン基板11内のソース/ドレイン拡散層上に、PMOS用コンタクトホール20を形成する。この際に、コンタクトホール20がシリコン基板11のソース/ドレイン拡散層内に届くようにエッチングする。コンタクトホール20内の拡散層上及び選択成長層15の側面にGeを選択成長し、熱処理よりSiGe層24とする。NMOSトランジスタのコンタクトホール25を選択成長層16に達するように形成する。コンタクトホール20、25内のSiGe層24及び選択成長層16上にコンタクトプラグ30を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 従来の半導体装置に形成されたアライメントマークは、該アライメントマークが形成された上層金属配線膜の直下層に配置される層間膜のコンタクトホールの段差形状が転写されていたが、該コンタクトホールの段差形状がなだらかであったため、アライメントマークの窪み深さが浅く、認識精度が低下する傾向にあった。

【解決手段】 複数層の機能膜を備え、前記複数層の機能膜のうち上層機能膜にアライメントマーク10が形成される半導体装置1であって、前記上層機能膜である上層金属配線膜8の一層下に、層間膜7を介して形成される下層機能膜である下層金属配線膜3における、前記アライメントマーク10形成箇所に相当する箇所に、所定幅の抜きパターンとなる段差部11が形成される。

(もっと読む)

半導体装置及び当該半導体装置を具備するIDラベル、IDタグ、IDカード

【課題】RFIDを有する半導体装置において、駆動電源のための電池の経時的劣化に伴う電池の残存容量の確認や電池の交換作業をすることなく、個体情報を送受信することができ、且つ駆動するための電源を外部からの電磁波の電力が十分でない場合であっても良好な個体情報の送受信状態を維持するRFIDを有する半導体装置を提供することを課題とする。

【解決手段】信号処理回路と、信号処理回路に接続された第1のアンテナ回路及び第2のアンテナ回路と、信号処理回路に接続されたバッテリーとを設け、第1のアンテナ回路は、信号処理回路に記憶されたデータを送信するための信号を送受信するものであり、第2のアンテナ回路は、バッテリーに充電するための信号を受信するものであり、第1のアンテナ回路が受信する信号と第2のアンテナ回路が受信する信号の波長が異なる構成とする。

(もっと読む)

半導体装置の製造方法

【課題】特性にばらつきが生じることを抑制して歩留まりを向上させることができる半導体装置の製造方法を提供する。

【解決手段】半導体基板10上に膜40を形成するステップと、膜40上に、所定のパターンを有するマスクを形成するステップと、マスクを用いて、膜40又は半導体基板10にエッチングを行うステップと、第1級乃至第4級アミンのうちの少なくとも1つと、フッ素とを含む薬液によって処理を行うステップとを備える。

(もっと読む)

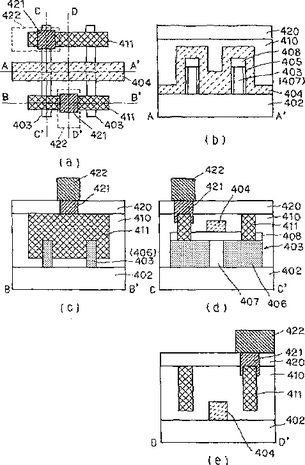

微小電気機械式装置の作製方法

【課題】微小構造を有するマイクロマシンの量産に際して、微小構造体と微小構造体を制御する半導体素子を同一基板上に形成し、コストを低減する方法を提供する。

【解決手段】マイクロマシンの作製に際して、膜のパターン形成を行うためのマスク材料を用いて犠牲層を形成し、半導体素子を形成する領域におけるマスクの除去と、微小構造体を形成する領域における犠牲層とマスクの除去を同一の工程にて行う。具体的には絶縁性基板上に選択的に犠牲層103を形成し、犠牲層を覆って半導体層104を形成し、半導体層上にマスク105を形成し、マスクを用いて半導体層をエッチングし、マスク及び犠牲層の除去を同時に行う微小電気機械式装置の作製方法を提供する。

(もっと読む)

半導体装置

【課題】銅配線を覆って設けられるバリアメタル膜のバリア性能が向上されており、低比誘電率層間絶縁膜から放出されるガスによりバリアメタル膜が酸化されても、銅配線の信頼性や性能、および品質等が低下するおそれの殆ど無い半導体装置を提供する。

【解決手段】比誘電率が3以下である絶縁膜3が基板1上に少なくとも1層設けられている。少なくとも一部がこの絶縁膜3内に形成されている凹部10の内面を覆って第1のバリアメタル膜6が設けられている。この第1のバリアメタル膜6の表面を覆って凹部10内に第2のバリアメタル膜7が設けられている。この第2のバリアメタル膜7の表面を覆って凹部10内に第3のバリアメタル膜8が設けられている。この第3のバリアメタル膜8の表面を覆って凹部10内にCu膜11が埋め込まれて設けられている。

(もっと読む)

薄膜トランジスタ及び半導体デバイスの作製方法

【課題】液滴吐出法などのマスクレスプロセスを用いて円形薄膜トランジスタを作製することにより、工程の簡略化、作製時間の短縮、及び作製費用の低減を図ると共に、従来よりもその形状が制御された円形薄膜トランジスタの作製方法を提供することを目的とする。

【解決手段】液滴吐出法等のマスクレスプロセスを用いて、基板上に同心円状の薄膜を積層し、円形の電極を有する円形薄膜トランジスタを形成する。また、液滴吐出法等のマスクレスプロセスを用いて、基板上に同心円状の薄膜を積層し、円形の半導体層を有する円形薄膜トランジスタを形成してもよい。

(もっと読む)

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上部から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在するゲート絶縁膜と、前記半導体凸部に設けられたソース/ドレイン領域とを有するMIS型電界効果トランジスタ、このトランジスタを含む基体上に設けられた層間絶縁膜、及びこの層間絶縁膜に形成された埋め込み導体配線を有し、この埋め込み導体配線は、前記半導体凸部のソース/ドレイン領域と、前記層間絶縁膜下の他の導電部とに接続されていることを特徴とする半導体装置。  (もっと読む)

(もっと読む)

半導体ダイオードを含む低温で製作された高密度不揮発性メモリアレイ

高密度のモノリシックな三次元メモリアレイにおける使用に適したメモリセルを説明する。メモリセルの好ましい実施形態において、比較的低い温度で結晶化させることができるゲルマニウムまたはゲルマニウム合金で形成された半導体接合ダイオードが、導体間に配置されて形成される。低温度材料の使用により、導体を銅またはアルミニウムで形成することが可能になり、銅およびアルミニウムは両方とも、非常に小さいフィーチャサイズで十分な電流を提供する、非常に密なスタックアレイを見越した、低抵抗率材料である。  (もっと読む)

(もっと読む)

固相エピタキシー方式を用いた半導体素子のコンタクト形成方法

【課題】SPE方式及び後続熱処理を用いてコンタクト物質をエピタキシャルシリコンとして形成する場合に発生する後続CMP工程でのディッシング現象を最小化させること。

【解決手段】 接合層が形成された半導体基板の上部に層間絶縁膜を形成するステップと、前記層間絶縁膜をエッチングして前記接合層を露出させるコンタクトホールを形成するステップと、前記コンタクトホールの底面の自然酸化膜を除去するための表面洗浄ステップと、固相エピタキシー方式を用いて前記コンタクトホールを埋めるコンタクト層を形成するが、前記接合層とのコンタクト領域ではエピタキシャル層に成長させ、前記コンタクトホールの残りの領域及び前記層間絶縁膜の表面では非晶質層に成長させるステップと、前記コンタクト層の非晶質層を選択的に平坦化させ、セルランディングプラグコンタクトを形成するステップとを含む。

(もっと読む)

導電性フィーチャへの接点を作る際の誘電体オーバーエッチングを低減するための方法

本発明の第1の好ましい実施形態において、導電性フィーチャが第1の誘電体エッチング停止層上に形成され、第2の誘電材料が導電性フィーチャ上およびその間に堆積される。第1の誘電体と第2の誘電体との間で選択的な導電性フィーチャへのバイアエッチングは、誘電体エッチング停止層上で停止し、オーバーエッチングを制限する。第2の実施形態において、複数の導電性フィーチャが減法的なパターン形成およびエッチングプロセスで形成され、誘電性充填材で満たされ、次に形成された表面が導電性フィーチャおよび誘電性充填材を同時露出する。誘電体エッチング停止層が表面に堆積させられ、次に第3の誘電体が誘電体エッチング停止層を覆う。第3の誘電体を貫通して接点がエッチングされると、この選択的エッチングは、誘電体エッチング停止層上で停止する。第2のエッチングが導電性フィーチャへの接点を作る。  (もっと読む)

(もっと読む)

平坦な表面における誘電体エッチング停止を用いて誘電体オーバーエッチングを低減するための方法

実質的に平坦な表面が、導電性フィーチャまたは半導体フィーチャと誘電体エッチング停止材料とを同時露出させる。誘電体エッチング停止材料とは異なる第2の誘電材料を、実質的に平坦な表面上に堆積する。選択的なエッチングによって、第2の誘電材料に孔または溝をエッチングして、エッチングが導電性フィーチャまたは半導体フィーチャおよび誘電体エッチング停止材料上で停止するようにする。好ましい実施形態において、実質的に平坦な表面は、導電性フィーチャまたは半導体フィーチャの間のギャップに酸化物のような第1の誘電体を満たし、酸化物を窪ませ、窒化物のような第2の誘電体を満たし、その後、窒化物と導電性フィーチャまたは半導体フィーチャとを同時露出させるように平坦化することにより形成される。  (もっと読む)

(もっと読む)

電子デバイス用基板、電子デバイス用基板の製造方法、表示装置および電子機器

【課題】本発明の目的は、例えば、表示装置において、表示ムラを低減することのできる電子デバイス用基板、かかる電子デバイス用基板の製造方法、かかる電子デバイス用基板を備える表示装置および信頼性の高い電子機器を提供すること。

【解決手段】

本発明の電子デバイス用基板は、基板と、この基板上に設けられたスイッチング素子と、このスイッチング素子を覆い、前記スイッチング素子の端子(接続部354)に到達するコンタクトホール361が設けられた層間絶縁膜360と、層間絶縁膜360上に設けられた画素電極223と、画素電極223に連続して、コンタクトホール361の内面および接続部354の表面に、気相プロセスにより形成された導電膜371と、コンタクトホール361の導電膜371内側の空間362を埋めるように充填された充填材料372とで構成される電気接続部370とを有するものである。

(もっと読む)

細線状MOSFETを含む半導体装置

【課題】 簡単な構成を採ることで、細線状素子領域に於けるソース領域及びドレイン領域からチャネル領域に向かって機械的な応力を効率良く印加し、キャリヤ移動度を向上させようとする。

【解決手段】 細線状チャネル領域4を挟んで細線状ソース領域8及び細線状ドレイン領域9が配設された細線状素子領域と、細線状ソース領域8及び細線状ドレイン領域9それぞれの少なくとも側面を覆う圧縮或いは引張の応力を発生する応力発生膜11或いは12とを備える。

(もっと読む)

半導体装置

【課題】銅ダマシン配線のエレクトロマイグレーション耐性の向上を図る。

【解決手段】本発明の例に関わる多層配線構造を有する半導体集積回路が形成される半導体装置は、銅配線14と、銅配線14の上面上に形成される絶縁層16とを備え、銅配線14は、銅配線14と絶縁層16との密着性を向上させる添加物を含み、その添加物のプロファイルは、銅配線14の上面から内部に向かうに従い、次第に濃度が減少する勾配を持ち、銅配線14の上面で最も高い濃度となる。

(もっと読む)

冷却効果を持つ電子素子および配線構造、並びに温度差を電圧に変換する機能を持つ電子素子

【課題】 電子素子のCPP配線部分での、抵抗発熱による局所的な温度上昇を回避あるいは抑制する。

【解決手段】 CPP構造は、多層構造を持つ電子素子、配線回路において、上層から下層(あるいはその反対方向)に電流を流すために、層に対して垂直な方向に加工された「柱状の導電性部分とその周辺を囲う絶縁体部分からなる構造」を指す。このCPP構造は、異種材料の上部電極と下部電極のそれぞれから、柱状部を一体に延長して、接合することにより構成される。このCPP構造部分は、適切に選択された異種材料(金属、半導体とその合金など、導電性物質一般を指す)からなる界面(界面群)を持っている。これによって、柱構造に沿って電流を流した際、界面(界面群)に於いて、ペルチェ効果による吸熱作用が発現する。

(もっと読む)

薄膜の加熱処理方法

【課題】 ランプアニールにより効果的に被処理膜を加熱処理するための方法を提供する。

【解決手段】 基板101の上面側からは紫外光ランプ104を用いて紫外光107が照射される。また、基板101の下面側からは赤外光ランプ108を用いて赤外光111が照射される。本発明では赤外光照射による振動励起効果に加えて紫外光照射による電子励起効果が付加されるため、被処理膜103の励起効率が大幅に高まり、効果的な加熱処理が可能となる。

(もっと読む)

薄膜トランジスタの作製方法

【課題】 しかし、薄膜トランジスタを有する表示装置では、同一対象物、例えば同一絶縁膜のエッチング条件を最適化することが難しかった。これは、同一絶縁膜において、エッチングする絶縁膜の膜厚や面積が異なるためである。特に面積の小さなコンタクトホールは、エッチングする量がその他の開口部と異なる。

【解決手段】 上記課題を鑑み本発明は、第1のマスクを用いて、第1の領域の対象物をエッチングして広面積な開口部を形成し、第2のマスクを用いて、第2の領域の前記対象物をエッチングして微細な開口部、つまりコンタクトホールを形成することを特徴とする。

(もっと読む)

41 - 58 / 58

[ Back to top ]