Fターム[5F033JJ03]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 半導体(基板を除く) (666)

Fターム[5F033JJ03]の下位に属するFターム

Fターム[5F033JJ03]に分類される特許

21 - 40 / 58

半導体装置

【課題】曲げ等の外力が加わり応力が生じた場合であってもトランジスタ等の損傷を低減する半導体装置を提供することを目的とする。

【解決手段】可撓性を有する基板上に設けられた第1の島状の補強膜と、第1の島状の補強膜上に、チャネル形成領域と不純物領域とを具備する半導体膜と、チャネル形成領域の上方にゲート絶縁膜を介して設けられた第1の導電膜と、第1の導電膜及びゲート絶縁膜を覆って設けられた第2の島状の補強膜とを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】ソースドレイン領域のサイズが増大することがない局所配線構造を備えた半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成されたゲート電極22及び半導体基板11におけるゲート電極22の両側方にそれぞれ形成された第1のソースドレイン領域29A及び第2のソースドレイン領域29Bを有するトランジスタ12と、半導体基板11の上における第1のソースドレイン領域29Aを挟んでゲート電極22と反対側に形成されたゲート配線42と、ゲート配線42と第1のソースドレイン領域29Aとを接続する局所配線構造60とを備えている。局所配線構造60は、第1のソースドレイン領域29A及びゲート配線42の上面に跨って形成されたSiGe層61によって構成されている。

(もっと読む)

半導体装置

【課題】SOI構造を有する半導体装置において、高性能化、低消費電力化を目的の一とする。また、より高集積化された高性能な半導体素子を有する半導体装置を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に複数の電界効果トランジスタがそれぞれ層間絶縁層を介して積層している半導体装置とする。複数の電界効果トランジスタの有する半導体層は半導体基板より分離されており、該半導体層は絶縁表面を有する基板、又は層間絶縁層上にそれぞれ設けられた絶縁層に接して接合されている。複数の電界効果トランジスタはそれぞれ前記半導体層に歪みを与える絶縁膜で覆われている。

(もっと読む)

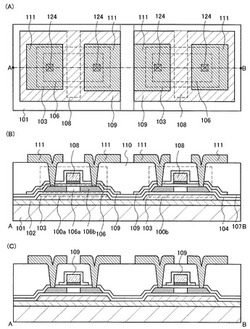

半導体装置およびその製造方法

【課題】ダイシング工程で発生する膜剥離やクラックがチップ内部に伝播するのを防ぐ。

【解決手段】半導体装置100は、基板102と、ビア層130および配線層132が形成される素子形成領域であるチップ内部202と、平面視においてチップ内部202を囲むようにチップ内部202の外周に形成されたシールリング部204と、を含む。シールリング部204において、シールリングは、平面視においてチップ内部202を囲むように形成された貫通孔122aを有する第1のメタル層122と、第1のメタル層122上に第1のメタル層122に接して形成された第2のメタル層124と、を含み、第1のメタル層122の貫通孔122aの下部分には絶縁性材料(層間絶縁膜106)が形成され、貫通孔122aの上部分には第2のメタル層124を構成するメタル材料がくい込んで形成される。

(もっと読む)

コンタクトスペーサを備えるコンタクト構造体の形成方法及びそれを用いた半導体素子の製造方法

【課題】コンタクトスペーサを備えるコンタクト構造体の形成方法及びそれを用いた半導体素子の製造方法を提供する。

【解決手段】本発明のコンタクト構造体の形成方法は、半導体基板上に層間絶縁膜を形成する工程と、層間絶縁膜をパターニングして半導体基板の所定領域を露出させるコンタクトホールを形成する工程と、半導体基板の主表面に対して傾斜した蒸着方向を有する蒸着法を用いてコンタクトホールの側壁にコンタクトスペーサを形成する工程と、を有する。このとき、蒸着方向は主表面と主表面に対する法線との間に位置する。それと共に、このコンタクト構造体の形成方法を用いた半導体素子の製造方法も提供される。

(もっと読む)

シード印刷及びめっきによるコンタクト金属及び相互接続金属の印刷

シリサイド形成金属を含むインクを用いて、コンタクト形成方法、そのコンタクト及び局所相互接続を含むダイオード及び/又はトランジスタ等の電気デバイスとその形成方法に関する。コンタクト形成方法は、露出したシリコン表面上にシリサイド形成金属インクを堆積させるステップと、インクを乾燥させ、シリサイド形成金属前駆体を形成するステップと、シリサイド形成金属前駆体及びシリコン表面を加熱して、金属スイサイドコンタクトを形成するステップとを含む。任意選択的に、露出したシリコン表面に隣接する誘電体層上に、金属前駆体インクを選択的に堆積させて、金属含有相互接続を形成できる。更に、1つ又は複数のバルク導電性金属を、残りの金属前駆体インク及び/又は誘電体層上に堆積させてもよい。かかる印刷したコンタクト及び/又は局所相互接続を用いて、ダイオード及びトランジスタ等を作製できる。 (もっと読む)

エッチング方法

【課題】銅薄膜にダメージを与えないエッチング方法を提供する。

【解決手段】本発明では処理対象物10上でフッ素系ガスのプラズマを発生させ、電極溝18内に露出する銅薄膜(例えばソース電極21、ドレイン電極22)にフッ素化合物薄膜を予め形成しておくので、ハロゲンガスのプラズマでシリコン層17をエッチングする際に、銅薄膜がハロゲンガスのプラズマで腐食されない。シリコン層17をエッチングした後に、O2ガスのプラズマに曝すか、水洗すれば、銅薄膜表面に残留するハロゲンガスが除去されるので保存性も高くなる。

(もっと読む)

配線及び記憶素子の作製方法

【課題】焼成を必要とする液滴吐出法をはじめとする塗布法において、配線や導電膜の作製時における焼成温度を低減することを課題とする。

【解決手段】液滴吐出法等の塗布法を用いて導電性材料よりなるナノ粒子が分散された組成物を吐出し、その後乾燥することで該溶媒を気化させる。そして、活性酸素による前処理を行った後、焼成を行うことで、配線もしくは導電膜を作製する。このように、焼成前に活性酸素による前処理を行うことで、作製時における焼成温度を低減することが可能となる。

(もっと読む)

半導体装置

【課題】アンテナを複数設ける場合であっても、アンテナの配置が制限されず集積回路部とアンテナの接続不良を低減し、且つ通信機との通信距離の低減を防止することが可能な半導体装置を提供することを目的とする。

【解決手段】絶縁性を有する基体の第1の面上に薄膜トランジスタを具備する集積回路部を設け、当該集積回路部上に第1のアンテナを設け、基体の第2の面上に第2のアンテナを設け、第1のアンテナを集積回路部と接続させ、第2のアンテナを基体に形成された貫通孔を介して集積回路部と接続させ、第1のアンテナ及び第2のアンテナを集積回路部と重畳させて設ける。

(もっと読む)

半導体装置の製造方法

【課題】自己整合コンタクトプラグを形成する層間膜に、酸化シリコン膜のエッチング速度に対するエッチング速度比が100以上となる材料を適用し、コンタクトプラグとワード配線、あるいはコンタクトプラグとビット配線のショートを防止する信頼性の高いコンタクトプラグの形成方法を提供する。

【解決手段】上面及び側面が酸化シリコン膜で覆われた配線105bを形成した後、配線を覆って全面にシリコンを含有しない有機塗布膜からなる犠牲層間膜132aを形成し、犠牲層間膜および下層絶縁膜を順次にエッチングしてコンタクトホール108を形成し、コンタクトプラグを形成する。その後、犠牲層間膜を除去してコンタクトプラグの柱を形成し、その上に層間絶縁膜106を形成し、さらに層間絶縁膜を表面から一部除去し、容量コンタクトプラグの表面を露出させるようにした。

(もっと読む)

半導体装置およびその作製方法

【課題】無線信号から生成できる電流値及び電圧値の範囲内で駆動できるメモリを搭載した半導体装置を提供することを課題とする。また、半導体装置製造後にデータの書き込みを行える追記型のメモリを提供することも課題とする。

【解決手段】絶縁表面を有する基板上にアンテナと、アンチヒューズ型のROMと、駆動回路とを形成する。アンチヒューズ型のROMを構成する一対の電極の間に、シリコン膜とゲルマニウム膜との積層を設ける。この積層を有するアンチヒューズ型のROMは、書き込み電圧のバラツキを低減することができる。

(もっと読む)

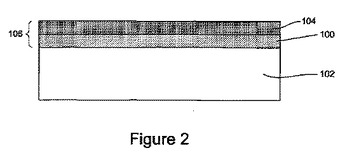

金属シリサイド晶子上にナノ構造物を形成する方法、並びにこの方法により得られる構造物及びデバイス

本発明の種々の実施形態は、非単結晶基板上にナノ構造物を形成する方法、並びにその結果得られるナノ構造物及びナノスケール機能デバイスに関する。本発明の一実施形態では、ナノ構造物を形成する方法は、金属層(100)及びシリコン層(104)を含む多層構造物(106)を形成することを含む。多層構造物(106)は、熱工程にかけられ、それにより金属シリサイド晶子(110)が形成される。金属シリサイド晶子(110)上にはナノ構造物(114)が成長される。本発明の別の実施形態では、構造物は、非単結晶基板(102)及び非単結晶基板(102)上に形成された層(108)を含む。層(108)は、金属シリサイド晶子(110)を含む。金属シリサイド晶子(110)上にいくつかのナノ構造物(114)が形成されてもよい。開示の構造物は、電子デバイス及び/又は光電子デバイスで使用されるいくつかの異なるタイプの機能デバイスを形成するために使用することができる。  (もっと読む)

(もっと読む)

基板貫通相互接続を形成する方法

少なくとも1つの基板貫通相互接続を形成する方法の一実施形態において、第1の表面202、及び反対側の第2の表面204を有する半導体基板200を提供する。半導体基板に、少なくとも1つの開口210を、半導体基板内で第1の面から中間深さまで延在するように形成する。少なくとも1つの開口は、基部216によって部分的に画定される。基部上に、少なくとも1つの金属触媒ナノ粒子220を提供する。金属触媒ナノ粒子によって導電性材料222の堆積が促進される条件下で、少なくとも1つの開口内に導電性材料を堆積させる。半導体基板の材料を第2の面から除去することにより、少なくとも1つの開口を充填する導電性材料の一部を露出させることができる(図3K)。別の実施形態では、ナノ粒子を使用する代りに、導電性材料を、少なくとも1つの開口を部分的に画定する基部に選択的に堆積するように選択することができる。  (もっと読む)

(もっと読む)

電気メッキによる垂直素子形成の方法および素子構造

【課題】電気メッキによって垂直導電構造を形成する方法に関する。

【解決手段】具体的には、まずテンプレート構造が形成され、該構造は、基板と、該基板の表面に配置された個別金属導体パッドと、個別金属導体パッドおよび基板を覆うインターレベル誘電体(ILD)層と、ILD層を貫通して個別金属導体パッド上に延びる金属穴構造とを含む。次に、テンプレート構造中に、IDL層を貫通し個別の金属導体パッド上に延びる垂直孔が形成される。しかる後、電気メッキにより垂直孔中に垂直導電構造が形成され、該電気メッキは、電気メッキ電流を金属穴構造を通して個別金属導体パッドに印加することにより実施される。望ましくは、該テンプレート構造は、複数の個別金属導体パッド、複数の金属穴構造、および複数の垂直導電構造を形成するための複数の垂直孔を含む。

(もっと読む)

貫通孔配線構造およびその形成方法

【課題】電気的性能の向上が図れる貫通孔配線構造およびその形成方法を提供することにある。

【解決手段】貫通孔配線構造は、ベース基板1の厚み方向に貫設した貫通孔10の内側に形成された貫通配線部2と、ベース基板の厚み方向の両表面側それぞれに貫通配線部2の端面および貫通孔10の周部に重なる形で形成されたパッド5a,5bとを備え、貫通配線部2においてパッド5a,5bそれぞれに接する端部からなるコンタクト部3a,3bが、貫通配線部2における他の部位である主部4よりも弾性率が高い導電性材料を用いて形成されている。

(もっと読む)

表示装置の作製方法、及びエッチング装置

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。

【解決手段】チューブを絶縁層の開口形成領域上に絶縁層に接して配置し、そのチューブを通して処理剤(エッチングガス又はエッチング液)を絶縁層に吐出する。吐出(された処理剤(エッチングガス又はエッチング液)によって、絶縁層を選択的に除去し、絶縁層に開口を形成する。従って、導電層上に開口を有する絶縁層が形成され、絶縁層下の導電層が開口の底面に露出する。露出された導電層と接するように開口に導電膜を形成し、導電層と導電膜を絶縁層に設けられた開口において電気的に接続する。

(もっと読む)

半導体素子及びその形成方法

【課題】下部領域にコンタクトを通じて電気的に連結される配線を形成する方法を提供する。

【解決手段】本発明の配線の形成方法は、複数の第1領域と、前記第1領域の間に各々配置された複数の第2領域とを有する基板上に絶縁膜を形成し、前記絶縁膜上に前記絶縁膜を貫通する第1コンタクトを通じて各々対応する前記第1領域に電気的に連結される複数の第1配線を形成し、前記第1配線の側面にスペーサを形成し、隣り合う前記スペーサの間の前記絶縁膜を除去して隣り合う前記第1コンタクトの間に対応する前記第2領域を露出する複数のコンタクトホールを形成し、対応する前記コンタクトホールを埋める複数の第2コンタクトを形成して対応する前記第2コンタクトに電気的に連結される複数の第2配線を形成することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、貫通電極を備えた半導体基板に、熱処理を行ったことによる応力の増大を抑制できる高信頼な半導体装置を提供する。

【解決手段】貫通電極の導電膜材料として、熱処理によって膜応力が一度引張応力側に変化してピークをもち、さらに高温熱処理によって圧縮応力側に変化する材料を用いる。半導体基板11を貫通する貫通電極15中の貫通導電膜12の成膜を複数回に分ける。例えば、第一層目導電膜12aの成膜の後には、膜応力がピークをもつ熱処理温度以上まで温度を上げて熱処理を行い、第一層目の導電膜の応力緩和の行う。そして、更に導電膜で貫通孔を埋め込む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】セル面積の縮小化とともに、シェアードコンタクト形成時のゲート電極側部に形成されたサイドウォールの膜減りによる半導体基板への突き抜けを防止する。

【解決手段】半導体基板上にゲート絶縁膜を介してゲート電極13が形成され、その両側にサイドウォール15,16が形成され、ゲート電極13両側の半導体基板にソース・ドレイン17,18が形成されている半導体基板上に、ゲート電極13、ソース・ドレイン17,18等を被覆する犠牲膜23を形成する工程と、犠牲膜23にゲート電極13上から一方側のソース・ドレイン18上を開口するシェアードコンタクト24を形成する工程と、シェアードコンタクト24の内部にゲート電極13と一方側のソース・ドレイン18に接続する導電性プラグ26を形成する工程と、犠牲膜23を除去する工程とを備えたことを特徴とする。

(もっと読む)

寸法測定パターン、及びその形成方法

【課題】 半導体装置に使用される寸法は、ますます微細化されている。寸法が微細化され、導電膜配線のエッチング時における下地膜のエッチングにより、導電膜配線パターンの寸法測定が正確に行えないという問題がある。

【解決手段】本発明の寸法測定パターンは、導電膜配線の寸法測定点となる導電膜配線の両端部を含む領域における下地膜を、導電膜配線のエッチングガスに対しエッチングされない材料とする。そのため測長SEMにて観察した時の2次電子画像のコントラスト波形が配線幅にあたるピークのみを安定して得られ、正確に導電膜配線の寸法測定が実施できる。

(もっと読む)

21 - 40 / 58

[ Back to top ]