Fターム[5F033JJ13]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | Au、Au合金 (649)

Fターム[5F033JJ13]に分類される特許

641 - 649 / 649

多層配線構造の製造方法

【課題】高集積化、微細化されたパターンにおいて、ビアホール等を良好に埋め込み、かつ電気抵抗率の低い埋め込み型の多層配線構造を提供する。

【解決手段】埋め込み型の多層配線構造の製造方法が、絶縁層に孔部を形成する工程と、孔部の表面に、物理的真空堆積法で、平均膜厚が0.2nm以上で10nm以下である触媒層6、または触媒層の平均膜厚が、触媒層の材料原子の1原子層以上で10nm以下である触媒層6、を形成する工程と、触媒層を触媒に用いた無電解めっき法により、孔部の表面に無電解めっき層7を形成する工程と、無電解めっき層をシード層に用いた電解めっき法で、孔部を電解めっき層8で埋め込む工程とを含む。

(もっと読む)

集積回路技術における超均一シリサイド

集積回路(100)の形成方法(900)およびその構造体が提供される。半導体基板(102)上にゲート誘電体(104)が形成され、半導体基板(102)上のゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)にソース/ドレイン接合部(504/506)が形成される。ソース/ドレイン接合部(504/506)上に超均一シリサイド(604/608)が形成され、半導体基板(102)の上方に誘電体層(702)が堆積される。次いで、誘電体層(702)に、超均一シリサイド(604/608/606)へのコンタクトが形成される。  (もっと読む)

(もっと読む)

半導体基板セグメント及びその製造方法並びに該セグメントを積層して成る積層半導体基板及びその製造方法

【課題】三次元積層に好適な半導体基板セグメント及びその製造方法並びに該セグメントを積層して成る積層半導体基板及びその製造方法を提供する。

【解決手段】半導体基板2のデバイス埋設側にデバイス3、感光性絶縁層4および配線5が設けられていると共に、基板端部側に第1の貫通微細導電体6が設けられている。また、デバイス電極と第1の貫通微細導電体6とが配線5により接続されている。さらにデバイス非埋設側の2bには、第1の貫通微細導電体6の先端である接続端6aが所定長さ突出すように形成されている。

(もっと読む)

多層配線構造の形成方法

【課題】SOG膜のSi原子と有機基(例えばCH3基)やH基の結合がアッシング時に切れるのを抑制して誘電率を低く抑える。

【解決手段】低誘電率の有機又は無機SOG膜にパターン化レジスト膜をマスクとしてエッチングを行って配線溝を形成し、この後、枚葉式ダウンストリーム型のプラズマアッシング装置を用いて、酸素ガスプラズマによるアッシング処理を例えば1.2Torrの圧力雰囲気下で施してレジスト膜を除去し、この後配線溝にバリヤメタル形成後、Cuを電界メッキ法にて埋設して配線を形成する。

(もっと読む)

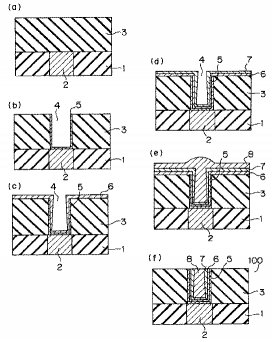

多層微細配線構造およびその作製方法

【課題】 高速情報処理用デジタル集積回路チップ内およびそのチップを搭載するためのパッケージ、モジュール、ボードなどの実装系内における多層配線の作製方法に関する新しい多層微細配線構造およびその作製方法を提案する。

【解決手段】 高解像感光性ポリイミドを絶縁層として、銅、銀、金、アルミニウム、パラジウム、ニオブなどの金属を配線層として用いて、ストリップライン、マイクロストリップライン、同軸ラインなどの伝送線路構造を有する多層微細配線構造を実現するため、広い周波数帯域について、インピーダンスが一定に制御され、デジタル高速信号伝送に適する線路を実現することができる。高解像特性を有する感光性ポリイミドを絶縁層として用いることにより、絶縁層へのビア穴加工がリソグラフィ工程のみで達成され、また、金属配線層をリフトオフ法によりパターン形成することにより、従来の多層配線技術に比べて、高密度の配線構造が実現でき、大幅に工程が簡略化される。

(もっと読む)

配線構造、その製造方法、および表示装置

【課題】 配線構造と他の電極間のショートを防ぐ。

【解決手段】 SiO2により構成されたゲート絶縁膜12およびその上に積層され、SiNにより構成された層間絶縁膜13に、緩衝フッ酸を用いたエッチングによりコンタクトホールを形成する。このコンタクトホールに、高融点金属により構成された第1の保護金属層170と、高融点金属よりも抵抗の低い金属により構成された配線層172と、および高融点金属により構成され、ゲート絶縁膜12よりも厚く形成された第2の保護金属層174とがこの順で積層された電極53を形成する。

(もっと読む)

半導体装置とその製造方法およびモノリシックマイクロ波集積回路

【課題】 強度低下や寸法増大を抑えながら、バイアホールの接地インダクタンスを低減できる半導体装置とその製造方法およびMMICを提供する。

【解決手段】 このマイクロ波帯用増幅器GaAsMMICは、その接地電極8が、3個のバイアホール11からなるバイアホール群12を有し、この3個のバイアホール11は、その内側に充填されたメッキ金属10aが近接されて形成され、その相互作用によって高周波的な電磁界結合が発生して、接地インダクタンスが低減された。

(もっと読む)

半導体チップ、配線基板およびそれらの製造方法ならびに半導体装置

【課題】複数の半導体チップを配線基板に積層しても、半導体チップを積層した半導体装置の厚みおよび基板面積の増大および半導体チップ間の配線長の増加を招かない半導体チップ、その製造方法および半導体装置等を提供する。

【解決手段】半導体基板13と、半導体基板13の第1の面14に形成された第1の外部電極21と、半導体基板13の第2の面17に形成された第2の外部電極22と、半導体基板13に形成された貫通孔16とを有し、貫通孔16は第2の面17となす内角が鈍角をなして形成された斜面15に設けられ、第1の外部電極21と第2の外部電極22とは、貫通孔16の内壁および斜面15を経由して形成された導電パターン19により電気的に接続されている。

(もっと読む)

配線構造及び配線形成方法

【課題】 電気的特性のみならず耐環境性にも優れた配線を実現し、ひいては当該配線を内装した半導体装置や配線基板等の信頼性の向上に寄与することを目的とする。

【解決手段】 絶縁層11,13に形成されたビア・ホールを介して下層の導体層12に電気的に導通するように絶縁層13と下層の導体層12とを覆って形成された金属薄膜14上に形成された配線層17の表面を、耐環境性に優れた材料からなる被覆層18で覆うように構成する。この被覆層18を構成する耐環境性に優れた材料としては、好適には、ニッケル/金、ニッケル/パラジウム、又はニッケル/パラジウム/金が用いられる。

(もっと読む)

641 - 649 / 649

[ Back to top ]