Fターム[5F033MM29]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 線幅の異なる複数の配線を有するもの (161)

Fターム[5F033MM29]に分類される特許

81 - 100 / 161

ヒロックの発生状況の評価パターン及びそれを備えた基板、並びに評価方法

【課題】本発明の課題は、ヒロックの発生状況をより効率的に把握することができる評価パターン及びそれを備えた半導体基板、並びに評価方法を提供することである。

【解決手段】本発明の評価パターン11は、ヒロック4の発生状況を評価する評価パターン11であって、絶縁膜12の上層に形成された所定の配線幅W1の環状配線13aと、環状配線13aの対向する2点間を縦横に接続する多数の格子配線13bとを有する格子状パターン13と、格子間に、環状配線13aと所定の隙間寸法L1をあけて配置された孤立配線14とを備える。

(もっと読む)

半導体装置

【課題】製造工程時間の増加を招くことなく、複数の凹部に埋め込まれた部材表面の平坦性を向上することのできる技術を提供する。

【解決手段】相対的に面積の大きい第1ダミーパターンDP1と相対的に面積の小さい第2ダミーパターンDP2とをダミー領域FAに配置することによって、素子形成領域DAとダミー領域FAとの境界BL近くまでダミーパターンを配置することができる。これにより、分離溝内に埋め込まれた酸化シリコン膜の表面の平坦性をダミー領域FAの全域において向上することができる。さらに、ダミー領域FAのうち相対的に広い領域を上記第1ダミーパターンDP1で占めることで、マスクのデータ量の増加を抑えることができる。

(もっと読む)

半導体装置の製造方法

【課題】記憶情報のセキュリティ性の高い半導体装置を製造工程数の増加を抑えて製造することのできる技術を提供する。

【解決手段】半導体基板10の主面に細い配線M1aと太い配線M1bとを形成した後、高密度プラズマCVD法によりこれら配線M1a,M1bを覆う絶縁膜26を堆積し、さらに遮光膜27および下層絶縁膜28aを順次堆積する。続いて下層絶縁膜28aの表面をCMP法により研磨して太い配線M1bの上の遮光膜27を露出させ、さらに太い配線M1bの上の遮光膜27を研磨して除去した後、上層絶縁膜28bを堆積する。続いて太い配線M1bの上の絶縁膜26および上層絶縁膜28bに、太い配線M1bに達する接続孔29aを形成した後、接続孔29aの内部にプラグ31を埋め込む。

(もっと読む)

半導体装置及びその製造方法並びに半導体製造装置

【課題】プログラムされた情報のセキリュティが高く、半導体チップ毎に異なる情報をプログラムすることを簡単に可能とすること。

【解決手段】本発明は、半導体ウエハ内に配列された複数の半導体チップとなるべき領域12内にそれぞれ設けられたOTP−ROMセル配列21に対応するプログラムドット配列を有するプログラムヘッド80を、複数の半導体チップとなるべき領域12のうち1つの領域内のOTP−ROMセル配列21に合わせる工程と、プログラムヘッド80を用いOTP−ROMセル配列21を、複数の半導体チップとなるべき領域12ごとに異なるパターンでプログラムする工程と、を有することを特徴とする半導体装置の製造方法である。

(もっと読む)

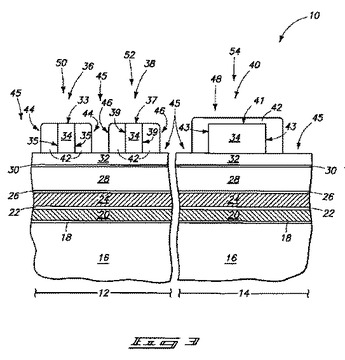

融合金属層を使用しているオン抵抗の低い電力用FET

【課題】追加金属層を使用してFETのオン抵抗を下げるための高電力用電界効果トランジスタ(FET)を提供する。

【解決手段】或る実施形態では、高電力用FETの上に載っている比較的薄いが幅の広いバス条片が形成され、ソース及びドレインの幅の狭い金属条片に電流を導電している。不動態化層は、FETの表面を覆って形成され、不動態化層は、エッチングされてバス条片の上面全体の殆どを露出させる。銅のシード層が、ウェーハの表面を覆って形成され、更にマスクが形成されて、バス条片上のシード層のみが露出される。次に、バス条片上のシード層に、銅又は金電気メッキが施されて、非常に厚い金属層が堆積され、これが下層の金属の層と効果的に融合して、オン抵抗を低下させる。メッキ金属は、その厚さと幅の広いライン/空間のために、不動態化を施す必要は無い。露出したバス条片を覆って厚い金属を堆積するのに、他の技法を使用することもできる。

(もっと読む)

半導体装置およびその製造方法

【課題】配線間の容量の低減および配線抵抗のばらつきの低減が図られる半導体装置とその製造方法を提供する。

【解決手段】下部配線4を直接覆うようにシリコン窒化膜などの接続孔ストッパ膜6を形成する。その接続孔ストッパ膜を直接覆うように下部層間絶縁膜8を形成する。その下部層間絶縁膜を直接覆うように下部層間絶縁膜とはエッチング特性の異なる上部層間絶縁膜10を形成する。その上部層間絶縁膜10に異方性エッチングを施すことにより上部配線溝18を形成する。その上部配線溝18に上部配線20を形成する。

(もっと読む)

電子装置、薄膜トランジスタ構造体及びそれを備える平板ディスプレイ装置

【課題】電子装置、薄膜トランジスタ構造体及びそれを備える平板ディスプレイ装置を提供する。

【解決手段】層を異ならせて互いに交差する二層以上の導電層を備える電子装置、薄膜トランジスタ構造体及びそれを備える平板ディスプレイ装置において、導電層のうち少なくとも何れか一層は、長手方向に沿って幅を異ならせる幅変動部を備え、幅変動部を備える導電層240と隣接する導電層のうち、少なくとも何れか一つには、これら導電層同士が交差しないその一つの導電層の非交差部に静電気を誘発させる電荷を集中させるためのダミー部241が備えられることを特徴とする。

(もっと読む)

アレイ基板

【課題】 アレイ基板において、電源ライン等の大電流を流す必要のある配線についても、製造コストやスループット等に影響を与えることなく線幅を削減可能とする。

【解決手段】 表示部の周辺に複数の配線層(第1配線27及び第2配線29)を有して構成される回路部を有するアレイ基板である。第1配線27と第2配線29は、互いに連続的に重なるように配置された2層重ね配線部30を有し、配線の重なり部(2層重ね配線部30)が1本の配線として機能する。この2層重ね配線部30は、電源ライン等として利用される。

(もっと読む)

薄膜トランジスタアレイ基板、その製造方法および液晶表示装置

【課題】TFTアレイ基板において、各配線間のクロストークを低減する。

【解決手段】TFTアレイ基板は、透明基板上に配置され、ゲート電極4aが分岐して延在するゲート配線1と、下部絶縁膜を介してゲート電極4aの上方を覆う半導体層3と、半導体層3を介してゲート電極4aの上側にそれぞれ一部が重なりかつゲート配線1とは交差しないようにそれぞれ別個に配置されたソース/ドレイン電極4b,4cと、ソース/ドレイン電極4b,4cを覆う上部絶縁膜と、この上部絶縁膜の上側においてゲート配線1と交差する方向に配置され、ソース電極4bに接続された上部ソース配線8と、ドレイン電極4cに電気的に接続された透明な画素電極11とを備え、少なくともゲート配線1と上部ソース配線8とが交差する交差部21では、ゲート配線1と上部ソース配線8との間に上記上部絶縁膜が配置されている。

(もっと読む)

半導体集積回路及び入出力セルの信号端子設計方法

【課題】信号端子を有する入出力セルを備えた半導体集積回路において、前記入出力セルの信号端子が接続用配線ヴィアを介して内部回路に接続される場合に、そのヴィアの原子の移動に起因するオープン不良を有効に防止する。

【解決手段】入力/出力セル2の信号端子3Aは、複数層(例えば4層)の導電層で形成される。その複数層の導電層の隣接する導電層同士は、ヴィアで接続される。前記複数層の導電層のうち、最大径のヴィア6−3で接続される導電層(例えば第4層の導電層)3−4では、その導電層3−4の幅が前記最大径のヴィア6−3を1個だけ配置できる幅に設定される。従って、接続用配線4から入力/出力セル2の入力端子3Aに原子が移動することが抑制され、前記接続用配線4に形成されるヴィア(図示なし)のオープン不良が有効に防止される。

(もっと読む)

半導体構造、複数のラインを形成する方法、および高密度構造と低密度構造を単一フォトマスクで形成する方法

いくつかの実施形態は、犠牲材料に沿ったポリマースペーサーの形成、犠牲材料の除去、および集積回路の製造中におけるマスクとしてのポリマースペーサーの利用、を含む。ポリマースペーサーマスクは、例えばフラッシュメモリアレイのフラッシュゲートをパターン化するために利用されてもよい。いくつかの実施形態では、ポリマーは大きな犠牲構造と小さな犠牲構造にわたって同時に形成される。ポリマーは、小さな犠牲構造にわたってよりも、大きな犠牲構造にわたっての方が厚く、こうした厚さの差を利用して、高密度構造と低密度構造を単一フォトマスクで製造する。  (もっと読む)

(もっと読む)

半導体装置の製造方法及びトランジスタの製造方法

【課題】溝の埋め込み性を改善することと、溝の埋め込み高さを確保することを両立させることができる半導体装置の製造方法を実現する。

【解決手段】半導体装置の製造方法として、半導体基板1上の層間膜2に幅の異なる溝3,4を形成する工程と、溝3,4が形成された層間膜2上にバリアメタル層5を形成する工程と、バリアメタル層5を覆いかつ溝3,4の形成部位に開口部を有するレジストマスク7を形成する工程と、レジストマスク7を用いてバリアメタル層5をエッチングすることによりオーバーハング部6を除去する工程と、レジストマスク7を除去した後、半導体基板1上で溝3,4に配線材料を埋め込む工程と、半導体基板1上で配線材料とバリアメタル層5の余剰部を研磨により除去する工程とによって溝配線を形成する。

(もっと読む)

ライン抵抗ばらつきを伴う配線構造

【課題】ライン抵抗のばらつきを抑制する配線構造を提供する。

【解決手段】半導体デバイスが提供される。この半導体デバイスは、カーボン・ドープのシリコン酸化膜の領域により分離される密に詰まったラインの領域と孤立ラインを含む領域とを含む。半導体デバイスの表面がエッチされるにつれ、エッチ・レートは、エッチされる材料に応じて変化する。それに応じて、孤立ラインの断面積は、その領域における遅いエッチング・プロセスを補償するために調節される必要がある。密に詰まったラインは、高さ、a、そして幅、b、を有し、そのためa*bの断面積を有する。しかしながら、孤立ラインは、高さ、D*a、そして幅、E*b、を有する、ここでD*E=1である。1つの又は複数のエッチング・プロセスが使用されることができ、それに応じてライン幅が調節される。

(もっと読む)

半導体装置及びその製造方法

【課題】2回以上のリソグラフィとエッチングを行って単一の配線層を形成する際に、パターンの重複部におけるレジスト残渣の発生を抑制し、安定した電気的特性を得る。

【解決手段】半導体装置は、第1パターン領域における絶縁膜12の表面に形成され、側壁にテーパを有する第1の深さD1の第1の配線溝と、第2パターン領域における絶縁膜12の表面に形成され、第1の配線溝よりも深い第2の深さD2の第2の配線溝と、上記第1,第2パターン領域の境界領域における絶縁膜の表面に形成され、第2の配線溝内に第2の配線溝よりも深い第3の深さD3で第1の配線溝のパターンが重複し、第2の配線溝の底面にテーパを持った側壁の段差部を有する第3の配線溝と、第1乃至第3の配線溝に埋め込まれる単一の配線層M1とを備える。

(もっと読む)

半導体装置および集積回路

【課題】TFTを電気的に駆動する場合にチャネル領域から発生する熱は、例えばゲート絶縁膜などの酸化シリコン膜を介して放熱していくが、酸化シリコンの熱伝導率は1.3W/(m・K)であり、シリコンの熱伝導率148W/(m・K)と比べ2桁以上低くTFTからの放熱が妨げられるため、熱の蓄積による温度上昇に伴うリーク電流の増加などTFT電気的特性の変動を抑えることが困難となる課題がある。

【解決手段】バッファ領域13上に配線22を配置する。チャネル21で消費された電力は熱に変わり、ソース18を介してバッファ領域13側に伝導され、配線22に伝導されて外部に放出される。バッファ領域13上にゲート絶縁膜14と層間絶縁膜16を介して配線22を通すことでチャネル21で発生した熱を効果的に逃がし、また配線22を設けることで集積度を向上させた半導体装置および集積回路を得ることができる。

(もっと読む)

半導体素子及びその形成方法

【課題】下部領域にコンタクトを通じて電気的に連結される配線を形成する方法を提供する。

【解決手段】本発明の配線の形成方法は、複数の第1領域と、前記第1領域の間に各々配置された複数の第2領域とを有する基板上に絶縁膜を形成し、前記絶縁膜上に前記絶縁膜を貫通する第1コンタクトを通じて各々対応する前記第1領域に電気的に連結される複数の第1配線を形成し、前記第1配線の側面にスペーサを形成し、隣り合う前記スペーサの間の前記絶縁膜を除去して隣り合う前記第1コンタクトの間に対応する前記第2領域を露出する複数のコンタクトホールを形成し、対応する前記コンタクトホールを埋める複数の第2コンタクトを形成して対応する前記第2コンタクトに電気的に連結される複数の第2配線を形成することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置のゲートパターンの寸法精度を高める。

【解決手段】複数のゲートパターンを含む所定のパターンを形成する際に、微細ゲートパターンとそれ以外のパターンとに分類し(S102)、被加工膜上に、ハードマスク膜を形成する(S106)。つづいて、ハードマスク膜上に微細な第1のパターンを有する第1のレジスト膜を形成してハードマスク膜をパターニングする(S108)。その後、ハードマスク膜上に別のパターンを有するレジスト膜を形成して、ハードマスク膜とレジスト膜とをマスクとして被加工膜を選択的にドライエッチングする(S110およびS112)。

(もっと読む)

半導体装置

【課題】インダクタ素子を有する半導体装置において、インダクタにより占有される面積を縮小し、かつ、該インダクタ配線における電流エレクトロマイグレーション耐性を向上させ、かつ好ましくない寄生容量の増加を抑制する。

【解決手段】膜厚の厚い金属配線1により上層インダクタ部を形成する。膜厚が薄い下層の金属配線2と金属配線3とを並列接続して下層インダクタ部を形成する。上層インダクタ部と下層インダクタ部とを層間プラグ4により直列接続する。最下層の金属配線3の配線幅を狭くする。

(もっと読む)

半導体装置及びその製造方法

【課題】コーナーラウンディング現象に起因するゲート電極寸法の変化及びトランジスタ特性の劣化を防止することができるゲート電極を備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、素子分離領域102と、素子分離領域102に囲まれた活性領域103と、素子分離領域102及び活性領域103上に形成されたゲート電極105とを備える。素子分離領域102上のゲート電極105における上面のゲート長方向の線幅LbTは、活性領域103上のゲート電極105における上面のゲート長方向の線幅LaTとほぼ等しく、素子分離領域102上のゲート電極105における下面のゲート長方向の線幅LbBは、活性領域103上のゲート電極105における下面のゲート長方向の線幅LaBよりも長い。

(もっと読む)

半導体装置の製造方法

【課題】多層レジストを用いたエッチングにおいて、被エッチング膜に所望のパターンを形成する。

【解決手段】半導体装置の製造方法は、絶縁膜に形成する配線パターンの中で配線ピッチが最も小さい配線パターンの配線ピッチが所定値以下か否かを判断する工程(S100)と、配線ピッチが所定値以下か否かを判断する工程において、配線ピッチが所定値以下であると判断された場合、当該配線ピッチに応じて下層レジスト膜の膜厚を決定する工程(S104)と、絶縁膜上に、ステップS104で決定された膜厚の下層レジスト膜を形成する工程(S106)とを含む。

(もっと読む)

81 - 100 / 161

[ Back to top ]