Fターム[5F033MM29]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 線幅の異なる複数の配線を有するもの (161)

Fターム[5F033MM29]に分類される特許

121 - 140 / 161

半導体装置およびその作製方法

【課題】工程数を増やすことなく、段切れ不良、及びコンタクト不良を防ぐ方法を提供し、それにより動作性能および信頼性の高い集積回路を作製することを課題とする。

【解決手段】配線の乗り越え部分において、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを配線形成用のフォトリソグラフィ工程に適用し、2層構造の下層配線となる導電層を形成し、下層配線が下層配線1層目と、1層目の幅より短い2層目の幅を有するようにレジストパターンを形成し、急峻な段差を緩和することを目的とした下層配線を形成する。

(もっと読む)

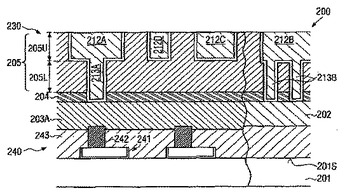

ダミービアの供給によりメタライゼーション層の密着性を向上させる技術

電気的に機能しない金属領域(212B、312B)の下方にダミービア(213B、313B)を供給することにより、後続のプロセスにおいて、金属が層間剥離する危険性が著しく低下する。更に、一実施形態では、形成されるメタライゼーション層(330)の機械的強度は、機能しないオーバーレイ金属領域(312B)のアンカーとしての役割を果たすダミー金属領域(303B)を供給することでさらに一層強化される。加えて、ダミービア(213B、313B)はさらに、電気的に機能する金属領域(212A、212C、212D、312A)と、領域(220A、320A)とともに供給され、これにより、機械的安定性とその電気的パフォーマンスも強化される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 切断された電気ヒューズの切断状態を良好に保つ。

【解決手段】 半導体装置100は、半導体基板(不図示)上に形成されるとともに凹部が形成された第1の絶縁膜102と、導電体206、ならびに導電体206の一端と他端にそれぞれ設けられた第1の端子202および第2の端子204を有し、第1の絶縁膜102上に設けられた電気ヒューズ200とを含む。導電体206は、第1の絶縁膜102の凹部を埋め込むように形成されるとともに、導電体206を構成する材料が凹部外に流出した流出領域212を有し、流出領域212とは異なる箇所が切断される。

(もっと読む)

半導体装置の製造方法

【課題】銅配線形成時のディッシングを防止する。

【解決手段】半導体基板12上面12a上の第1絶縁膜14の表面を覆う拡散防止膜22、拡散防止膜上を覆う第2絶縁膜24、及び第2絶縁膜上を覆うキャップ膜26を順次に積層する。拡散防止膜、第2絶縁膜及びキャップ膜を貫通する配線溝部30であって、この配線溝部の底面からキャップ膜の表面までの高さh1に対する、配線溝部の延在方向に直交する方向の幅w1の比率を最大でも2.8倍として当該配線溝部を形成する。キャップ膜の表面及び配線溝部の表面を覆うバリアメタル膜を形成する。バリアメタル膜上を覆う配線膜を成膜する。配線膜の表面からキャップ膜の表面が露出するまで、配線膜及びバリアメタル膜を削り取って、配線溝部を埋め込む配線部を形成する。

(もっと読む)

LDMOSトランジスタ

本発明のLDMOSトランジスタ(1)は、基板(2)、ゲート電極(10)、基板コンタクト領域(11)、ソース領域(3)、チャネル領域(4)、ならびに、ドレインコンタクト領域(6)およびドレイン拡張領域(7)を具えるドレイン領域(5)を具える。前記ドレインコンタクト領域(6)は、前記ドレイン拡張領域(7)の上方に延在するトップメタル層(23)に電気的に接続され、前記トップメタル層(23)と前記ドレイン拡張領域(7)との間に、2μmよりも大きい距離(723)を有する。このように、前記ドレインコンタクト領域(6)の面積を減少させることができ、前記LDMOSトランジスタ(1)のRF電力出力効率を増加させることができる。別の実施形態において、前記ソース領域(3)は、第1メタル層(21)の代わりに、ケイ素化合物層(32)を介して前記基板コンタクト領域(11)に電気的に接続され、それによって、前記ソース領域(3)と前記ドレイン領域(5)との間の静電結合を減少させ、それゆえに、前記LDMOSトランジスタ(1)のRF電力出力効率を増加させる。  (もっと読む)

(もっと読む)

薄膜トランジスター基板及びその製造方法

【課題】フレキシブル基板を用いた液晶表示装置の製造工程に際し、基板の膨張及び収縮による誤整列に備えることを可能にする。

【解決手段】ベース基板110上に形成されたゲートライン120と、ゲートラインと絶縁されて形成されたデータライン、及びゲートラインとデータラインとが交差する領域に形成され、ゲートラインの線幅は少なくとも前記データラインの線幅よりも大きく形成される薄膜トランジスターと、を備え、データラインは、前記ゲートラインと絶縁されて交差する第1のデータライン160a、160cと、第1のデータラインと交差し、その一端が第1のデータラインと電気的に接続される第2のデータライン160bと、を備え、薄膜トランジスターのドレイン電極170は、データラインと所定の間隔だけ離して配置されることを特徴とする。

(もっと読む)

電子基板とその製造方法及び電気光学装置並びに電子機器

【課題】 高精度の抵抗部を容易に形成する。

【解決手段】 基板P上に配線パターン20、21が設けられる。配線パターン20、21の一部の配線諸元を、他の部分と異ならせて設けられた抵抗素子Rを有する。

(もっと読む)

膜パターンの形成方法、デバイス、電気光学装置、及び電子機器

【課題】 幅の異なる幾つかの領域を有するパターン形成領域に機能液を配置する場合等において、形成される膜パターン間での膜厚さを無くした該膜パターンの形成方法を提供する。

【解決手段】 本発明の膜パターンの形成方法は、基板48上に所定パターンのバンク34を形成するバンク形成工程と、前記形成したバンク34に対してフッ素化処理を施す撥液化処理工程と、前記撥液化処理後、前記バンク34に区画されたパターン形成領域55,56に機能液を配置する機能液配置工程と、前記配置した機能液を乾燥させる乾燥工程と、を含み、前記バンク形成工程は、前記基板48上に第1バンク層34aを形成する第1バンク層形成工程と、前記形成した第1バンク層34a上に、該第1バンク層34aよりもフッ素化され易い第2バンク層34bを形成する第2バンク層形成工程と、を含むことを特徴とする。

(もっと読む)

半導体集積装置の製造方法

【課題】半導体集積装置内の配線に生じる応力の集中を緩和して、その電気的な信頼性を高く維持することのできる半導体集積装置及びその製造方法を提供する。

【解決手段】CCDイメージセンサの形成された半導体チップ100と同半導体チップ100と図示しないガラス基板とを貼り合せるエポキシ樹脂310との上には、シリコン酸化膜120が形成されている。そして、このシリコン酸化膜120上には、外部配線410を介して、外部端子と半導体チップ100に形成された上記CCDイメージセンサとのコンタクトをとる内部パッド140が形成されている。この内部パッド140には、同内部パッド140の電極幅よりも線幅の細い内部配線150が接続されている。この内部パッド140は、半導体チップ100の上方に迫り出すように形成されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線形成のためのドライエッチングが進行しても、ゲート絶縁膜にチャージダメージを与えることを抑制できる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、ゲート絶縁膜3a,3bを形成する工程と、ゲート配線4a,4bを形成する工程と、絶縁膜8を形成する工程と、接続孔8a,8b,8cを形成する工程と、接続孔8a,8b,8cに導電体9a,9b,9cを埋め込む工程と、絶縁膜8上及び導電体9a,9b,9c上に、導電膜11,12,13を形成する工程と、ドライエッチングを用いて導電膜11,12,13をパターニングすることにより、絶縁膜8上に複数の配線10a,10b,10d、及びダミー配線10cを形成する工程とを具備する。ダミー配線10cと、ダミー配線10cに最も近い配線10bの間隔は、配線10a,10b,10dの相互間隔以下である。

(もっと読む)

膜パターンの形成方法、半導体装置、電気光学装置、及び電子機器

【課題】 バンクに撥液化処理を行う際の、機能膜へのダメージを解消した膜パターンの形成方法と、これによって得られた膜パターンを備えた半導体装置、電気光学装置、及び電子機器を提供する。

【解決手段】 基板Pに設けられたゲート絶縁膜28(機能膜)上に機能液を配置して膜パターンを形成する方法である。基板Pにゲート絶縁膜28を設け、ゲート絶縁膜28上にポリシラザン液、ポリシラン液またはポリシロキサン液のいずれかを塗布し乾燥してバンク膜31を形成する。そして、マスクMを用いてバンク膜31を選択的に露光し、バンク膜31に撥液処理を施す。バンク膜31を現像処理することでゲート絶縁膜28を露出させ、パターン形成領域を区画するバンクを形成する。パターン形成領域に前記機能液を配置し、膜パターンを形成する。少なくとも、バンク膜31に撥液処理を施す工程は、バンク膜31を現像処理しバンクを形成する工程より前の工程で行う。

(もっと読む)

不揮発性記憶素子とその製造方法

【課題】 本発明は上記の問題に鑑みてなされたものであり、その目的は、情報の書込み時及び消去時における過渡電流を小さくし、消費電流を低減することができる不揮発性記憶素子及びその製造方法を提供する点にある。

【解決手段】 電気抵抗状態の高低を情報として記憶することができる可変抵抗体4と、可変抵抗体4に接する複数の電極2を備えてなる不揮発性記憶素子であって、複数の電極2の内の少なくとも1つの電極2の可変抵抗体4との接触面積が、不揮発性記憶素子の作製に用いる製造プロセスの最小加工寸法の2乗よりも小さいことを特徴とする。

(もっと読む)

接続バンプによって引き起こされるインピーダンスばらつきを減ずるために集積回路内で導電体を構成するためのシステムおよび方法

【課題】改善された半導体装置性能のためのシステム及び方法の提供。

【解決手段】接続バンプの近接及び/又は密度及び/又は動作により引き起こされるインピーダンスばらつきを減ずるための導電体を構成するための改良された半導体システム及び方法である。本発明は半導体装置に何らの機能も付加しないインピーダンス減少導電性要素を付加することを含む。付加される要素は疎接続バンプ密度領域内に配置される。インピーダンス減少導電性要素は、機能的金属線相互間に付加された金属線を含み得る。隣接する動作線間への配置は様々である。インピーダンス減少導電性要素は、導電層の任意の1つまたは組み合わせに対して付加され得、付加される要素は、機能的な要素の任意の1つまたは組み合わせに作用し得る。付加される要素は、電気的に動的で半導体装置の動作に応答してもよい。また、接続バンプ密度を決定するための自動化され得る方法。

(もっと読む)

半導体装置

【課題】ワイヤボンディング法を用い、高速LSIが形成された半導体チップを搭載するパッケージを形成する手段を提供する。

【解決手段】半導体チップ42と、半導体チップ42の主面42aより小さいダイパッド41aと、封止体43と、外部端子部41cとインナリード部41bとからなる複数のリード41dと、半導体チップ42のボンディングパッド42cとインナリード部41bとを接続する複数のボンディングワイヤ44とからなり、複数のインナリード部41bの各々が封止体43の実装面43aから離れる方向に折り曲げられていることにより、チップ側のボンディングパッド42cとインナリード部41bのボンディング位置の高さを近づけてワイヤ長さを短くすることができ、ワイヤ部分のインダクタンスの増加を抑えて高周波信号の入出力の伝送経路の各部におけるインピーダンスの整合をとることができる。

(もっと読む)

半導体装置

【課題】 電流密度の部分的な集中を防止して、より小面積でより大電流を駆動可能にする。

【解決手段】 複数の半導体素子を並列に接続する第1配線16及び第2配線17を、複数の配線層により構成する。各配線層は、第1配線16及び第2配線17を交互に且つ平行に形成してなる。隣接する配線層間では、上下の配線が互いに交差するように形成されると共に、第1配線16の交差部及び第2配線17の交差部でそれぞれ第1配線16同士及び第2配線17同士が層間接続部165,166,175,176によって接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 製造工程における機械的強度を強くするとともに、配線間絶縁膜を低誘電率化する。

【解決手段】 本発明の半導体装置の製造方法は、以下の手順を含む。まず高密度絶縁膜を形成する(S102)。つづいて、高密度絶縁膜にビアホールおよび配線溝を形成する(S104)。次いで、ビアホールおよび配線溝を埋め込むように、配線およびビア金属膜を形成する(S106)。その後、CMPにより、配線溝外部に露出した金属膜を除去する(S108)。つづいて、Heプラズマ照射またはエネルギー線照射により、高密度絶縁膜表面を低密度化する(S110)。その後、低密度化された絶縁膜上にエッチングストッパ膜(またはキャップ膜)を形成する(S112)。

(もっと読む)

インク吐出パターン、線パターンおよび線パターン形成方法

【課題】 互いに接続されたインク領域においてインク領域間のインクの流れ出しを防止したインク吐出パターンを提供する。

【解決手段】 基板上に形成されるインクを吐出すべき第であって、互いに接続して形成される第1のパターン形成部10であって、それぞれライン状の太線部11と細線部12とを有する第1のパターン形成部10において、太線部11と細線部12との間に、太線部11との接続部における幅が太線部11よりも狭いと共に、細線部12との接続部における幅が細線部12よりも狭い、液滴流動阻止部13を設けている。

(もっと読む)

集積回路製造

集積回路(100)のパターンを作成する方法であって、基板(108)の第1の領域(102)にフォトリソグラフィーを用いて、第1のフォトレジスト層の複数の特徴物を作成することを含む。この方法は更に、フォトレジスト層内の特徴物の各々に対してピッチ増倍(multiplication)を用いて少なくとも2つの特徴物(120)を下方マスキング層(116)に形成することを含む。下方マスキング層内(116)の特徴物は、ループ状の端部(124)を有する。この方法は更に、下方マスキング層(116)上のループ状の端部(124)を含み、基板(108)の第2の領域(104)を第2のフォトレジスト層(126)で覆うことを含む。この方法は更に、基板(108)上に、第2の領域をエッチングせずに下方マスキング層上の特徴物を介して、溝のパターンをエッチングすることを含む。これらの溝は溝幅を有する。 (もっと読む)

プラズマ酸化および酸化材料の除去

【課題】プラズマ酸化および酸化材料の除去

【解決手段】導電層をエッチングする方法は、導電層の少なくとも一部を転換し、導電層の転換部分を実質的に除去し、残存表面を露出させるために、導電層をエッチングすることを含む。残存表面は、約10nm未満の平均表面粗さを有する。導電層をエッチングするための方法も開示される。

(もっと読む)

自動配置配線装置

【課題】信号線配線後の配線可能な空き領域に電源配線を自動的に追加挿入することのできる自動配置配線装置を得ること。

【解決手段】一連の配線処理終了後のレイアウトにおいて配線可能な空き領域30を特定し、その空き領域30に接続できる配線済みの電源配線が含まれているか否かを調べ、含まれている場合は挿入し、含まれていない場合は配線済みの信号線を移動して配線済みの電源配線が含まれるようにしてから挿入するなど、その空き領域30に人手を介さずに電源配線を挿入する。これによって、人手による作業を発生させること無しに電源配線の容量を増加し、電圧降下を抑えることができる。

(もっと読む)

121 - 140 / 161

[ Back to top ]