Fターム[5F033MM29]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 線幅の異なる複数の配線を有するもの (161)

Fターム[5F033MM29]に分類される特許

21 - 40 / 161

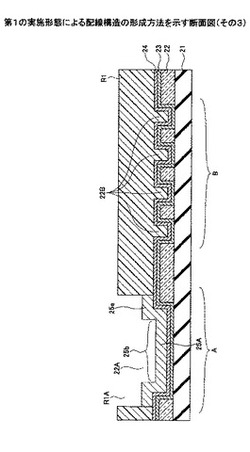

配線構造の形成方法および配線構造

【課題】太い幅の配線溝と細い幅の配線溝をCuの電解メッキで充填する際に、アンダープレートの発生を抑制し、化学機械研磨後におけるディッシングの発生を抑制する。

【解決手段】表面の第1の領域に縦/横比小さい第1の配線溝22Aが形成され、表面の第2の領域に縦/横比が大きい第2の配線溝22Bを形成された絶縁膜の表面上にレジスト膜R1を形成し、第1の領域を露出する第1のレジスト開口部R1Aを形成する工程と、レジスト膜をマスクに電解メッキを行い、第1の配線溝を第1の配線パタ―ン25Aで充填する工程と、第2の領域を露出する第2のレジスト開口部を形成する工程と、レジスト膜をマスクに電解メッキを行い、第2の配線溝を第2の配線パタ―ンで充填する工程と、レジスト膜を除去し、第1の配線パタ―ンおよび第2の配線パタ―ンを、それぞれの表面が絶縁膜の表面に一致するように、化学機械研磨により平坦化する工程と、を含む。

(もっと読む)

配線形成方法

【課題】配線層で、配線密度の高い領域では隣接する配線間のショートを防ぎ、配線密度の低い領域では所望の平坦度が得られるとともに所望の配線抵抗が得られるように配線高さを制御できる配線形成方法を提供する。

【解決手段】まず、基板上に第1の絶縁膜111と、第1の絶縁膜111に比してCMP研磨レートの小さい所定の厚さの第2の絶縁膜112を順に積層させて層間絶縁膜11を形成し、ついで、層間絶縁膜11の第1の領域に第1の配線密度となり、第2の領域に第1の配線密度よりも低い第2の配線密度となるように、第2の絶縁膜112を貫通し、底部が第1の絶縁膜111に至る配線形成用溝21を形成した後、配線形成用溝21を形成した層間絶縁膜11上に導電性材料膜14を形成し、そして、CMP法によって、少なくとも第1の領域で第1の絶縁膜111が露出、後退するように層間絶縁膜11と導電性材料膜14を研磨する。

(もっと読む)

半導体集積回路およびそのパターンレイアウト方法

【課題】CMP処理においてダミーパターンに機械的ストレスが作用しても、ダミーパターンが折れ曲がったり、ダミーパターンの一部が欠落したりすることを抑制できる半導体集積回路およびそのパターンレイアウト方法を提供する。

【解決手段】半導体集積回路は、所定の機能領域と、空き領域SP1に形成されたダミーパターンDMP1とを備える。空き領域SP1は、所定の機能領域同士の間に位置する。ダミーパターンDMP1は、枠状に形成されるとともに、ダミーパターンDMP1の外縁EDを規定する第1メタル部MT1と、第1メタル部MT1の内周側に位置し、第1メタル部MT1に連続するように形成された第2メタル部MT2と、第1メタル部MT1の内周側において第2メタル部MT2が形成されていない領域に位置する複数の非形成領域NTと、を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の広幅の配線におけるディッシングの抑制と、抵抗の抑制と、を両立させる。

【解決手段】半導体装置100は、半導体基板1と、半導体基板1上に形成された配線層絶縁膜9と、を有している。配線層絶縁膜9には、第1配線用配線溝11と、第1配線用配線溝11よりも広幅の第2配線用配線溝12と、が形成されている。第1配線用配線溝11内には第1配線21が、第2配線用配線溝12内には第2配線22が、それぞれ形成されている。第2配線用配線溝12の底面の少なくとも一部分は、絶縁膜(例えば、絶縁膜4及びエッチングストッパー膜5)によって、第2配線用配線溝12の上端に達しない高さで第1配線用配線溝11の底面よりもかさ上げされた、かさ上げ部15となっている。

(もっと読む)

半導体装置

【課題】並列に並ぶゲートパターンを有する半導体装置において、ゲートパターンのレイアウトを工夫することによって、光近接効果を補正しつつ、集積度を向上させる。

【解決手段】並列に並ぶゲートパターン21,22の端部と、並列に並ぶゲートパターン23,24の対向端部とにおいて、ゲートパターン21の端部はゲートパターン22の端部よりもゲートパターン23,24の方に突き出ており、ゲートパターン24の対向端部はゲートパターン23の対向端部よりも、ゲートパターン21,22の方に突き出ている。引っ込んでいる方の、ゲートパターン22の端部およびゲートパターン23の対向端部について、仕上がり形状において後退が生じない程度に、補正量を大きく設定することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ディッシングを抑制することができる半導体装置の構造を実現する。

【解決手段】半導体装置200は、基板(シリコン基板)と、基板上に設けられた絶縁層(層間絶縁膜201)と、層間絶縁膜201に設けられた第1の配線溝と(配線溝202)、配線溝202に埋め込まれた第1の金属膜(Cuめっき膜206)と、を備え、配線溝202の底部が、凸部形状を有する。

(もっと読む)

半導体装置

【課題】電極パッドからの水分の拡散を防止できると共に、絶縁膜の薄膜化及び低誘電率化に対応できるようにする。

【解決手段】半導体装置は、半導体基板11の上方に形成され、外部との電気的な接続を取る接続部25である電極パッドと、半導体基板と接続部との間に積層された絶縁膜14等にそれぞれ形成され、上層の配線34が接続部と接続された複数の第1配線層及び該第1配線層同士を接続するビア31よりなる積層構造体27と、複数の絶縁膜に積層構造体の周囲を隙間なく囲むように形成され、複数の第2配線層40等及び該第2配線層同士を線状に接続するラインビア41よりなるリング構造体28と、接続部と内部回路とを電気的に接続する引き出し配線32Aとを有している。積層構造体とリング構造体とは複数の第1配線層の少なくとも1つによって互いに接続されており、引き出し配線はリング構造体と接続されている。

(もっと読む)

半導体装置

【課題】半導体装置において、パッド下方の絶縁膜におけるクラックの発生を抑制する。

【解決手段】半導体装置10は、基板4上に形成された絶縁膜3と、絶縁膜3中に形成された複数の配線20を含む配線層と、絶縁膜3上に形成されたパッド1とを備える。パッド1下方の少なくとも一部を含む領域において、該領域外に比べて隣り合う複数の配線20同士の間隔が狭くなった狭配線間隔領域が構成されている。

(もっと読む)

半導体装置の製造方法

【課題】マイクロローディング効果を抑えつつ開口幅の異なる溝を同時に形成することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、被加工部材1上の第1のマスク膜2上に、第1のアスペクト比を有する溝4aを含む小開口パターン領域5aと第1のアスペクト比よりも小さい第2のアスペクト比を有する溝4bを含む大開口パターン領域5bを含むパターンを有する第2のマスク膜3を積層する工程と、第2のマスク膜3のパターンを第1のマスク膜2に転写する工程と、小開口パターン領域5aの第2のマスク膜3を選択的に除去する工程と、小開口パターン領域5aの第2のマスク膜3を選択的に除去した後、第1のマスク膜2および第2のマスク膜3をマスクとして用いて被加工部材1にエッチングを施し、溝を形成する工程と、を含む。

(もっと読む)

半導体装置のパターン構造物及び半導体装置のパターン構造物の形成方法

【課題】半導体装置のパターン構造物及び半導体装置のパターン構造物の形成方法を提供すること。

【解決手段】半導体装置のパターン構造物は、延長ラインと延長ラインの端部に連結されるパッドとを具備する。パッドは、延長ラインの幅より広い幅を有することができる。パッドは、パッドの側部から延長する突出部を含むことができる。パターン構造物は、単純化された工程を通じて製造されることができ、微細パターンとパッドを含む多様な半導体装置に適用することができる。

(もっと読む)

配線パターン形成方法および半導体装置の製造方法、半導体装置、データ処理システム

【課題】2回のリソグラフィ工程によるSADP法(Self Align Double Patterning)を用いて、第1配線パターン形成領域には解像限界未満のパターンを含む第1配線パターンを形成し、第2配線パターン形成領域には解像限界以上の通常パターンからなる第2配線パターンを簡便に形成する方法を提供する。

【解決手段】解像限界未満の寸法を有する複数の配線を含む第1配線パターンを、第1リソグラフィ工程と第1リソグラフィ工程の後に実施される第2リソグラフィ工程を用いて形成し、第1のリソグラフィ工程で形成されたパターンに対してのみサイドウォールの形成および除去処理を行い、その後、解像限界以上のパターンを生成する第2リソグラフィ工程を実施する。第2のリソグラフィ工程で形成される解像限界以上の通常パターンに対しては、単純なリソグラフィ工程とすることが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】貫通電極を有し縦方向に積層される半導体装置であって、設計の自由度を拡大することができる半導体装置およびその製造方法を提供することを目的とする。

【解決手段】半導体基板1と、相互に離間して第1の主表面10から半導体基板1の深さ方向に向かって設けられた電極30aおよび電極30bと、電極30aおよび電極30b同士の間を結び半導体基板1を貫通することなく第1の主表面10から半導体基板1の深さ方向に向かって設けられた配線部40aとを備えている。電極30aは、半導体基板1を貫通して第2の主表面20に達する貫通電極となっている。貫通電極を有し縦方向に積層される半導体装置において、配線部40aを備えていることにより設計の自由度を拡大することができる。

(もっと読む)

半導体装置の製造方法

【課題】

太幅配線の添加元素を細幅配線の添加元素とは独立に制御する。

【解決手段】

層間絶縁膜に、第1の幅を有する第1の配線溝および第1の幅より広い第2の幅を有する第2の配線溝を形成し、第1の配線溝および第2の配線溝内に、第1の添加元素を含む第1のシード層を形成し、第1のシード層上に第1の銅層を形成し、第1の配線溝内の第1の銅層および第1のシード層を残存させつつ、第2の配線溝内の第1の銅層および第1のシード層を除去し、その後、第2の配線溝内に、第2の添加元素を含む又は添加元素を含まない第2のシード層を形成し、第2のシード層の上に第2の銅層を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線に断線が発生することを抑制し、かつエレクトロマイグレーションに対する耐性、及び熱ストレスに起因したボイドの発生に対する耐性を配線に持たせる。

【解決手段】第2導電パターン104は端が第1導電パターン100につながっており、第1導電パターン100より幅が細い。第1導電パターン100及び第2導電パターン104は、シード層110及びメッキ層120を有する。シード層110及びメッキ層120は、それぞれ銅により形成されている。メッキ層120は、底層に、表層より結晶粒が小さい小粒層122を有している。そして第2導電パターン104を形成するメッキ層120は、小粒層122を、第1導電パターン100を形成するメッキ層120より厚く有している。

(もっと読む)

パターン描画方法、配線パターン描画方法及び薄膜トランジスタ基板の製造方法

【課題】液滴吐出ヘッドと基材とを相対的に移動させることによって、同一の基材上に互いに方向と幅の異なる複数の線が混在するパターンを、同一方向の線毎に、それぞれ基材に対して液滴吐出ヘッドを同一方向に相対的に移動させながら液滴を吐出することによって描画するに際し、より高速な描画を行うこと。

【解決手段】基材上に方向と幅の異なる複数の線が混在するパターンを、それぞれ基材に対して液滴吐出ヘッドを同一方向に相対的に移動させながら液滴を吐出することによって、同一方向に沿う線毎に描画する方法であって、複数の線のうち、幅の最も狭い線とは方向が異なり且つ幅が広い線を、該幅の最も狭い線を描画する際に吐出する液滴のドット径よりも大きなドット径の液滴を吐出することによって描画する。

(もっと読む)

半導体装置及びその製造方法

【課題】容易なプロセスで導電層のコンタクト構造を形成できる半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、基体10のメモリセル領域5上に交互に積層された導電層WL1〜WL8と絶縁層17a〜17hとを有する積層体と、基体10のコンタクト領域6上に上記積層体の厚さと同等以上の高さで設けられ、各導電層WL1〜WL8の一層分の厚さよりも広い間隔を隔てて対向する壁部31〜35と、各壁部31〜35間に介在して設けられ各壁部31〜35間の開放端を通じてメモリセル領域5の積層体の各導電層WL1〜WL8と接続されたコンタクト層41〜44と、各コンタクト層41〜44上に設けられ各コンタクト層41〜44と接続されたコンタクト電極61〜64とを有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】配線抵抗の増加を抑えつつ、配線のエレクトロマイグレーション寿命、およびストレスマイグレーション寿命を向上させる。

【解決手段】半導体装置100は、基板102上に形成された層間絶縁膜104に形成された凹部に、高融点金属を含むバリアメタル膜106と、配線金属膜114を構成する銅および銅とは異なる不純物金属を含むシード合金膜ならびに銅を主成分として含むめっき金属膜とを形成し、シード合金膜およびめっき金属膜を、200℃以上、10分以下で熱処理する第1の熱処理工程と、第1の熱処理工程の後、凹部外部に露出しためっき金属膜、シード合金膜、およびバリアメタル膜106を除去する工程と、シード合金膜およびめっき金属膜を熱処理する第2の熱処理工程と、を含む。

(もっと読む)

多層配線、多層配線のダミー配線配置方法、半導体装置およびその製造方法

【課題】層間絶縁膜のグローバル段差をより低減する。

【解決手段】メタル配線11、21、31と層間絶縁膜12、22、32とが積層され、各層の層間絶縁膜を形成する毎に研磨して平坦化される多層配線60を積層方向からみて複数の領域52に分割し、領域毎に、各領域の面積に対する各領域内のメタル配線の占有面積の割合を、メタル配線についてそれぞれ求め、求めた割合を、領域毎に、メタル配線について積算した積算割合をそれぞれ求め、複数の領域の積算割合を用いて、予め求めておいた積算割合の相対値と層間絶縁膜32の上面の相対位置との関係より、複数の領域間の層間絶縁膜32の上面の相対位置関係を求め、層間絶縁膜32の上面が所定の値より低い位置にある領域511では、ダミー配線13,23,33を設け、層間絶縁膜32の上面が所定の値以上の位置にある領域513ではメタル配線にダミー配線を設けない。

(もっと読む)

半導体集積回路

【課題】配線の幅とピッチが変化する部分の欠陥に対するマージンを十分に確保することが可能な半導体集積回路を提供する。

【解決手段】第1、第2の配線11,12は、配線の幅と配線間のスペースの幅が等しい。第3の配線13は、第1の配線11の一端に接続され、幅が第1の配線11の幅とスペースの幅に等しく、第2の配線12の側部に接続されている。第2の配線12は一部にギャップGを有している。

(もっと読む)

低損失多層オンチップインダクタ

【課題】多層構造のオンチップインダクタ素子において、インダクタの表皮効果を低減してQ値を向上させる。

【解決手段】単一のインダクタ配線1から構成される、又は複数のインダクタ配線1を上下に積層して並列接続したものから構成されるインダクタ配線層を3層以上有し、各インダクタ配線層は上下に積層されて直列接続されており、最上層と最下層のインダクタ配線層を除く中間層の各インダクタ配線層の実効的な膜厚が、該最上層及び最下層のインダクタ配線層の実効的な膜厚よりも大きいことを特徴とする、半導体基板上絶縁膜中のオンチップインダクタである。

(もっと読む)

21 - 40 / 161

[ Back to top ]