Fターム[5F033NN16]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクト部の配線構造の特徴 (690) | 接触構造 (642) | 下層配線、上層配線を貫通 (75)

Fターム[5F033NN16]に分類される特許

21 - 40 / 75

集積回路装置及びその製造方法

【課題】チップ面積が小さく、製造コストが低い集積回路装置及びその製造方法を提供する。

【解決手段】集積回路装置の製造方法において、複数の第1絶縁層及び複数の第2絶縁層を1層ずつ交互に積層させて積層体を形成すると共に、少なくとも2層の前記第2絶縁層内に少なくとも2本の配線を形成する工程と、前記積層体における前記積層体の積層方向から見て前記配線から離隔した位置に、前記積層方向に延びるコンタクトホールを形成する工程と、前記第2絶縁層における前記コンタクトホールと前記配線との間の部分を除去する工程と、前記第2絶縁層が除去された部分及び前記コンタクトホールの内部に導電材料を埋め込む工程と、を実施する。

(もっと読む)

半導体装置およびその製造方法

【課題】グラフェンのバリスティック伝導性を利用した低抵抗配線を備え、配線と配線接続部材の接続部分の構成の複雑化を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、基板と、基板の上方に設けられ、積層された複数のグラフェンナノリボンシート122からなるグラフェンナノリボン層121を含む下層配線12と、複数のグラフェンナノリボンシート122の少なくとも1枚を貫通し、下層配線12と上層配線13とを接続するビア14およびバリアメタル15と、を有する。

(もっと読む)

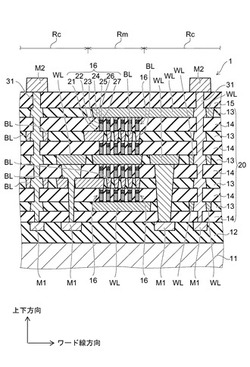

半導体記憶装置

【課題】層間接続により生ずるチップ面積の増大を抑制し、コスト削減を実現する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、前記半導体基板上に前記半導体基板と垂直方向にそれぞれ複数層形成された互いに交差する複数の第1及び第2の配線、並びにこれら第1及び第2の配線の各交差部に接続された複数のメモリセルを有するセルアレイブロックと、前記セルアレイブロックの第n層目(nは自然数)の第1の配線と前記第n層目の第1の配線以外の第1の配線、前記半導体基板、又は他の金属配線とを接続する前記セルアレイブロックの積層方向に延びる第1のビア配線とを備える。前記第1のビア配線は、前記セルアレイブロックの積層方向と直交する断面が楕円形状であり、この断面の長径方向が前記第1の配線方向に対し垂直であることを特徴とする。

(もっと読む)

キャパシタ・モジュール・アレイを含む半導体構造とその製造方法および動作方法

【課題】漏れ電流の大きいキャパシタを電気的に切断することができるキャパシタ・モジュールを含む半導体構造、これを製造する方法、およびこれを動作させる方法を提供する。

【解決手段】モジュール化したキャパシタ・アレイは複数のキャパシタ・モジュールを含む。各キャパシタ・モジュールは、キャパシタと、このキャパシタを電気的に切断するように構成されたスイッチング・デバイスと、を含む。スイッチング・デバイスは、キャパシタの漏れのレベルを検出するように構成された検知ユニットを含み、漏れ電流が所定のレベルを超えるとスイッチング・デバイスがキャパシタを電気的に切断するようになっている。各キャパシタ・モジュールは、単一のキャパシタ・プレート、2つのキャパシタ・プレート、または3つ以上のキャパシタ・プレートを含むことができる。漏れセンサおよびスイッチング・デバイスを用いて、漏れを生じたキャパシタ・アレイのキャパシタ・モジュールを電気的に切断し、これによってキャパシタ・アレイを過剰な電気的漏洩から保護する。

(もっと読む)

3次元半導体メモリ装置及びその製造方法

【課題】3次元半導体メモリ装置及びその製造方法を提供する。

【解決手段】本装置は、積層された導電パターン、導電パターンを貫通する活性パターン及び導電パターンと活性パターンとの間に介在される情報貯蔵膜を含む少なくとも1つのメモリ構造体を含み、活性パターンは積層された下部及び上部貫通ホールを各々満たす下部及び上部半導体パターンを含むことができる。1つのメモリ構造体を構成する情報貯蔵膜は同一の工程段階を利用して実質的に同時に形成され、1つのメモリ構造体を構成する下部及び上部貫通ホールは互いに異なる工程段階を利用して順に形成され得る。

(もっと読む)

半導体集積回路装置

【課題】多層配線の下地半導体基板への配線引き出し部のコンタクト抵抗均一化を図った半導体集積回路装置の提供。

【解決手段】半導体集積回路装置は、半導体基板と、前記半導体基板上に複数層積層形成された配線と、前記配線の引き出し領域に前記配線の延長部として形成されて、所定幅のスペースを介して対向するメタル片対により構成されるフックアップ部73と、前記フックアップ部のメタル片対のスペースを貫通するように埋め込まれたコンタクト導体72とを有し、前記配線の少なくとも2層の間で前記フックアップ部のメタル片対のスペース幅を異ならせた。

(もっと読む)

半導体装置、半導体装置の製造方法、および電子機器

【課題】IGZO層とITO層とを電気的に接続する場合には、易加工性を備え電気抵抗率が低いアルミ等の金属と高融点金属としてのチタン等との積層構造を用いる必要があるが、積層構造を形成する場合、複数の金属層を形成する必要がある。そのため製造工程が増えると共に、パーティクル等の発生確率が増え、歩留まりを落とすという課題がある。

【解決手段】ITO等の金属酸化物を用いた画素電極2aが、層間絶縁層9に形成されたコンタクトホール9aを介してIGZO層を用いた配線層7aと電気的に接続している。画素電極2aとAl−Nd合金を用いた上電極6cと直接接触させた場合、コンタクト抵抗が高くなるが、配線層7aにIGZO層を用い、画素電極2aにITO等の第2金属酸化物配線層を用いた場合、互いの構造が類似していることから、密接させるだけで接触抵抗の増大を招くことなく電気的に導通を取ることが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とのコンタクトを簡便に得ることが可能な半導体装置及びその製造方法を提供すること。

【解決手段】本発明にかかる半導体装置は、縦型MOSFET50を有する半導体装置であって、半導体基板に形成され、ゲート絶縁膜3を介して縦型MOSFET50のゲート電極4aが埋め込まれている第1トレンチ(トレンチ2a)と、第1トレンチとつながって形成され、第1トレンチよりトレンチ幅の広い第2トレンチ(トレンチ2b)と、ゲート電極4aとつながって形成され、ゲート絶縁膜3を介して第2トレンチの側面に形成されたゲートパッド(ゲート電極4b)と、ゲートパッドの側面と接続するように形成され、ゲートパッドを介してゲート電極4aと電気的に接続するゲート配線11と、を備えるものである。

(もっと読む)

半導体装置とその製造方法、電気光学装置とその製造方法、回路基板とその製造方法、及び電子機器

【課題】フォトリソグラフィー法及びエッチング法を用いることなく導電層間を接続することができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、基板上に第1導電層と層間絶縁膜と第2導電層とを順に積層形成する導電層工程と、前記第2導電層の表面から物理的加工を施すことで、前記第2導電層と前記層間絶縁膜とを貫通して前記第1導電層に達する凹部を形成するコンタクトホール形成工程と、を有することを特徴とする。

(もっと読む)

三次元積層型半導体集積回路及びその製造方法

【課題】スルーシリコンビアの高密度化、製造歩留りの向上及び製造コストの低減を同時に実現する。

【解決手段】本発明の例に係る三次元積層型半導体集積回路は、同一方向を向いて互いに積み重ねられる第一及び第二チップC1,C2と、第一チップC1を構成する第一半導体基板21及び第二チップC2を構成する第二半導体基板21を貫通し、かつ、第一チップC1内に設けられる半導体素子に繋がる第一電極14を貫通するスルーシリコンビア13とを備える。第一及び第二チップC1,C2は、面で結合する。

(もっと読む)

半導体装置及びその製造方法

【課題】チップ面積の増大を防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】拡散領域101aを表面に有する半導体基板100と、半導体基板100を覆う層間絶縁膜107と、層間絶縁膜107上に形成され、拡散領域109aを表面に有する半導体層108と、層間絶縁膜107および半導体層108を貫通する貫通口119a内に形成され、拡散領域101aに接し、且つ側面の一部が拡散領域109aに接するソース線プラグ116aと、ソース線プラグ116aと層間絶縁膜107との間に介在し、且つソース線プラグ116aが拡散領域109aと接する部分を除いてソース線プラグ116aと半導体層108との間に介在する側壁絶縁膜117aと、を具備する。

(もっと読む)

半導体装置

【課題】コンタクトホールの加工時において配線のダメージを受けにくく、信頼性の低下を抑制できる構造の接続部を有する半導体装置を提供すること。

【解決手段】接続部1は、第1導電層2と第2導電層4とが、その交差個所に設けられたコンタクトホール5を介して接続されたものである。矩形状のコンタクトホール5は第2導電層4の幅方向の略中央に配置されている。そして、コンタクトホール5のパターンを囲むように矩形状の半導体層3が設けられている。半導体層3は、コンタクトホール5の底部において第1導電層2上に形成されている。この半導体層3は、第1導電層2とのエッチング選択比が高く、第1導電層2に対するエッチング効率が充分に高いものである。

(もっと読む)

半導体装置及びその製造方法

【課題】導電層とコンタクト電極との接触抵抗が導電層の形成された深さによってばらつくのを抑制する半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、複数の導電層WL1〜WL4と複数の絶縁層17とが交互に積層された積層体であって、複数の導電層WL1〜WL4が階段状に加工された階段構造部を有する積層体と、その階段構造部を覆って設けられた層間絶縁層42と、層間絶縁層42を貫通すると共にそれぞれが対応する階段状の各導電層WL1〜WL4を一層分貫通して形成された複数のコンタクトホール50の内部に設けられ、コンタクトホール50内に露出する導電層WL1〜WL4の側壁部に接するコンタクト電極63とを備えている。

(もっと読む)

半導体装置

【課題】タングステン埋め込み配線に接続される信頼性の高いタングステンコンタクトを有する半導体装置を提供する。

【解決手段】半導体基板の主面上の第1層11に配設されるとともに、貫通孔を有し、タングステンを主成分とする第1配線12と、一端部13aが貫通孔を通って第1配線12の底面に至るとともに、バリアメタル14を介して貫通孔の側面12bに接触し、他端部13bが層間絶縁膜15を挟んで第1層11の上方の第2層16に配設された第2配線17に接続されたタングステンを主成分とする接続導体13と、を具備する。

(もっと読む)

積層半導体装置及び積層半導体装置の製造方法

【課題】動作の安定した積層半導体装置を提供する。

【解決手段】単結晶シリコンのベース部と、ベース部の上の絶縁層と、絶縁層の上の単結晶シリコン層と、単結晶シリコン層に形成され絶縁層に達する分離溝構造と、分離溝構造で囲まれた単結晶シリコン層のボディ領域と、ボディ領域に形成されるトランジスタと、少なくともベース部および絶縁層を貫通し、ボディ領域に電気的に結合する貫通結合部とを有する第1半導体装置と、貫通結合部に接する外部接続部を有する第2半導体装置と、を備え、第2半導体装置は、貫通結合部を介して第1半導体装置のボディ領域の電位を制御する。

(もっと読む)

半導体装置

【課題】コンタクトの位置ずれが回路の特性に与える影響を低減した半導体装置を提供する。

【解決手段】この半導体装置は、半導体層10に設けられた素子分離膜20と、素子分離膜20により区画された素子形成領域と、素子形成領域上及び素子分離膜20上を延伸しているゲート配線140と、ゲート配線140の側壁に形成されたサイドウォール150と、素子分離膜20上に位置するゲート配線140に接続するコンタクト200とを備える。ゲート配線140の側壁は、少なくとも上部においてコンタクト200に接触してる領域144を有する。

(もっと読む)

半導体装置

【課題】コンタクト抵抗が低い半導体装置を提供する。

【解決手段】半導体装置は、第1導電型の半導体基板と、埋め込み酸化膜と、第2導電型の半導体層と、を備えるSOI基板に作られ、前記埋め込み酸化膜は、自己に穿設された、前記半導体基板と前記半導体層とを連通する、第1の開口を有し、前記半導体基板は、その表面部分に埋め込み状態に形成され、前記第1の開口内の前記半導体層の埋設部と互いに電気的に接続している、第2導電型の接続層を有し、前記半導体層及び前記埋め込み酸化膜を貫通して、前記接続層の表面部分に至る第2の開口内に埋め込まれて、側面において前記半導体層と電気的に接続し、底面において前記接続層と電気的に接続する、コンタクト電極と、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極のショート不良を引き起こすことなく、貫通電極とパッド電極との密着性を向上させる。

【解決手段】開口部22が設けられたパッド電極21b上にエッチストッパ膜23を積層し、半導体基板11に形成された貫通孔41に貫通電極45を埋め込む際に、貫通電極45の先端が、開口部22を介してパッド電極21bの一部を突き抜け、エッチストッパ膜23で止められるように構成する。

(もっと読む)

半導体装置の製造方法

【課題】Alを含む金属配線の形成において、サイドエッチ量を低減した微細な金属配線を形成でき、金属配線上に形成するビアホールが金属膜を突き抜けるのを抑制することができる半導体装置の製造方法を提供する。

【解決手段】基板上に第一TiN膜3、Alを含む金属膜4、第二TiN膜5を順次積層した金属配線層6を形成する工程と、前記金属配線層6の上にストッパー膜7、シリコン酸化膜8を順次積層したハードマスク層12を形成する工程と、前記ハードマスク層12を選択的にエッチングして前記金属配線層6の上にハードマスク12aを形成する工程と、前記ハードマスク12aをマスクとしてエッチングし金属配線6aを形成する工程と、前記ハードマスク12aおよび前記金属配線6aの上に層間絶縁膜14を形成する工程と、前記ストッパー膜7をエッチングストッパとして前記層間絶縁膜14にビアホール17aを形成する工程とを含む。

(もっと読む)

TFTアレイ基板の製造方法

【課題】簡単な工程で画素電極とコンタクトホールとを形成するTFTアレイ基板の製造方法を提供する。

【解決手段】絶縁膜を成膜する工程と、絶縁膜の上に導電膜を成膜する工程と、導電膜をパターニングして開口が設けられた画素電極を形成する工程と、開口が設けられた画素電極をエッチングマスクとしてエッチング法により絶縁膜に開口と連通するコンタクトホールを形成する工程と、を有することを特徴とするTFTアレイ基板の製造方法。

(もっと読む)

21 - 40 / 75

[ Back to top ]