Fターム[5F033NN16]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクト部の配線構造の特徴 (690) | 接触構造 (642) | 下層配線、上層配線を貫通 (75)

Fターム[5F033NN16]に分類される特許

41 - 60 / 75

半導体装置及びその製造方法

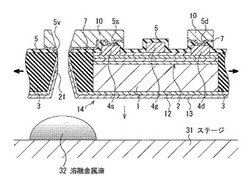

【課題】細く深いバイアホールが設けられる場合でも、ソースインダクタンスを十分に低減し、高い放熱効率を得ることができる半導体装置及びその製造方法を提供する。

【解決手段】SiC基板1上に化合物半導体領域2を形成し、その後、化合物半導体領域2上にゲート電極4g、ソース電極4s及びドレイン電極4dを形成し、更に、化合物半導体領域2上にソース電極4sに接続されるAu膜10を形成する。次に、SiC基板1の裏面にレーザビームを照射して、SiC基板1、化合物半導体領域2及びAu層を貫通するバイアホール21を形成する。次に、バイアホール21の側面及びSiC基板1の裏面にわたってビア配線14を形成する。次に、バイアホール21内に溶融金属滴32を充填し凝固させることにより、導通ビアを形成する。そして、溶融金属滴32を充填する際に、SiC基板1を溶融金属滴32に対して相対的に振動させる。

(もっと読む)

配線構造、半導体装置及び半導体装置の製造方法

【課題】 高周波信号の伝達も含めた配線抵抗を低減することができると共に、良好な遮蔽導体として機能する配線構造及びその配線構造を有する半導体装置を提供する。

【解決手段】 複数の配線層にそれぞれ設けられた配線1,3が互いに重複し、互いに電気的に複数層に亘り並列接続された配線構造であって、複数の配線層の少なくとも下層の一つの配線層が、少なくとも2本以上の並列配線に分離されて延伸しているスリット配線部を有し、上層の配線3からスリット配線部の並列配線の間隙に浸入して両側の並列配線と接続しているスリット接続部2aを有する配線構造とする。

(もっと読む)

半導体基板接続ビア

第1導電層(104)とシリケートガラス層(106)の縁部を互いに隣接させて、半導体基板(41)まで延在するビア(164)に沿って延在させる。導電体(114/116)は、ビア(164)を通り延在して、半導体基板(41)と接触する。 (もっと読む)

半導体装置

【課題】静電保護素子のクランプ能力を十分に発揮し、内部回路を静電気によるサージから保護することができる半導体装置を提供することを目的とする。

【解決手段】半導体基板上に、内部回路と、前記内部回路と接続配線及び接地配線により接続される接続パッド及び接地パッドと、前記接続パッドと前記接地パッドとの間に接続される静電保護素子とが設けられ、前記半導体基板と前記接地配線とが、前記接地配線に所定の密度で形成されたコンタクトにより電気的に接続されている半導体装置であって、前記所定の密度は、前記接続パッドから前記静電保護素子を経由して前記接地パッドに至る部分のインピーダンスが、前記接続パッドから前記内部回路を経由して前記接地パッドに至る部分のインピーダンスよりも低くなるように設定されていることを特徴とする。

(もっと読む)

半導体装置、電気光学装置、及び電子機器

【課題】構造を複雑化させることなく安定した特性が得られ、さらには抵抗素子を含む回路の高集積化を実現できる半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、基板本体(基板)10Aと、基板本体10A上に形成された半導体素子(インバータINV1,INV2)と、半導体素子に接続された配線121,122と、配線121,122に形成された抵抗素子R1,R2とを備えており、配線121,122が、積層された複数の導電層131,132を有しており、異なる抵抗値を有する複数の抵抗素子R1,R2が、複数の導電層のうち少なくとも一部の導電層を用いて配線121,122に形成されていることを特徴とする。

(もっと読む)

半導体パッケージ用貫通電極及びこれを有する半導体パッケージ

【課題】 積層半導体パッケージに適した半導体パッケージ用貫通電極、及び前記貫通電極を有する半導体パッケージを提供する。

【解決手段】 半導体パッケージ用貫通電極は、半導体チップを貫通して、内部にリセス部が形成された第1の電極、及び前記リセス部内に配置された第2の電極を含む。半導体パッケージは、回路部を有する半導体チップ本体及び前記回路部と連結されたボンディングパッドを有する半導体チップ、並びに、前記ボンディングパッド及び前記ボンディングパッドと対応する前記半導体チップ本体を貫通し、内部にリセス部を有する第1の電極、及び前記リセス部の内部に配置された第2の電極を有する貫通電極を含む。

(もっと読む)

半導体装置の製造方法

【課題】製造コストの増大を抑えながら、コンタクト抵抗のばらつきを低減できる半導体装置の製造方法を提供する。

【解決手段】第1の絶縁膜上に第1の導電層を形成する工程と、第1の導電層を覆うように第2の絶縁膜を形成する工程と、第2の絶縁膜上にレジストマスクを形成する工程と、前記レジストマスクを用いた第1のドライエッチングにより、第2の絶縁膜に、第1の導電層に達するホールを形成する工程と、前記レジストマスクを除去する工程と、前記ホールの底に露出した第1の導電層を第2のドライエッチングにより除去して、このホールが第1の絶縁膜に達し且つこのホール内の側面に第1の導電層を露出させる工程と、前記ホール内に導電材を埋め込んで、このホール内の側面に露出した第1の導電層と接触する導電プラグを形成する工程と、第2の絶縁膜上に、前記導電プラグに接続する第2の導電層を形成する工程を有する半導体装置の製造方法。

(もっと読む)

半導体装置及びその形成方法

【課題】効果的に切断できるヒューズ構造物を有する半導体装置及びその形成方法を提供する。

【解決手段】半導体装置は、基板110上に位置するヒューズ構造物120を含む。層間絶縁膜130は、ヒューズ構造物120を覆う。第1コンタクトプラグ151、第2コンタクトプラグ152及び第3コンタクトプラグ153が層間絶縁膜130を貫通して、ヒューズ構造物120に連結される。第1コンタクトプラグ151及び第2コンタクトプラグ152とそれぞれ電気的に連結される第1導電パターン161及び第2導電パターン162が層間絶縁膜上130に配置される。

(もっと読む)

半導体パッケージ、その製造方法、半導体パッケージを利用したパッケージモジュール及び電子製品

【課題】貫通電極と導電性パッドとを電気的に連結すると同時に、貫通電極と半導体基板とを絶縁させることによって信頼性を高めた半導体パッケージを提供する。

【解決手段】第1面1051及び第2面1052を持つ半導体基板105と、半導体基板105の第1面上1051の層間絶縁層115と、層間絶縁層115の一部分上の導電性パッド120と、第2面1052から半導体基板105を貫通して伸張する第1部分、及び第1部分から層間絶縁層115を貫通して導電性パッド120と電気的に連結された第2部分を備える貫通電極155と、半導体基板105から貫通電極155の第1部分を分離するスペーサ絶縁層145と、を備える。

(もっと読む)

半導体装置及び当該半導体装置の作製方法

【課題】集積回路部上にアンテナを作り込んで設ける場合であっても、接続不良やコンタクト抵抗の増加を抑制することを課題とする。

【解決手段】基板上に第1の導電膜を有する集積回路部を形成し、集積回路部上に絶縁膜を形成し、絶縁膜上にアンテナとして機能する第2の導電膜を選択的に形成し、絶縁膜及び第2の導電膜に開口部を形成して第1の導電膜を露出させ、メッキ処理により開口部及び第2の導電膜の上面に第3の導電膜を形成することにより、第1の導電膜及び第2の導電膜とを電気的に接続する。

(もっと読む)

半導体装置及びその作製方法

【課題】ソース電極又はドレイン電極の膜厚のばらつき又は断線を防止した半導体装置を容易に作製する方法を提案する。

【解決手段】絶縁基板上に形成された半導体層と、半導体層上に形成された第1の絶縁層と、第1の絶縁層上に形成されたゲート電極と、ゲート電極上に形成された第2の絶縁層と、を有し、少なくとも第1の絶縁層、及び第2の絶縁層に形成された半導体層に達する開口部と、前記開口部において前記第2の絶縁層の側面に形成された段差と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置およびその製造方法は高誘電体をゲート絶縁膜として有し、かつ、適正な閾値電圧を有する。

【解決手段】半導体装置は、半導体基板101と、半導体基板上に設けられ、シリコン酸化膜よりも比誘電率の高い高誘電体から成るゲート絶縁膜108,109と、ゲート絶縁膜上に設けられたアルミニウム層を含むN型FET用の第1のゲート電極110aと、ゲート絶縁膜上に設けられ、NiXSiY(X>Y)から成るP型FET用の第2のゲート電極110bとを備えている。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、以下の工程を有している。層間絶縁膜1内に下部配線5を備えた第一層を準備する。第一層上にライナー膜11を設ける。層間絶縁膜12をライナー膜11上に設ける。層間絶縁膜12およびライナー膜11を貫通して下部配線5に達するトレンチ14を形成する。トレンチ14の側壁に沿った層間絶縁膜12上及びライナー膜11上と、下部配線5上に位置するトレンチ14の底部とにバリアメタル13を形成する。トレンチ14底部を物理エッチングすることにより、トレンチ14底部のバリアメタル13と下部配線5とを削り、円錐形状又は半球形状の孔6をトレンチ14の下側に設ける。トレンチ14の側壁上のバリアメタル13上及び孔6内に導電膜15を形成する。トレンチ14及び孔6内にCu膜19を埋め込む。

(もっと読む)

半導体装置およびその製造方法

【課題】多層配線構造の作製において、すべての多層配線用ビア・配線・電極および放熱用ビアなどを、相互の接続特性を良好に保って、カーボンナノチューブ(CNT)束により形成する半導体装置を提供する。

【解決手段】電導素材である、柱状構造をもったカーボンナノチューブ(CNT)束2の少なくとも一つの表面に、Au膜など金属膜を形成後、下地層を積層し、その上に触媒金属層を形成して、CVD法により柱状構造をもったカーボンナノチューブ(CNT)束7を成長することで、二つの柱状構造体カーボンナノチューブ(CNT)束を低抵抗で接続して形成する。この基本構成方法の組合せで、多層配線用の各種電導構成要素を作製する。また、成長条件によりCNTの成長先端部が平坦となることを用いて、Au膜など金属膜を利用せずに、成長方向に多段に、長いカーボンナノチューブ(CNT)束を作製でき、特に放熱用ビアなどへの適用が可能である。

(もっと読む)

半導体装置

【課題】外部から曲げ等の物理的な力が加わり応力が生じた場合であってもトランジスタ等の素子の損傷を抑制する半導体装置を提供することを目的とする。

【解決手段】基板上に設けられ、チャネル形成領域と不純物領域とを具備する半導体膜と、チャネル形成領域の上方にゲート絶縁膜を介して設けられた第1の導電膜と、第1の導電膜を覆って設けられた第1の層間絶縁膜と、第1の層間絶縁膜上に、少なくとも不純物領域の一部と重なるように設けられた第2の導電膜と、第2の導電膜上に設けられた第2の層間絶縁膜と、第2の層間絶縁膜上に、開口部を介して不純物領域と電気的に接続するように設けられた第3の導電膜とを設ける。

(もっと読む)

表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。

【解決手段】絶縁表面上に選択的に光吸収層を形成し、絶縁表面上及び光吸収層上に絶縁層を形成し、絶縁表面、光吸収層及び絶縁層にレーザ光を照射し、絶縁層のレーザ光照射領域において光吸収層上の絶縁層のみを選択的に除去し絶縁層に光吸収層に達する開口を形成し、開口に光吸収層と接するように導電膜を形成する。露出した光吸収層と接するように開口に導電膜を形成することによって、光吸収層及び導電膜は絶縁層を介して電気的に接続することができる。

(もっと読む)

レーザビーム照射装置及びレーザビーム照射方法

【課題】TFT及びそれを用いる電子回路並びにTFTによって形成される表示装置の製造工程において、フォトリソグラフィ工程を使用せず、さらに工程を簡略化し、生産能力を向上させる技術を提供する。

【解決手段】レーザビームを射出するレーザ発振器と、前記レーザビームを被照射体の表面において線状ビームに形成する光学系と、前記光学系と前記被照射体との間に設けられたマスクと、を有し、前記線状ビームは前記マスクを介して複数のレーザビームに分割され、前記複数のレーザビームは前記被照射体に照射される。

(もっと読む)

半導体装置およびその製造方法

【課題】バリア膜の構造を工夫することで、銅配線と絶縁膜との密着性を向上させることを可能とする。

【解決手段】基板11上の第1絶縁膜12に形成された第1配線17を被覆する第2絶縁膜21と、前記第2絶縁膜21に形成された配線溝25と、前記配線溝25の底部の前記第2絶縁膜21に形成されたもので前記第1配線17に通じる接続孔26と、前記接続孔26底部を除く前記配線溝25と接続孔26との内面に形成された第1バリア膜31と、前記接続孔26底部の前記第1絶縁膜12上に形成された第2バリア膜34と、前記第1バリア膜31および第2バリア膜を34介して前記配線溝25および前記接続孔26に埋め込まれた第2配線35(含むプラグ36)とを備えたことを特徴とする。

(もっと読む)

表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。また、それらの表示装置を構成する配線等のパターンを、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】マスク層を形成する際、形成したいパターンの外側(パターンの輪郭、端部に相当する)に液状のマスク層形成材料を含む組成物を付着させ、枠状の第1のマスク層を形成する。枠状の第1のマスク層の内側の空間を充填するように、液状の第2のマスク層形成材料を含む組成物を付着させ第2のマスク層を形成する。第1のマスク層及び第2のマスク層は接して形成され、第2のマスク層の周囲を囲むように第1のマスク層が形成されるので、第1のマスク層及び第2のマスク層は連続した一つのマスク層として用いることができる。

(もっと読む)

デュアル配線型集積回路チップ

【課題】 デュアル配線型集積回路チップ及びその製造方法を提供する。

【解決手段】 両面に配線レベルを有する半導体デバイス、及び、両面のデバイス及び配線レベルへのコンタクトを有する半導体構造体を製造する方法を提供する。本方法は、シリコン・オン・インシュレータ基板上のデバイスへの第1コンタクトと、第1コンタクトへの第1側面上の配線レベルとを有するデバイスを製造するステップと、下部シリコン層を除去して埋込み酸化物層を露出させるステップと、埋込み酸化物層を貫通してデバイスへの第2コンタクトを形成するステップと、埋込み酸化物層の上に第2コンタクトへの配線レベルを形成するステップとを含む。

(もっと読む)

41 - 60 / 75

[ Back to top ]