Fターム[5F033NN20]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | 下部引き出し電極の利用 (42)

Fターム[5F033NN20]に分類される特許

1 - 20 / 42

半導体装置

【課題】2つの入力端子の配置形態を工夫することにより配線層の増設スペースを確保しスタンダードセルの原価低減を図る。

【解決手段】入力端子34bはゲート配線2bに接続され、入力端子34cはゲート配線2cに接続される。また、入力端子34b、34cは、Y方向に互いに近接して配置され、入力端子34bの第2コンタクト配線4bは、第1コンタクト配線3bと隣接し、且つ該第1コンタクト配線3bに対しX方向に延在する。入力端子34cの第2コンタクト配線4cは、第1コンタクト配線3cと隣接し、且つ該第1コンタクト配線3c対して第2コンタクト配線4bとは逆のX方向に延在する。即ち、入力端子34bの第1コンタクト配線3bと入力端子34cの第2コンタクト配線4cとはY方向に互いに対向して配置され、入力端子34bの第2コンタクト配線4bと入力端子34cの第1コンタクト配線3cはY方向に互いに対向して配置される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】縦型トランジスタの特性を悪化させることなく縦型トランジスタの設置面積を削減できる高集積化に適した半導体装置およびその製造方法を提供する。

【解決手段】一定の間隔を空けて配置された複数のピラー30が備えられ、複数のピラー30が、縦型トランジスタTのチャネルとして機能する半導体層からなるチャネルピラー1と、不純物拡散層からなり、前記チャネルピラー1の下部に接続されて縦型トランジスタTの一方のソースドレインとして機能する下部拡散層4に電気的に接続された引き上げコンタクトプラグ2とを含む半導体装置とする。

(もっと読む)

半導体装置およびその製造方法

【課題】3Dピラートランジスタにおいて、ゲートコンタクトとシリコン基板との間のショートを抑制した半導体装置及びその製造方法を得るという課題があった。

【解決手段】半導体からなる基板1と、一面1aから突出され、前記半導体からなる第1の突出部2と、一面1aに設けられた溝部1cに充填された第1の絶縁体3と、第1の突出部2に隣接して一面3aから突出され、第1の絶縁体3からなる第2の突出部4と、第1の突出部2の側面を覆うゲート絶縁膜5と、ゲート絶縁膜5を覆うゲート電極6と、第1の突出部2に設けられた上部拡散層13と、下部拡散層14と、第2の突出部4の側面を覆うとともにゲート電極6に接続された連結電極60と、第1の突出部2及び第2の突出部4を覆う層間絶縁膜と、前記層間絶縁膜を貫通して連結電極60に接するゲートコンタクト10と、を有する半導体装置及びその製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置及びその製造方法

【課題】階段状に加工された複数の導電層と、各導電層に達し深さの異なる複数のコンタクトホールとの接続構造の信頼性を高めた半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、基板10の第2のコンタクト領域5上に設けられ、第2のコンタクト領域5と第1のコンタクト領域4との間に段差を形成する下地層45bと、下地層45bを覆って基板10上に設けられ、下地層45b上に積層された上段部81が階段状に加工された下層側積層体91と、下層側積層体91における第1のコンタクト領域4上に積層された下段部82の上に設けられ、階段状に加工された上層側積層体92と、階段状に加工された部分を覆う層間絶縁層62と、層間絶縁層62を貫通し階段状に加工された部分の各々の導電層WLに達して形成されたコンタクトホール内に設けられたコンタクト電極51と、を備えた。

(もっと読む)

半導体装置の製造方法

【課題】 今後の素子の微細化に対応できる、貫通電極を備えた半導体装置の製造方法を提供すること。

【解決手段】 半導体装置の製造方法は、第1の主面および該第1の主面に対向する第2の主面を有する半導体基板10と、半導体基板10の第1の主面上に設けられた電極パッド26と、半導体基板10の前記第1の主面と前記第2の主面との間を貫通する貫通孔100内に設けられ、電極パッド26と接続する貫通電極23とを具備してなり、貫通孔100の前記第1の主面側には、電極パッド26と貫通電極23とが直接的に接続する第1の接続部と、電極パッド26と貫通電極23とが間接的に接続する第2の接続部とを含み、前記第1の主面上に電極パッド26を形成する工程と、半導体基板10を加工し、貫通孔100を形成する工程であって、貫通孔100内において電極パッド26の一部が露出する前記工程と、貫通孔100内に貫通電極23を形成する工程とを含む。

(もっと読む)

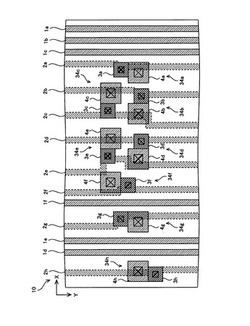

多層配線基板及びそれを備えた半導体装置

【課題】遮光領域を抑制することにより、開口率の低下を防止するとともに、製造工程を簡素化することができる多層配線基板及びそれを備えた半導体装置を提供することを目的とする。

【解決手段】TFT基板1は、第1コンタクトホール11が形成された第1絶縁膜8と、第1絶縁膜8の表面及び第1コンタクトホール11の表面に形成された第1配線層14と、第2コンタクトホール15が形成された第2絶縁膜9と、第2絶縁膜9上に積層されるとともに、第2絶縁膜9の表面及び第2コンタクトホール15の表面に形成され、第1配線層14と導通された第2配線層16とを備えている。そして、第1及び第2コンタクトホール11,15が、TFT基板1の上下方向Xにおいて重なった状態で直線的に配置され、第1コンタクトホール11において、第1配線層14上に絶縁性樹脂25が充填されている。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応可能であり、不純物拡散領域上に形成したコンタクトプラグが近傍の導電材料とショートすることを防止する配線構造を有する半導体装置を提供する。

【解決手段】半導体基板内の不純物拡散領域22上に選択エピタキシャル成長法により、第1の層16aを形成する工程と、第1の層16a上に、選択エピタキシャル成長法により第2の層18を形成する工程と、第2の層18上に導電材料を充填することにより、コンタクトプラグ21を形成する工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置内の埋め込みコンタクトホールを簡略な工程で形成するための半導体装置の製造方法を提供する。

【解決手段】シリコン基板101上に1又は複数の半導体素子が作り込まれてなる半導体装置に埋め込みコンタクトを形成するにあたり、半導体素子層の全面に層間絶縁膜109を形成する(第1工程)。次いで、半導体装置内のシリコン106、107、ポリシリコン104A、104B、又は金属シリサイド108A,108Bからなる2つの領域が露出するように層間絶縁膜にコンタクトホール109aを形成する(第2工程)。そして、コンタクトホールから露出しているシリコン106、107、ポリシリコン104A、104B、又は金属シリサイド108A,108Bの表面に無電解めっき法により選択的に金属膜111を形成する(第3工程)。

(もっと読む)

半導体装置とその製造方法

【課題】柱状半導体層が微細化されて高集積化されても、コンタクト抵抗の増加を抑制する構造の半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に設けられた、半導体柱状部(柱状半導体層3)と、の天面に接するように設けられた、柱状半導体層3と同径以下のコンタクト柱状部(コンタクト層7)と、この天面に設けられた凹部をと備えるものである。

(もっと読む)

半導体装置およびその製造方法

【課題】ビアホール下方でのスペーサ膜の閉塞を回避するとともに、ビアプラグの上方で隣接する配線層との間の余裕距離を確保することができる半導体装置を提供する。

【解決手段】シリコン基板1上に設けられた上面から下面まで貫通するコンタクトプラグ32を有する第1の層間絶縁膜30と、第1の層間絶縁膜30上に形成され、コンタクトプラグ32の形成位置に対応する位置の上面から下面まで貫通するビアホール41を有する第2の層間絶縁膜40と、ビアホール41内にコンタクトプラグ32と電気的に接触するように導電性材料が埋め込まれたビアプラグ43と、を備え、ビアホール41を形成する側壁は、第2の層間絶縁膜40の上面から下面に向かって、基板面に平行な方向の断面積が徐々に減少する順テーパ状を有し、ビアホールの上端部から所定の深さまでの側壁に、第2の層間絶縁膜40とは異なる絶縁性材料からなるスペーサ膜42が埋め込まれている。

(もっと読む)

半導体装置、半導体装置の製造方法及びパワーアンプ素子

【課題】ウェハー上面側から基板までの電流経路を低抵抗にできる半導体装置およびその製造方法を提供する。

【解決手段】第一導電型高濃度半導体基板101と、第一導電型高濃度半導体基板101上に設けられた低濃度不純物エピタキシャル層103と、105とを含み、第一導電型高濃度半導体基板101に接続するトレンチ110が低濃度不純物エピタキシャル層103、105に設けられている半導体装置であって、トレンチ110の内壁に沿って少なくとも低濃度不純物エピタキシャル層103、105中に形成されるとともに、第一導電型高濃度半導体基板101に接続する、第一導電型高濃度半導体基板101と同一導電型の第一導電型高濃度不純物領域112と、第一導電型高濃度不純物領域112上に形成されたコンタクト111とを含む、半導体装置を提供する。

(もっと読む)

薄膜トランジスタ基板および表示デバイス

【課題】ソース電極とドレイン電極のドライエッチングレートの低下や、エッチング残さを引き起こすことがなく、半導体層と、ソース電極やドレイン電極といった配線金属の間からバリアメタルを省略することができる薄膜トランジスタ基板および表示デバイスを提供する課題とする。

【解決手段】半導体層1、ソース電極2、ドレイン電極3、透明導電膜4を有する薄膜トランジスタ基板において、ソース電極2とドレイン電極3は、ドライエッチング法によるパターニングで形成されたSiおよび/またはGe:0.1〜1.5 原子%、Niおよび/またはCo:0.1〜3.0原子%、Laおよび/またはNd:0.1〜0.5 原子%を含有するAl合金薄膜より成り、半導体層1と直接接続している。

(もっと読む)

半導体装置及びその製造方法

【課題】ソースドレイン領域のサイズが増大することがない局所配線構造を備えた半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成されたゲート電極22及び半導体基板11におけるゲート電極22の両側方にそれぞれ形成された第1のソースドレイン領域29A及び第2のソースドレイン領域29Bを有するトランジスタ12と、半導体基板11の上における第1のソースドレイン領域29Aを挟んでゲート電極22と反対側に形成されたゲート配線42と、ゲート配線42と第1のソースドレイン領域29Aとを接続する局所配線構造60とを備えている。局所配線構造60は、第1のソースドレイン領域29A及びゲート配線42の上面に跨って形成されたSiGe層61によって構成されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】製造コストを抑えつつ、ソース又はドレインと基板との間に生じる接合容量を低減できるようにした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】シリコン基板1にMOSトランジスタを形成する半導体装置の製造方法であって、シリコン基板1に素子分離膜3を形成する工程と、シリコン基板1上にゲート絶縁膜5を介してゲート電極7を形成する工程と、ゲート電極7と離間して、シリコン基板1上から素子分離膜3上にかけて引出電極9を形成する工程と、ゲート電極7と引出電極9とにより平面視で挟まれた領域のシリコン基板1に不純物を導入してS/D層11を形成する工程と、S/D層11上から引出電極9の少なくとも側面にかけてシリサイド23を形成する工程と、を含む。

(もっと読む)

薄膜抵抗体及びその製造方法

【課題】薄膜抵抗層を損傷することなく形成して、抵抗値の制御性を向上するとともに、微細化にも有利な薄膜抵抗体の製造方法を提供する。

【課題の解決手段】半導体基板1上に設けた絶縁層2上に薄膜抵抗層3のパターンを形成する工程と、レジストのパターンを用いて薄膜抵抗層3の配線接続領域に金属層6を形成する工程と、レジストを除去した後に金属層6を含む薄膜抵抗層3全体を覆うように層間絶縁膜7を形成する工程と、層間絶縁膜7に金属層6に達する開口部(コンタクトホール)10を形成する工程と、少なくとも開口部(コンタクトホール)10を含む領域に金属層6と接続される配線層12を形成する工程とを、順次施す。

(もっと読む)

半導体素子のコンタクトプラグ形成方法

【課題】セル領域及び周辺回路領域のコンタクトプラグ形成工程の単純化及びコスト削減をする方法を提供する。

【解決手段】セル領域A及び周辺回路領域Bが定義され、上記周辺回路領域Bに第1のコンタクトプラグ110が形成された半導体基板100上に第1の絶縁膜108を形成する段階と、上記第1の絶縁膜をエッチングして上記セル領域Aには接合領域104が露出され、上記周辺回路領域Bでは上記第1のコンタクトプラグが露出される第2のコンタクトホールを形成する段階と、上記第2のコンタクトホール内に第2のコンタクトプラグ116を形成する段階と、上記周辺回路領域Bの上記第2のコンタクトホール内に形成された上記第2のコンタクトプラグを除去する段階と、上記第2のコンタクトホール側壁にスペーサ120を形成する段階と、上記第2のコンタクトホール内に第3のコンタクトプラグ124を形成する段階を含む。

(もっと読む)

半導体素子の製造方法

【課題】コンタクトホールにおける断線や電流リークがなく、また、絶縁層上に形成された配線パターン同士の残渣による短絡なく、穴径に対する穴深さの比率が例えば2.4以上の高アスペクト比を有する低い導通抵抗のコンタクトホールを形成可能な、半導体素子の製造方法を提供する。

【解決手段】半導体基板1上に第1絶縁層3を形成し、この第1絶縁層を貫通して半導体基板を露出させる第1穴部3aを形成し、第1絶縁層上にAlまたはAl合金からなる導電膜8を成膜し、この導電膜を加熱して流動化させ冷却した後にパターン化して中継電極10を形成し、第1絶縁層上に中継電極を覆う第2絶縁層12を形成し、この第2絶縁層を貫通して中継電極を露出させる第2穴部12aを形成し、第2絶縁層上に第2穴部を介して中継電極と電気的に接続する配線パターンを形成する。

(もっと読む)

層間導電性コンタクトを含む半導体素子及びその形成方法

【課題】半導体素子及びその形成方法を提供する。

【解決手段】半導体素子は、半導体素子の下部コンタクト領域(underlying contact region)上に配置され、上部面を有する第1層間絶縁膜と、前記第1層間絶縁膜を貫通する第1開口部110a、110b内に配置され、第1幅W1aの上部を有する第1導電パターン113a、113bと、第1導電パターン113a、113bの上部面と接触され、第1幅W1aより狭い第2幅W2aの下部を有する第2導電パターン125a、125bと、を含み、第1導電パターン113a、113bの上部面は、前記第1層間絶縁膜の上部面に対して相対的にリセスされて、第1導電パターン113a、113bの上部面の前記下部コンタクト領域に相対的な高さは、前記第1層間絶縁膜の上部面の前記下部コンタクト領域に相対的な高さより低い。第2導電パターン125a、125bが第1導電パターン113a、113bの上部面と接続される。第2導電パターンの下部は、第1幅より狭い第2幅を有する。

(もっと読む)

超高密度のキャパシタ及び基板貫通ビアを有する集積基板

システム・イン・パッケージ用の集積基板は、基板貫通ビア及びトレンチキャパシタを備え、少なくとも4つの導電性のキャパシタ電極層を誘電層との交互の配列で含むトレンチ充填物を有する。キャパシタ電極層は、第1又は第2の基板側に設けた2つのキャパシタ端子のそれぞれの1つに、交互に接続される。トレンチキャパシタ及び基板貫通ビアは、半導体基板中に10μmを越える同等の横方向の延びを有するトレンチ開口及びビア開口内にそれぞれ形成される。この構造によれば、基板中にビア開口及びトレンチ開口を同時に製造することができるので、他の利点の中でも特に、集積基板をコスト効率よく製造することができる。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の配線または電極形成方法

【課題】 高温環境下で作動する半導体装置に好適な電極または配線形成方法及びこれらを備えた半導体装置を実現する。

【解決手段】 半導体基板10の基板面10a上に、下層配線11を覆って層間絶縁膜12を形成し、層間絶縁膜12に配線溝13を形成する。次に、スパッタ法、CVD法などにより、層間絶縁膜12の表面、配線溝13の内壁及び下層配線11を覆う金属膜14を形成する。続いて、酸素プラズマによる酸化処理を行い、金属膜14を酸化してバリア層15を形成する。これにより、200℃を超える高温使用環境においても化学的に安定であり、バリア層として効果的に作用するバリア層15をCu配線18と層間絶縁膜12との間に介在させることができるので、配線材料たるCuの層間絶縁膜12への拡散を防止することができる。

(もっと読む)

1 - 20 / 42

[ Back to top ]